1. 背景

- 会不会写makefile,从⼀个侧⾯说明了⼀个⼈是否具备完成⼤型⼯程的能⼒

- ⼀个⼯程中的源⽂件不计数,其按类型、功能、模块分别放在若⼲个⽬录中,makefile定义了⼀系列的规则来指定,哪些⽂件需要先编译,哪些⽂件需要后编译,哪些⽂件需要重新编译,甚⾄于进⾏更复杂的功能操作

- makefile带来的好处就是⸺⸺“⾃动化编译”,⼀旦写好,只需要⼀个make命令,整个⼯程完全⾃动编译,极⼤的提⾼了软件开发的效率。

- make是⼀个命令⼯具,是⼀个解释makefile中指令的命令⼯具,⼀般来说,⼤多数的IDE都有这个命令,⽐如:Delphi的make,Visual C++的nmake,Linux下GNU的make。可⻅,makefile都成为了⼀种在⼯程⽅⾯的编译⽅法。

- make是⼀条命令,makefile是⼀个⽂件,两个搭配使⽤,完成项⽬⾃动化构建。

2. 基本使用

实例代码:

#include <stdio.h>

int main()

{

printf("hello Makefile!\n");

return 0;

}

Makefile文件

myproc:myproc.c

gcc -o myproc myproc.c

.PHONY:clean

clean:

rm -f myproc

解释一下:

依赖关系:上⾯的⽂件myproc,它依赖myproc.c

依赖方法:gcc -o myproc myproc.c ,就是与之对应的依赖关系

项目清理:

- ⼯程是需要被清理的

- 像clean这种,没有被第⼀个⽬标⽂件直接或间接关联,那么它后⾯所定义的命令将不会被⾃动执⾏,不过,我们可以显⽰要make执⾏。即命令⸺⸺“make clean”,以此来清除所有的⽬标⽂件,以便重编译。

伪目标文件总是被执行的。

什么叫做总是被执⾏?

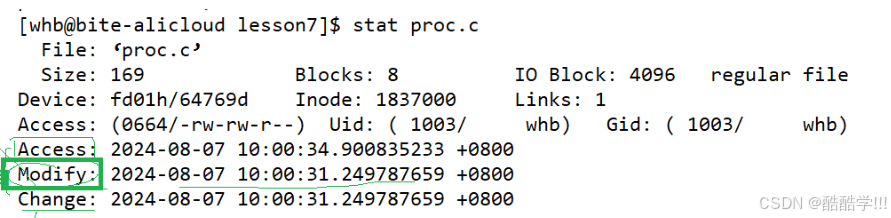

查看状态, 我们可以看到以下三个时间。

文件 = 内容 + 属性

以下简称acm时间, a表示最近一次访问的时间, M表示内容最近被修改的时间, C表示最近一个属性被修改的时间。

例如 :

cat proc.c就是访问文件(但是访问频繁影响效率, 现在的操作系统已经这一块已经发生了变化。)

chmod o-r proc.c 就是改变属性

vim proc.c 就是修改内容

但是内容被修改可能发生属性的联动, 因为文件的大小变了。

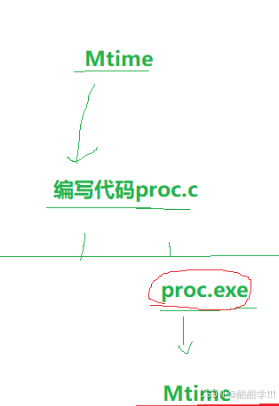

不管是源文件, 还是可执行程序, 都是文件, 程序可不可总是被执行就是看mtime的时间, 如果没有修改proc.c的m时间,只修改了proc.exe的时间, 那么表示exe比.c更新,编译器就认为没有必要再重新编译了, 相反如果.c的mtime时间更新,那么就可以重新编译生成新的可执行程序。

拓展, touch不仅可以创建文件, 还可以用来修改文件的时间(mtime和ctime都会被修改)。

结论: .PHONY:让make忽略源⽂件和可执⾏⽬标⽂件的M时间对⽐

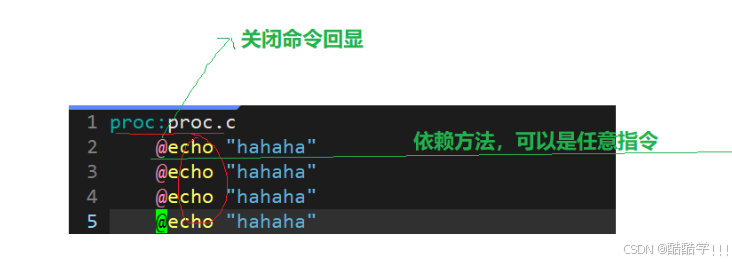

执行make, 默认在命令行打印四条“hahaha”, 如果加上@则不会执行,关闭命令回显。

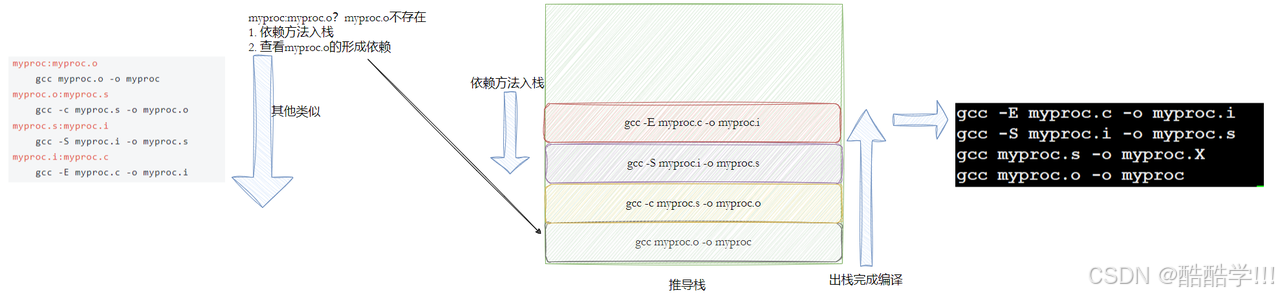

3. 推导过程

myproc:myproc.o

gcc myproc.o -o myproc

myproc.o:myproc.s

gcc -c myproc.s -o myproc.o

myproc.s:myproc.i

gcc -S myproc.i -o myproc.s

myproc.i:myproc.c

gcc -E myproc.c -o myproc.i

.PHONY:clean

clean:

rm -f *.i *.s *.o myproc

编译

$ make

gcc -E myproc.c -o myproc.i

gcc -S myproc.i -o myproc.s

gcc -c myproc.s -o myproc.o

gcc myproc.o -o myproc

make是如何⼯作的,在默认的⽅式下,也就是我们只输⼊make命令。那么:

- make会在当前⽬录下找名字叫“Makefile”或“makefile”的⽂件。

- 如果找到,它会找⽂件中的第⼀个⽬标⽂件(target),在上⾯的例⼦中,他会找到 myproc 这个⽂件,并把这个⽂件作为最终的⽬标⽂件。

- 如果 myproc ⽂件不存在,或是 myproc 所依赖的后⾯的 myproc.o ⽂件的⽂件修改时间要⽐ myproc 这个⽂件新(可以⽤ touch 试),那么,他就会执⾏后⾯所定义的命令来⽣成myproc 这个⽂件。

- 如果 myproc 所依赖的 myproc.o ⽂件不存在,那么 make 会在当前⽂件中找⽬标为myproc.o ⽂件的依赖性,如果找到则再根据那⼀个规则⽣成 myproc.o ⽂件。(这有点像⼀个堆栈的过程)

- 当然,你的C⽂件和H⽂件是存在的啦,于是 make 会⽣myproc.o ⽂件,然后再⽤myproc.o ⽂件声明 make 的终极任务,也就是执⾏⽂件 hello 了。

- 这就是整个make的依赖性,make会⼀层⼜⼀层地去找⽂件的依赖关系,直到最终编译出第⼀个⽬标⽂件。

- 在找寻的过程中,如果出现错误,⽐如最后被依赖的⽂件找不到,那么make就会直接退出,并报错,⽽对于所定义的命令的错误,或是编译不成功,make根本不理。

- make只管⽂件的依赖性,即,如果在我找了依赖关系之后,冒号后⾯的⽂件还是不在,那么对不起,我就不⼯作啦。

4. 好用的操作

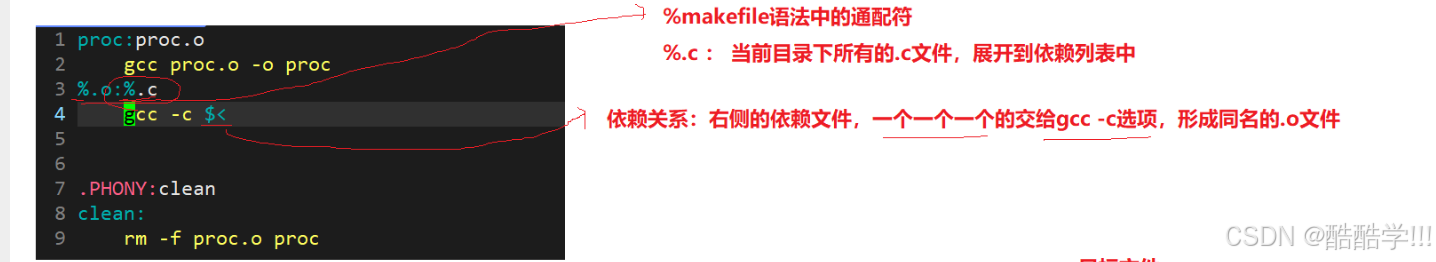

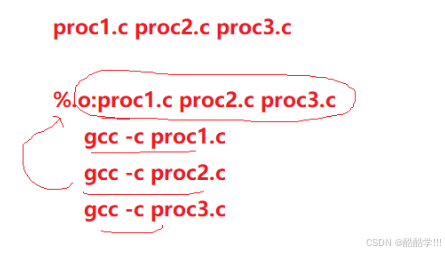

% 是makefile中的通配符

例如: %.c: 当前目录下所有.c文件, 展开到依赖项中。

依赖关系:右侧的依赖文件, 一个一个的交给gcc -c选项, 形成同名的.o文件。

继续

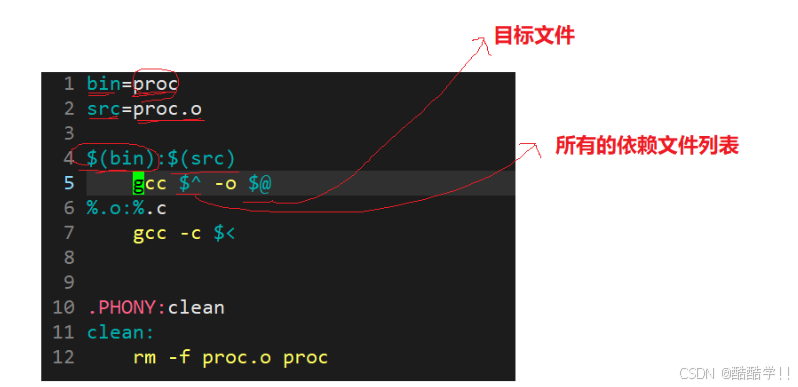

$@表示目标文件, $^表示所有依赖文件的文件列表

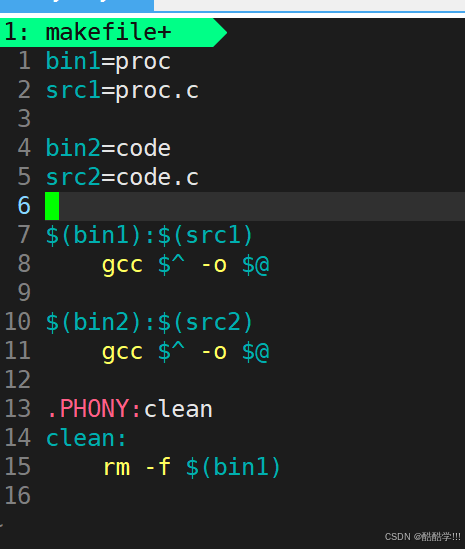

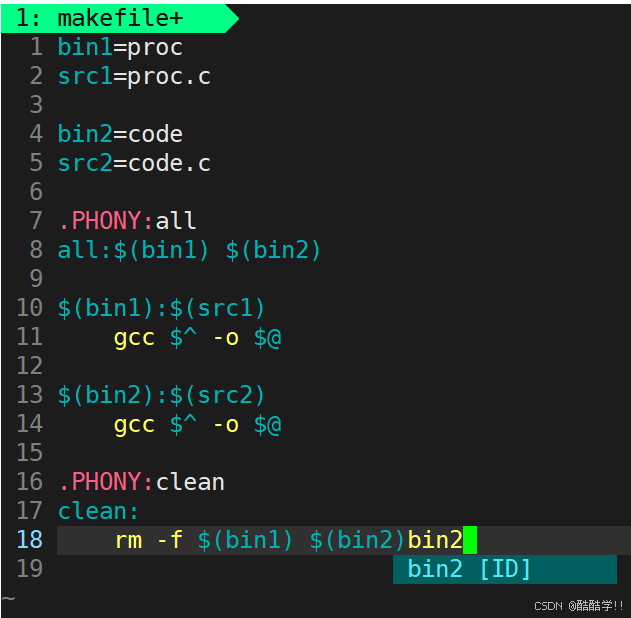

默认情况下, makefile执行到了一个目标文件之后就会停下来, 比如下图, 只会生成一个proc文件。

如果想进行多个文件同时编译,则可以添加目标all,但是不给执行方法, 为了形成目标all,makefile就会像下面搜索依赖项,形成proc和code。

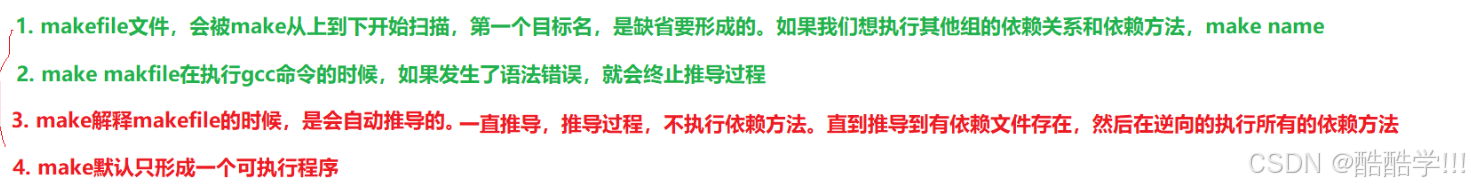

小结一下:

5. 拓展语法

BIN=proc.exe # 定义变量

CC=gcc

#SRC=$(shell ls *.c) # 采⽤shell命令⾏⽅式,获取当前所有.c⽂件名

SRC=$(wildcard *.c) # 或者使⽤ wildcard 函数,获取当前所有.c⽂件名

OBJ=$(SRC:.c=.o) # 将SRC的所有同名.c 替换 成为.o 形成⽬标⽂件列表

LFLAGS=-o # 链接选项

FLAGS=-c # 编译选项

RM=rm -f # 引⼊命令

$(BIN):$(OBJ)

@$(CC) $(LFLAGS) $@ $^ # $@:代表⽬标⽂件名。 $^: 代表依赖⽂件列表

@echo "linking ... $^ to $@"

%.o:%.c # %.c 展开当前⽬录下所有的.c。 %.o: 同时展开同

名.o

@$(CC) $(FLAGS) $< # %<: 对展开的依赖.c⽂件,⼀个⼀个的交给gcc。

@echo "compling ... $< to $@" # @:不回显命令

.PHONY:clean

clean:

$(RM) $(OBJ) $(BIN) # $(RM): 替换,⽤变量内容替换它

.PHONY:test

test:

@echo $(SRC)

@echo $(OBJ)

完