考点19 ARM处理器中的MMU和MPU

1.MMU(存储器管理单元)

- .ARM处理器中的MMU是许多高性能处理器所必需的重要部件之一。虚拟存储器技术,借助MMU能把系统中的不同类型存储器(Flash、SRAM、SDRAM、ROM、优盘等)进行统一管理,通过地址映射,使需要运行在连续地址空间的软件,可运行在不连续物理存储器中,需要较大的存储空间的软件可以运行在较小容量的物理存储器中。

- .MMU功能:

- 实现虚拟地址到物理地址的映射。ARM中MMU功能可以被“禁止”或“使能”。当“使能”MMU时,ARM处理器产生的地址是虚拟地址。MMU的功能就是虚拟地址到物理地址的转换,需要通过查找页表来完成。页表是一张虚拟地址与物理地址的对应表,存储在内存储器中。

- 实现存储器访问权限的控制。存储器访问权限可以块(页)为单位进行设置,分为不可访问,只读、可读/写等不同的权限。当访问具有不可访问权限的页时,会产生一个存储器异常的信号,通知ARM处理器。

3. .存储器访问的顺序:

当执行加载/存储指令,要访问存储器时,MMU要先查找TLB中的转换表。如果TLB中没有,则硬件自动查找主存储器内的页表,找到从虚拟地址到物理地址的转换信息和访问权限信息,就可以用来进行存储器的读/写操作,同时把这些信息放入TLB中供此后继续使用。如果页表中也找不到转换信息,就产生中断,通知操作系统OS进行处理。

2.MPU(存储器保护单元)

- 存储器保护单元是对存储器进行保护的可选组件,它提供了简单替代MMU的方法来管理存储器,没有MMU就不需要进行复杂的地址转换操作。

- MPU允许ARM处理器的4 GB空地址空间定义8对域,分别控制8个指令和8个数据内存区域。每个域的首地址和界(或长度)均可编程。域和域可以重叠,并且可以设置不同的优先级。

考点20 ARM指令分类及指令格式

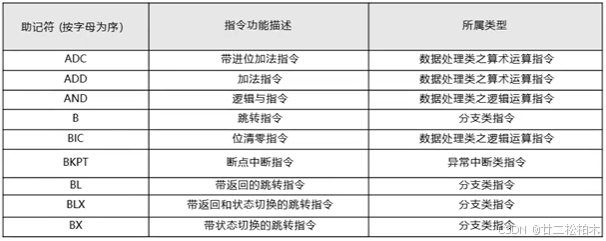

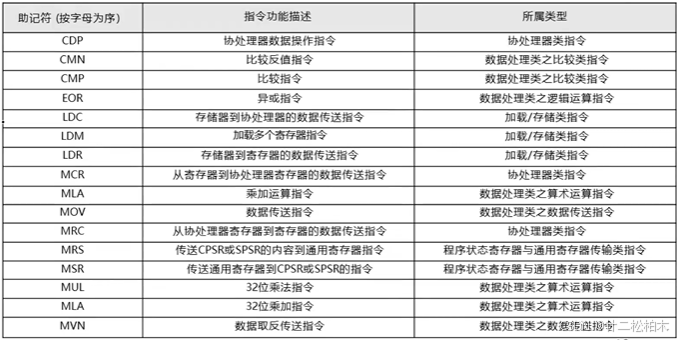

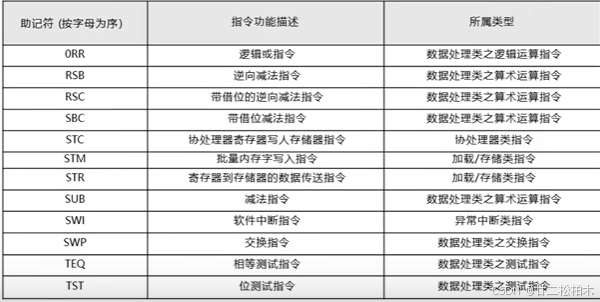

1.ARM微处理器的指令集可以分为分支指令、数据处理指令、程序状态寄存器(CPSR)处理指令、加载/存储指令、协处理器指令和异常产生指令六大类。

2.ARM指令格式

- 一般格式:<opcode>{<cond>}{S} <Rd>,<Rn>{,<op2>}

- <>不可省略,{}可省略,opcode、cond与S之间没有分隔符,{S}与Rd之间用空格隔开。

- 格式具体项目如下表:

3.指令的条件域

- 当处理器工作在ARM状态下,几乎所有的指令均根据CPSR中条件码的状态和指令的条件域有条件的执行。当指令的执行满足条件时,指令被执行,否则被忽略。

- 每一条arm指令包含4位的条件码,位于指令的最高4位【31:28】。条件码共有16种,每种条件码各用两个字符表示。这两个字符可以添加在指令助记符的后面与指令同时使用。

- 具体条件码如下:

4.ARM指令中操作数符号

- # 是立即数符号,表示立即数,其后用十进制或16进制数。

- 0x 是16进制符号,后面数据是16进制数。

- ! 为更新基址寄存器符号,表示指令在完成操作后,最后的地址应该写入基址寄存器。

- ^ 为复制SPSR到CPSR符号。用于批量数据存储指令存放在寄存器之后作为后缀,当其前面的寄存器不包含PC时,该符号所用的寄存器是用户模式的寄存器;当其前面的计算器包含PC时,该符号指令将SPSR计算器的值复制的CPSR中。

- - 是寄存器系列表范围符号,如R7-R0。

5.ARM指令的移位操作

- 移位操作包含如下六种类型:LSL逻辑左移、ASL算数左移、LSR逻辑右移、ASR算术右移、ROR循环右移、RRX带扩展的循环右移。

- 通用格式为:Rm,<opsh>#<shift>

- 其中,Rm为要移位的通用寄存器,<opsh>为移位操作符,即上述六种,<shift>为移位次数(0-31)。