#C0308

沧海茫茫千钟粟,且拾吾昧一微尘

——《沧海拾昧集》@CuPhoenix

【阅前敬告】

沧海拾昧集仅做个人学习笔记之用,所述内容不专业不严谨不成体系

如有问题定为本集记录有谬,切勿深究

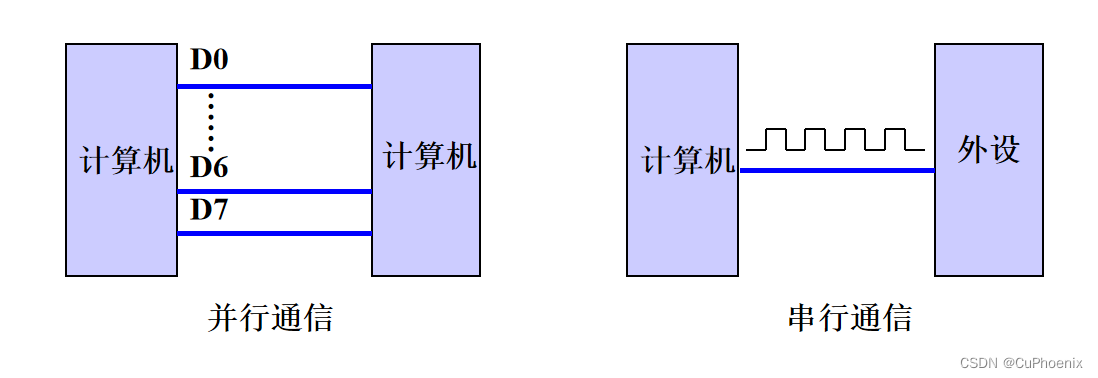

引子:串行通信技术

1、串行通信的优势

| 优点 | 缺点 |

|---|---|

| 通信线路简单,适于远距离传输 抗干扰能力强,通信费用低 传输线既传数据,又传联络信号 | 传输速度慢 需要串并转换 对数据格式有要求 |

2、异步通信协议

- 串行通信时的数据、控制和状态信息都使用同一根信号线传送。

- 收发双方必须遵守共同的通信协议(通信规程),才能解决传送速率、信息格式、位同步、字符同步、数据校验等问题。

- 串行异步通信以字符为单位进行传输,其通信协议是起止式异步通信协议。

| 起始位 | 数据位 | 校验位 | 停止位 | ||

|---|---|---|---|---|---|

| 0 | 0/1 | ··· | 0/1 | 0/1 | 1 |

- 起始位:字符开始传送的标志,采用逻辑0电平;

- 数据位:数据位紧跟着起始位传送。由5~8个二进制位组成,低位先传送;

- 校验位:用于校验是否传送正确;可选择奇检验、偶校验或不传送校验位;

- 停止位:表示该字符传送结束。停止位采用逻辑1电平,可选择1、1.5或2位;

- 空闲位:不传输信息时,为逻辑1电平;

3、波特率

每秒钟传送的二进制数据位数称为波特率,单位为波特(bps)。在串行通信中,利用波特率来表示数据传送的速率。 异步串行传送常用的波特率为110,300,600,1200,2400,4800,9600,19200,28800,36400,57600波特。同步传送的波特率高于异步传送的波特率。

4、异步通信方式

异步通信要求在发送每一个字符时都要在数据位的前面加上1位起始位,在数据位后面要有1位或1.5位或2位的停止位。在数据位和停止位之间可以有1位校验位,数据位可以为5-8位长。字符之间允许有不定长度的空闲位。

传送开始后,接收设备不断地检测传输线,当在测到一系列的“1”之后检测到一个“0”,就确认一个字符开始,于是以位时间(1/波特率)为间隔移位接收规定的数据位和奇偶校验位,拼装成一个字符的并行字节。这之后应接收所规定位长的停止位“1”,若没有收到即为“帧出错”。

只有既无帧出错又无奇偶错才算正确地接收到一个字符。一个字符接收完毕,接收设备又继续测试传输线,监视“0”电平的到来和下一字符的开始。

示例:设数据传送的速率为120字符/秒,每个字符8个数据位,采用1位停止位,无校验

传送的波特率为:10 × 120 = 1200 bps

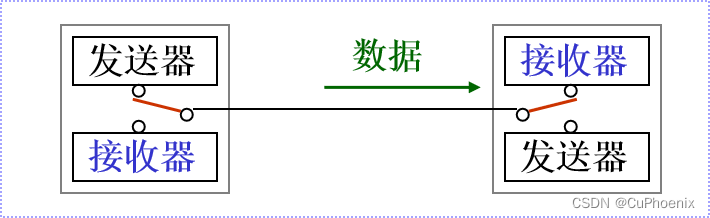

5、数据传送方式

| 单工方式 | |

|---|---|

| 半双工方式 |  |

| 半双工方式 |  |

6、信号传输方式

- 基带传输方式:在传输线路上直接传输不加调制的二进制信号。它要求传送线的频带较宽,传输的数字信号是矩形波。由于线路中存在着电感、电容及漏电感、漏电容等分布参数,矩形波通过传输线后会发生畸变、衰减和延迟而导致传输的错误。信号的频率越高、传输的距离越远这种现象则越严重,因此基带传输方式仅适宜于近距离和速度较低的通信。

- 频带传输方式:频带传输方式又称为载波传输方式。在远距离通信时,通常是利用电话线传输的。电话线的频带在300HZ-3400HZ之间,由于频带不宽,用它来直接传输数字信号时,就会出现畸变失真,但用它来传送一个频率为1000Hz-2000Hz的模拟信号时,则失真较小。

一、串行接口标准

串行接口标准指的是计算机或终端(数据终端设备DTE)的串行接口电路与调制解调器MODEM等(数据通信设备DCE)之间的连接标准。在计算机网络中,由它构成网络的物理层协议。

常用标准:RS-232C接口、RS-422A接口、RS-485接口、USB接口

1、RS-232C标准

- 设计目的:连接调制解调器;

- 功能:可实现远距离通信,也可近距离连接两台微机;

- 所在层次:物理层。

- 接口电平:EIA电平(逻辑1为 -3V ~ -15V,逻辑0为 +3V ~ +15V)

2、RS-232C引脚定义

- 完全版标准:使用25针连接器(DB25);

- 一般设备:只用其中9个信号,使用9针连接器(DB9)即可;

- 信道:两个信道,一主一次(次信道为辅助串行通道提供数据控制和通道,传输速率比主信道低得多);

| 引脚缩写 | 引脚名称 | 功能 |

|---|---|---|

| TxD | 发送数据 | 串行数据的发送端 |

| RxD | 接收数据 | 串行数据的接收端 |

| TxC | 发送器时钟 | 控制数据终端发送串行数据的时钟信号 |

| RxC | 接收器时钟 | 控制数据终端接收串行数据的时钟信号 |

| RTS | 请求发送 | 数据终端设备准备好送出数据,发出有效的RTS信号 用于通知数据通信设备准备接收数据 |

| CTS | 清除发送(允许发送) | 数据通信设备准备好接收数据终端设备的传送数据时 发出CTS有效信号来响应RTS信号 |

| DTR | 数据终端准备好 | 当数据终端设备一加电,该信号就有效 表明数据终端设备准备就绪 |

| DSR | 数据装置准备好 | 表示数据通信设备已接通电源连到通信线路上 处在数据传输方式 |

| GND | 信号地 | 为所有的信号提供一个公共的参考电平 |

| CD | 载波检测 | 本地调制解调器接收到来自对方的载波信号时 该引脚向数据终端设备提供有效信号 |

| RI | 振铃指示 | 调制解调器接收到对方的拨号信号期间 该引脚信号作为电话铃响的指示、保持有效 |

3、RS-232C的连接

- 远距离通信:利用232C接口连接调制解调器,调制解调器连接电话线路进行通信;

- 短距离通信:不使用调制解调器,直接连接,又称零调制解调器连接;通信时RTS和CTS各自互接,DTR和DSR各自互接,表明请求传送总是允许、数据装置总准备好。(如果互接通信比较可靠,但不经济)

二、Inter 8251A芯片

1、8251A的基本功能

- 可以选择工作方式。同步方式波特率为0~64K,异步方式波特率为0~19.2K。

- 在同步方式下,每个字符可以用5 ~ 8位来表示,并且内部能自动检测同步字符,从而实现同步。除此之外,8251A也允许同步方式下增加奇/偶校验位进行校验。

- 在异步方式下,每个字符可以用5 ~ 8位来表示,时钟频率为传输波特率的1、16或64倍,用1位作为奇/偶校验。此外,8251A在异步方式下能自动为每个数据增加1个启动位,并能根据编程为每个数据增加1个、1.5个或2个停止位。同时,可以检查假启动位,自动检测和处理终止字符。

- 全双工的工作方式,其内部提供具有双缓冲器的发送器和接收器。

- 提供出错检测,具有奇偶、溢出和帧错误等校验电路。

2、8251A的内部结构

- 发送器

由发送缓冲器和发送控制电路两部分组成。

当发送器中发送缓冲器已空(即可接收数据),由发送控制电路向CPU发出TxRDY有效信号,如果CPU与8251A之间采用中断方式交换信息,那么TxRDY可作为向CPU发出的中断请求信号。此时,CPU可向8251A输出数据。CPU送出的数据经数据总线缓冲器并行输入锁存到发送缓冲器中。

采用异步方式传输,则由发送控制电路在其首尾加上起始位和停止位,经移位寄存器从数据输出线TxD逐位串行输出,其发送速率取决于TxC端收到的发送时钟频率。

采用同步方式传输,则在发送数据之前,发送器将自动送出1~2个同步字符(对应内同步方式)或在收到有效的同步信号(对应外同步方式)后,才逐位串行输出数据。

当发送器中的数据发送完,由发送控制电路向CPU发出TxE有效信号,表示发送器中移位寄存器已空。因此,发送缓冲器和发送移位寄存器构成发送器的双缓冲结构。

- 接收器

接收器由接收缓冲器和接收控制电路组成。接收移位寄存器用来从RxD引脚上接收串行数据,按照相应格式转换成并行数据后存入接收缓冲器。而接收控制电路则配合接收缓冲器工作,管理有关接收的所有功能。

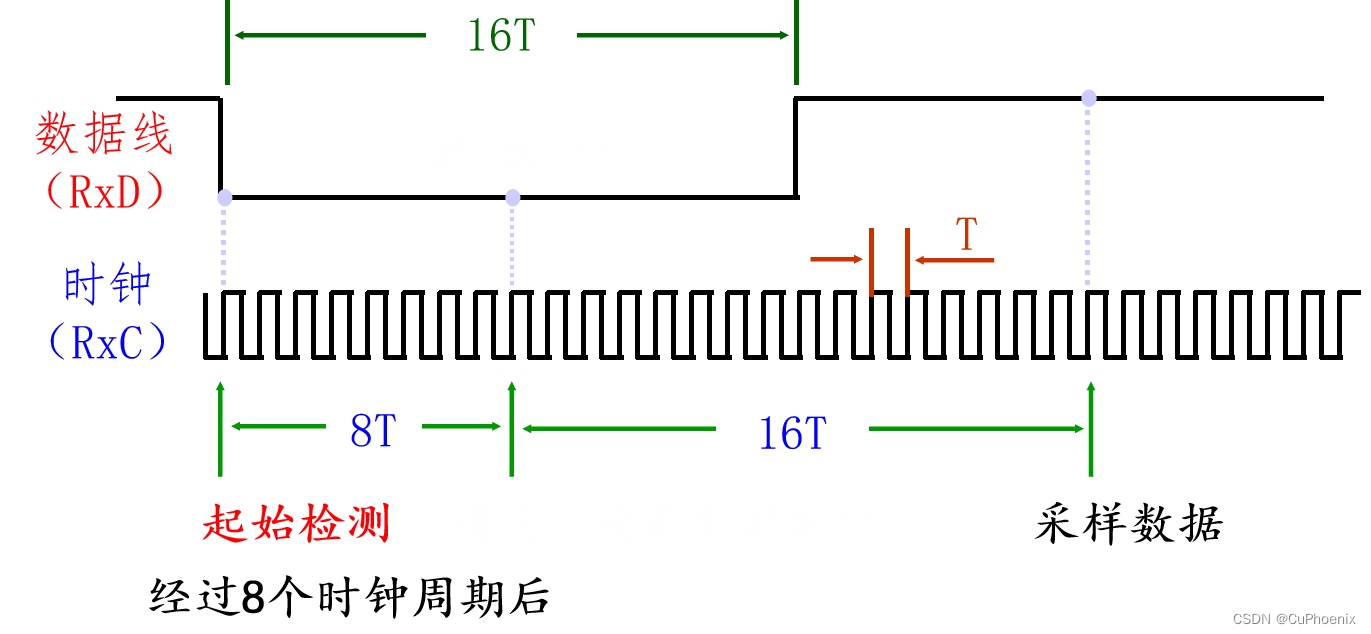

当8251A工作在异步方式并准备接收一个字符时:①在RxD线上检测低电平,将检测到的低电平作为起始位;②启动接收控制电路中的一个内部计数器进行计数,计数脉冲就是8251A的接收器时钟脉冲;③当计数进行到相应于半个数位传输时间(比如时钟脉冲为波特率的16倍,则计到第8个脉冲)时,再对RxD线进行检测,如果此时仍为低电平,则确认收到一个有效的起始位。

然后,8251A开始进行常规采样,数据进入接收移位寄存器完成字符装配,并进行奇偶校验,然后,送入接收缓冲器,同时向CPU发出RxRDY信号,表示已经收到一个可用的数据,通知CPU来取数。如果CPU与8251A之间采用中断方式交换信息,那么RxRDY可作为向CPU发出的中断请求信号。

- 数据总线缓冲器

数据总线缓冲器是8251A与CPU之间进行交换信息的必经之路,或者说它是CPU与8251A之间的数据接口。CPU从8251A读取的数据或状态信息,及写入的数据或控制字都经由数据总线缓冲器完成。

- 读/写控制电路

| CS* | C / D* | RD* | WR* | 相应的操作 |

|---|---|---|---|---|

| 0 | 0 | 0 | 1 | CPU从8251A输入数据 |

| 0 | 0 | 1 | 0 | CPU从8251A输出数据 |

| 0 | 1 | 0 | 1 | CPU读入8251A的状态 |

| 0 | 1 | 1 | 0 | CPU往8251A写入控制命令 |

- 调制解调控制电路

调制解调控制电路提供了一组通用的控制信号,用来完成8251A和调制解调器的连接。包括DTR*、DSR*、RTS*、CTS*。

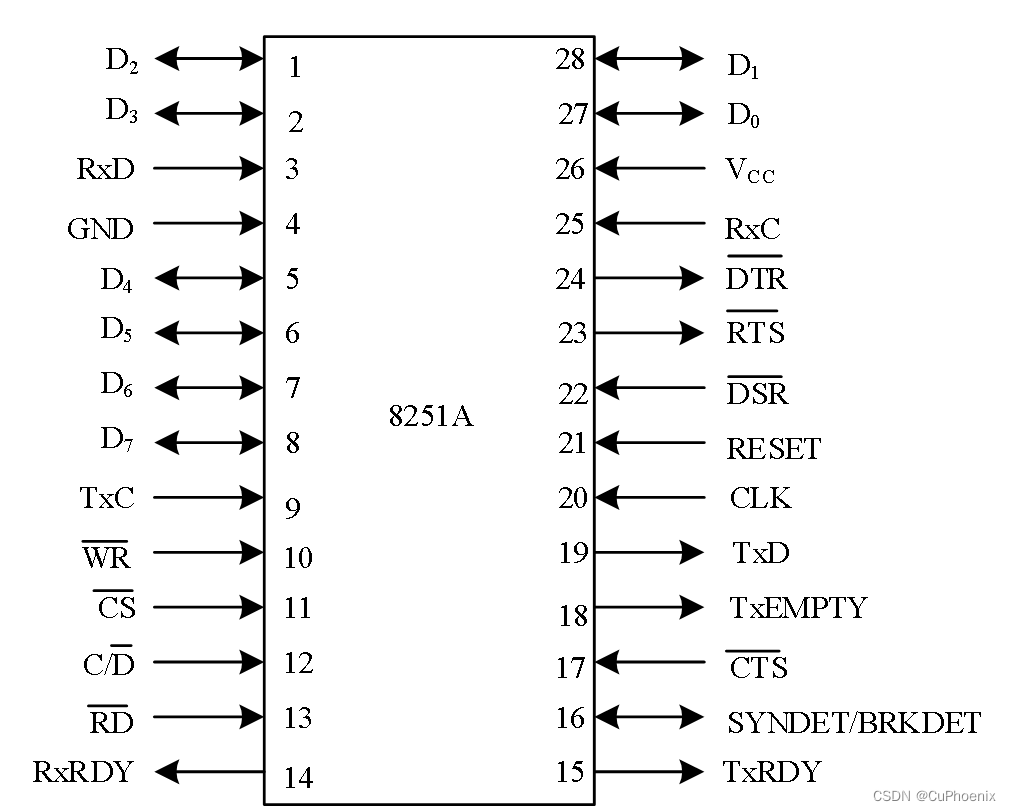

3、8251A的引脚

连接CPU:

- D7~D0:数据总线,用于连接CPU;

- WR*:输入,低电平有效,CPU输出数据时有效;

- RD*:输入,低电平有效,CPU输入数据时有效;

- C/D*:输入,数据/控制信息选择引脚,低电平时传输数据,高电平时传输控制信息;

- CS*:输入,低电平有效,有效时芯片才工作;

- TxRDY:发送器准备好信号,既可作为中断请求信号也可作为查询信号;

- TxE:发送器空信号;

- RxRDY:接收器准备好信号,既可作为中断请求信号也可作为查询信号;

- SYNDET:同步检测信号,只用于同步方式。外同步时是输入信号,内同步时是输出信号;

- RESET:复位信号输入,高电平有效

连接外设:

- RxD:接收数据引脚;

- TxD:发送数据引脚;

- DTR*:数据终端准备好信号,由825lA送往外设,低电平时有效。CPU可以通过控制命令使有效,从而通知外部设备,CPU当前已经准备就绪;

- DSR*:数据设备准备好信号,由外设送往8251A。该信号低电平时有效,用来表示当前外设已经准备好。当其出现低电平时,8251A状态寄存器的第7位自动置1,CPU可以通过读状态寄存器的操作,实现对该信号的检测。

- RTS*:请求发送信号 由8251A送往外设,低电平时有效,表示CPU已经做好发送准备。CPU可以通过编程命令使RTS变为有效电平;

- CTS*:允许发送信号 是对RTS的响应,由外设送往8251A。只有当 CTS为低电平时,8251A才能执行发送操作。

注:实际使用时,CTS*必须为低,其余三个联络信号可以悬空。

其他引脚:

- CLK:工作时钟输入,用来产生芯片的内部时序,要求CLK的频率

- 在同步方式下,大于TxC /RxC的30倍;

- 在异步方式下,大于TxC /RxC的4.5倍

- VCC:电源;

- GND:地;

- TxC:发送器时钟输入;

- RxC:接收器时钟输入;

注:在异步方式下,时钟频率可以为字符传输波特率的x1 / x16 / x64,决定于初始化编程指定的波特率因子。

三、Inter 8251A的初始化编程

1、方式选择控制字(模式字)

写入控制端口(奇地址),用来确定8251A的工作方式、数据格式、校验方法等。

2、操作命令控制字(控制字)

写入控制端口(奇地址),其作用是使8251A处于某种工作状态,以便接收或发送数据。

异步方式下通常写37H。

3、状态字

从奇地址端口读取。

4、初始化流程

- 芯片复位后,第一次往控制端口写入的是方式选择控制字(模式字);

- 如果在方式选择控制字中,规定8251A是同步工作方式,则接下来向控制端口写入1个或2个字节就是同步字符,同步字符被写入同步字符寄存器;

- 不管是在同步方式还是在异步方式下,接下来由CPU往控制端口写入的是操作命令控制字即控制字,如果规定是内部复位命令,则转去对芯片复位,重新初始化。否则,进入应用程序,通过数据端口传输数据。

敬谢诸君。

金陵钟山之阳。