文章目录

1. 概述

1.1 发展历程

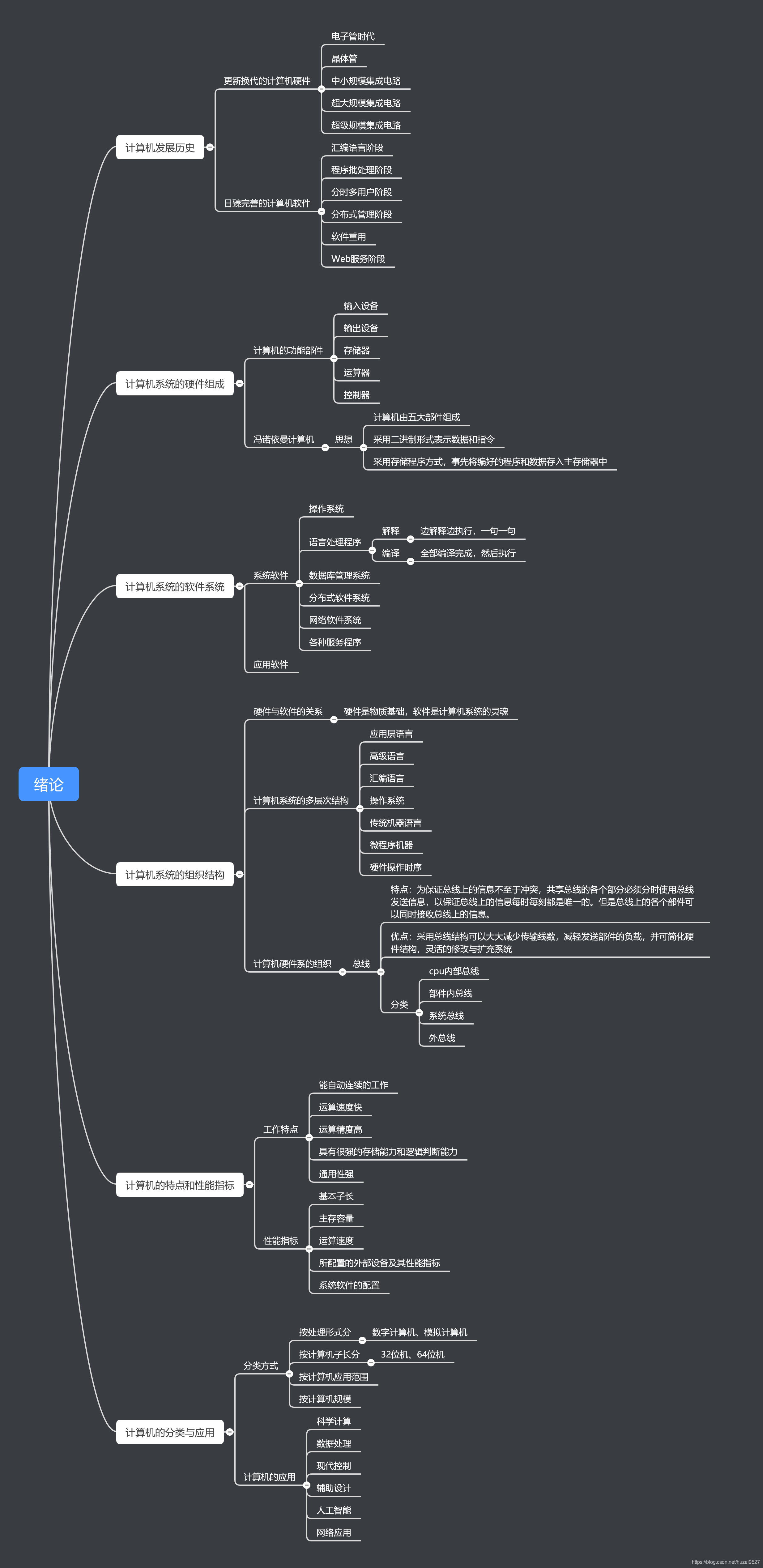

1.2 计算机系统层次结构

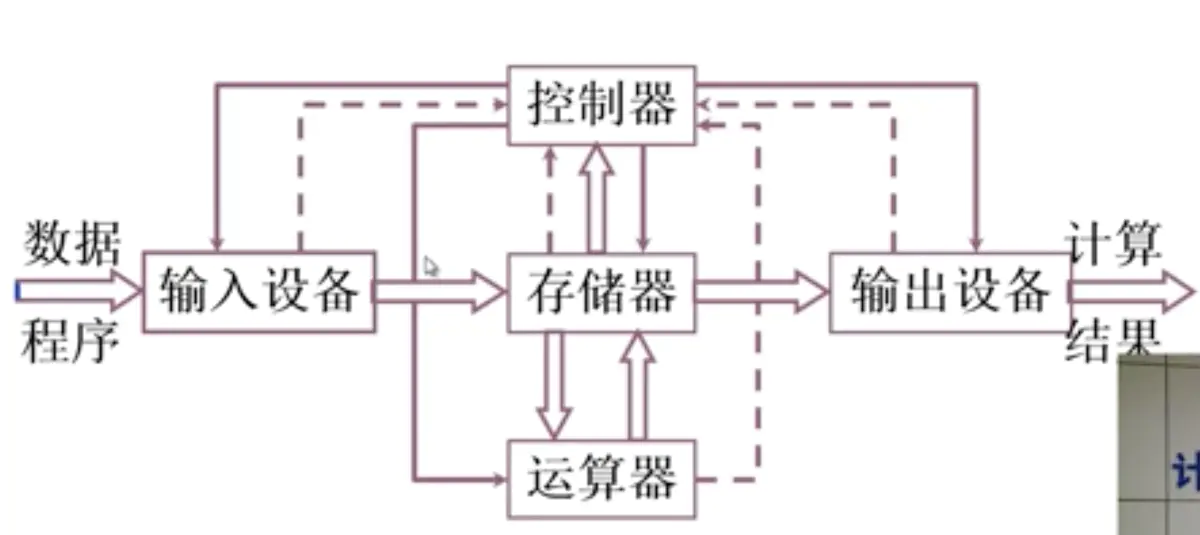

1.2.1 五大部件

1) 存储器

类比:

- 存储体 — 存储单元 — 存储原件(0/1)

- 大楼 — 房间 — 床位 (有人/没人)

重要概念:

- 存储单元 :存放一串二进制代码(可能是指令,也可能是数据)

- 存储字 : 存储单元中二进制代码的组合

- 存储字长:存储单元中二进制代码的位数(32位/64位)

每个存储单元赋予一个地址号,每个存储单元中存放一个存储字;存储单元按地址寻访

-

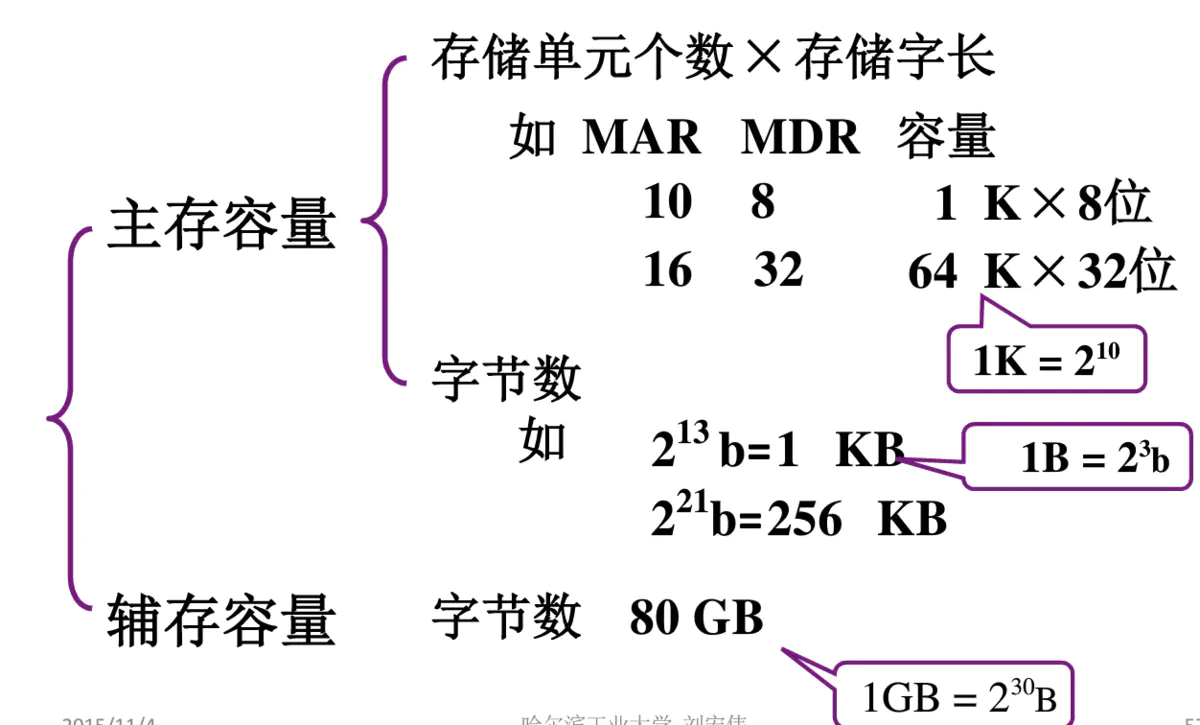

MAR(Memory Address Register)存储器地址寄存器:存地址的,反映存储单元的个数

-

MDR(Memory Data Regester)存储器数据寄存器:存数据的,反映存储字长

设MAR=4位 说明存储单元个数是2的4次方=16个(反映存储单元的个数);

MDR=8位,说明存储字长8位

解释:计算机中的主存数据寄存器(MDR),与主存地址寄存器(MAR)帮助完成CPU和主存储器之间的通信:

- MAR用来保存数据被传输到的位置的地址或者数据来源位置的地址;

- MDR保存要被写入地址单元或者从地址单元读出的数据。

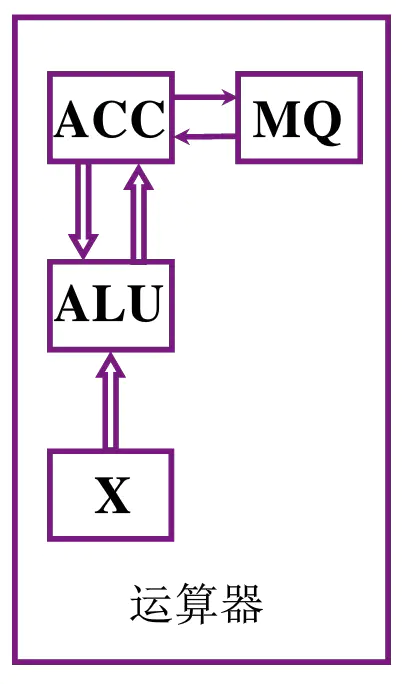

2) 运算器

运算器的功能是什么,如何工作?

- 加法运算

- 乘法运算

- 或与非

运算器结构:

- ALU(Arithmetic Logic Unit):算数逻辑单元,核心运算单元;通常是个组合电路,其特点是如果输入撤销,那么输出结果也会撤销,所以如果要保存结果需要在输入输出端加上相应的寄存器(ACC,X);

- ACC(Accumulator):累加器;

- X: 数据寄存器;

- MQ:乘商寄存器(在乘法过程中,产生的结果是操作数的两倍)为了把乘法结果都保存下来,需要此寄存乘法增加的部分;

| ACC | MQ | X | |

|---|---|---|---|

| 加法 | 被加数、和 | 加数 | |

| 减法 | 被减数、差 | 减数 | |

| 乘法 | 乘法结果的高位 | 乘数、乘法结果的低位 | 被乘数 |

| 除法 | 被除数、余数 | 商 | 除数 |

乘法:加法+移位操作 (这里有点不太清楚)

除法:减法+移位操作 (这里有点不太清楚)

(回去看看《编码》、《CSAPP》第二章理解理解,再回过来看看)

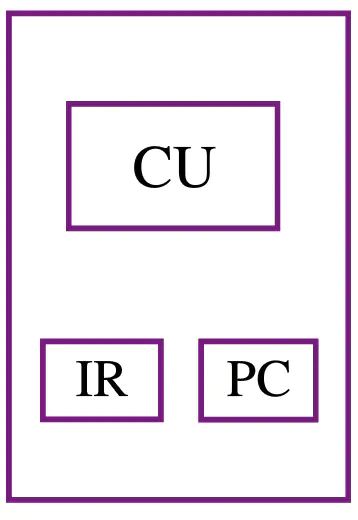

3) 控制器

功能:

- 解释指令

- 保证指令按顺序执行

基本结构:

完成一条指令:

- 取指令(PC)

- 分析指令(IR)

- 执行指令(CU)

结构:

- CU:核心控制单元,执行指令

- PC:程序计数器,用来存放当前要执行指令的地址,具有计数功能(PC) + 1 —> PC(不同的机型,这里不一定+1,即相邻两个指令的物理地址不一定相邻)

- IR:指令寄存器,存放当前欲执行的指令

4) 输入设备

5) 输出设备

1.2.2 指令完成

这里要好好理解每一个指令步骤,理解了每一个步骤就相当于理解了这一章。

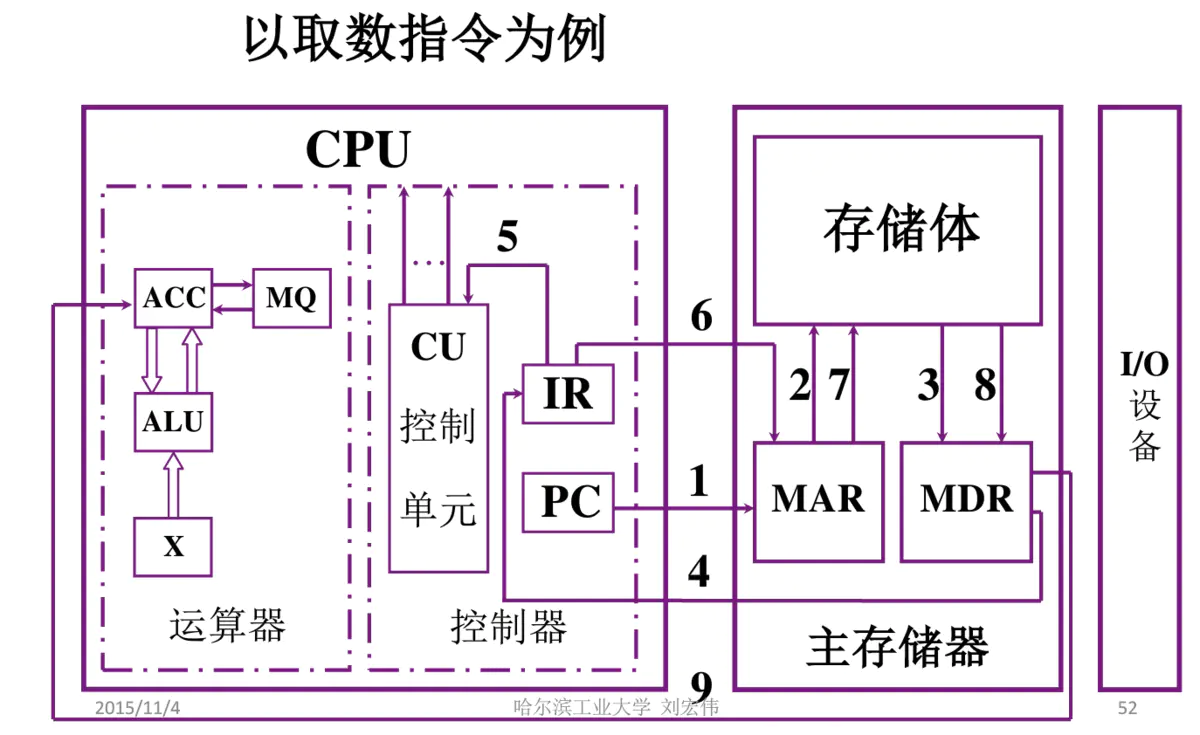

(1)主机完成一条取数指令的步骤

取数指令的功能:把存储体(主存/内存)中的数存到ACC中

完成一条指令的三个阶段:

- 取指令

- 分析指令

- 执行指令

(注:指令:操作码+地址码)

取数操作步骤分析(如图):

- 要执行的指令的地址保存在PC中,指令保存在存储体中;第一步将PC中要执行的指令的地址放入MAR;

- MAR将指令地址送给存储体M;

- 在控制器的控制下,存储体M将指令地址中的指令送给MDR;

- 在控制器的控制下,将MDR中的指令存到IR中;(到此,取指令的操作完成;PC—>MAR—>M—>MDR—>IR)

- 分析指令:将IR中指令的操作码部分给CU,由CU去分析控制执行;

- 把IR中指令中待取的数的地址部分送到MAR;

- MAR将数的地址送给存储体M;

- 在控制器的控制下,存储体M将数的地址中的数送给MDR;

- 在控制器的控制下,MDR中的数交给ACC保存。

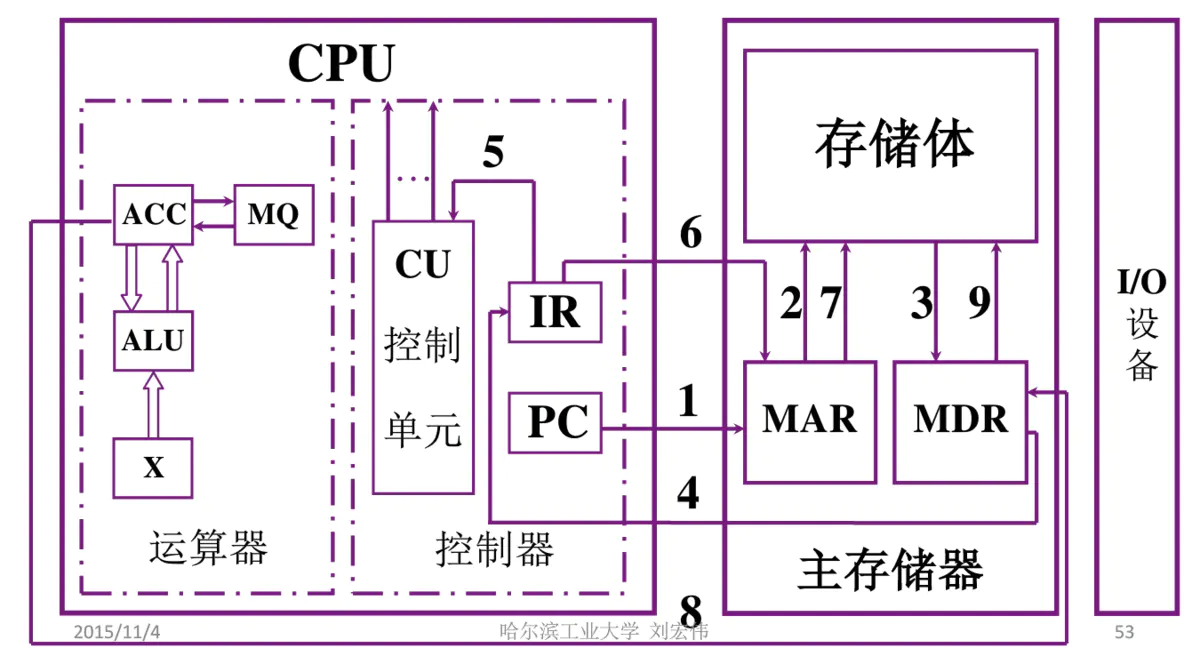

(2)主机完成一条存数操作步骤

存数指令的功能:把存放在ACC中的计算结果存到内存单元M中

存数操作步骤分析(如图):

- 要执行的指令的地址保存在PC中,指令保存在存储体中;第一步将PC中要执行的指令的地址放入MAR;

- MAR将指令地址送给存储体M;

- 在控制器的控制下,存储体M将指令地址中的指令送给MDR;

- 在控制器的控制下,将MDR中的指令存到IR中;(到此,取指令的操作完成;PC—>MAR—>M—>MDR—>IR)

- 分析指令:将IR中指令的操作码部分给CU,由CU去分析控制执行;

- 把IR中指令中待存的数的地址送到MAR;(从这一步开始不同)

- MAR将数的地址送给存储体M,告诉存储体要存进来一个数,其地址是多少;

- 在控制器的控制下,将ACC中要存的数交给MDR;

- 在控制器的控制下,将MDR中的数交给存储体。

1.3 计算机硬件指标

1.3.1 字长

机器字长

CPU一次能处理数据的位数(如可以对两个8位二进制数进行加法,就是8位),与CPU中的寄存器(ACC,X,MQ)的位数有关。

- 一般来说,机器字长越长性能越好。

- 机器字长反映了计算机的运算精度,即字长越长,数的表示范围也越大,精度也越高。

存储字长

一个存储单元存储一串二进制代码(存储字专),这属串二进制代码的位数称为存储字长,存储字长可以是8位、16位、32位等。

指令字长

一个指令字中包含二进制代码的位数。

编址

- 按字编址,就是机器字长编址,机器为32 位,4B就是一个单位,机器字长为64 位,8B就是一个单位

- 按字节编址,1B就是 一个单位

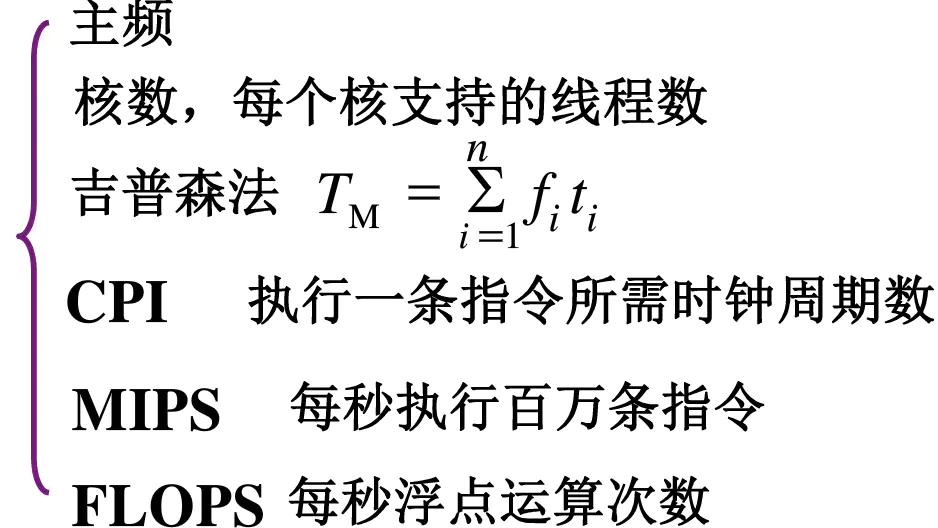

1.3.2 运算速度

前两个是硬件指标;后四个是从指令执行的角度来衡量的。

1) 各种周期比较

| 时钟周期 | 时钟周期是计算机中最基本的、最小的时间单位 | |

| 机器周期(cpu周期) | 机器周期也称为CPU周期。在计算机中,为了便于管理,常把一条指令的执行过程划分为若干个阶段(如取指、译码、执行等),每一阶段完成一个基本操作。完成一个基本操作所需要的时间称为机器周期。一般情况下,一个机器周期由若干个时钟周期组成 | |

| 指令周期 | 一般由若干个机器周期组成,是从取指令,分析指令到执行完所需的全部时间。 取指周期 间址周期 执行周期 中断周期 | |

| 存储周期 | 存储器进行一次“读”或“写”操作所需的时间称为存储器的访问时间(或读写时间),而连续启动两次独立的“读”或“写”操作(如连续的两次“读”操作)所需的最短时间,称为存取周期(或存储周期)。 | |

| 存取时间 | 存储访问时间,也可以称之为存取时间,是指从启动一次存储器操作到完成该操作所经历的时间。 | |

| 总线周期 | 总线周期通常指的是CPU完成一次访问MEM或I/O端口操作所需要的时间。一个总线周期由几个时钟周期组成。 |

将机器周期定为单位1ns,则指令周期为1~4ns,时钟周期为1/6s,总线周期为2/3ns(一个总线周期一般包含bai4个时钟周期)。

存取时间<存储周期

时钟周期<机器周期<指令周期

2) CPI

CPU 执行一条指令所需的时钟周期数

系统结构,指令集,计算机组织都会影响CPI,而时钟频率不会

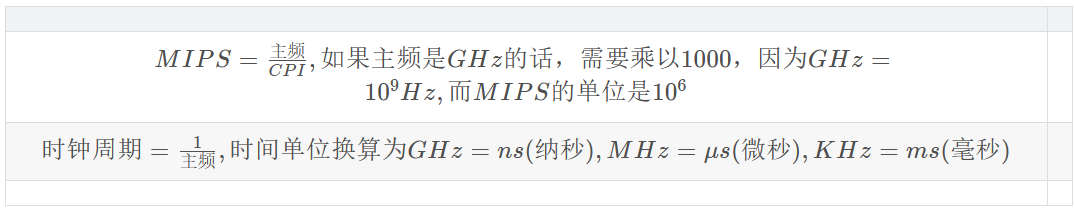

3) 主要的计算

1.3.3 存储容量

存放二进制信息的总位数