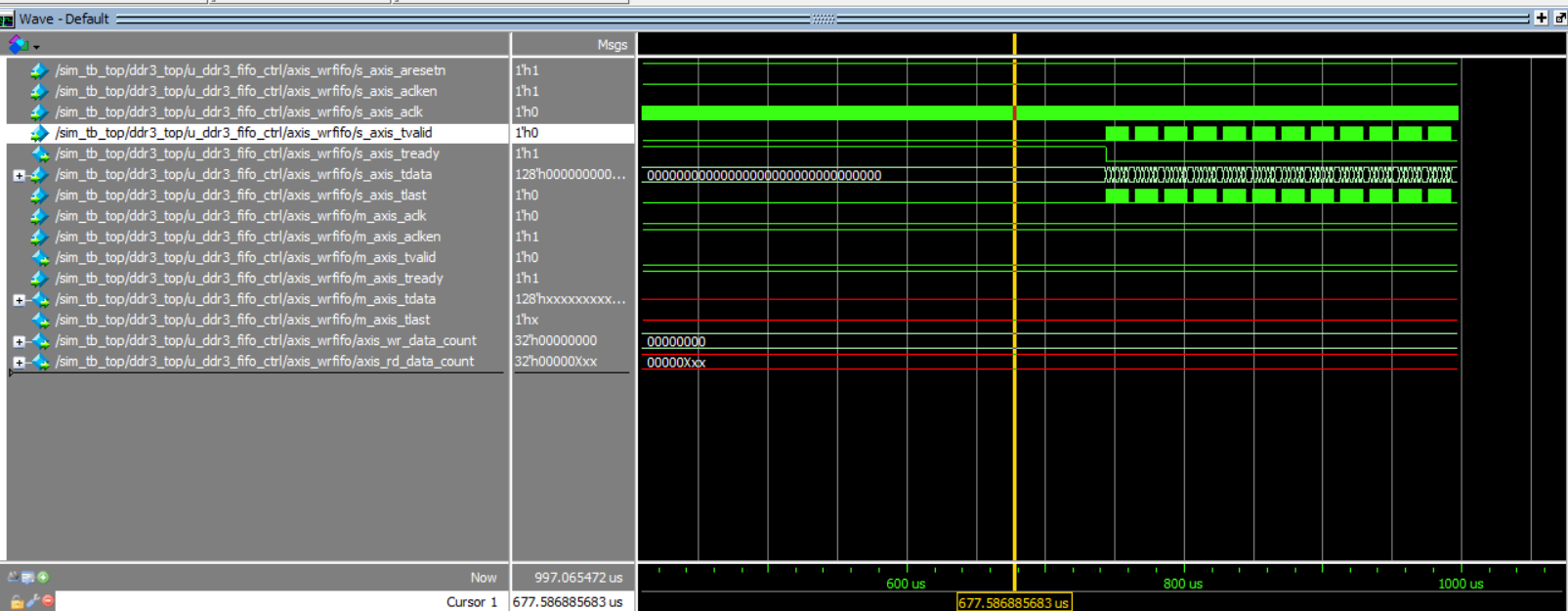

1、 s_axis_tready出现异常情况

如图所示,一开始s_axis_tready是正常的,但是之后开始写入数据时,s_axis_tready没拉起来。

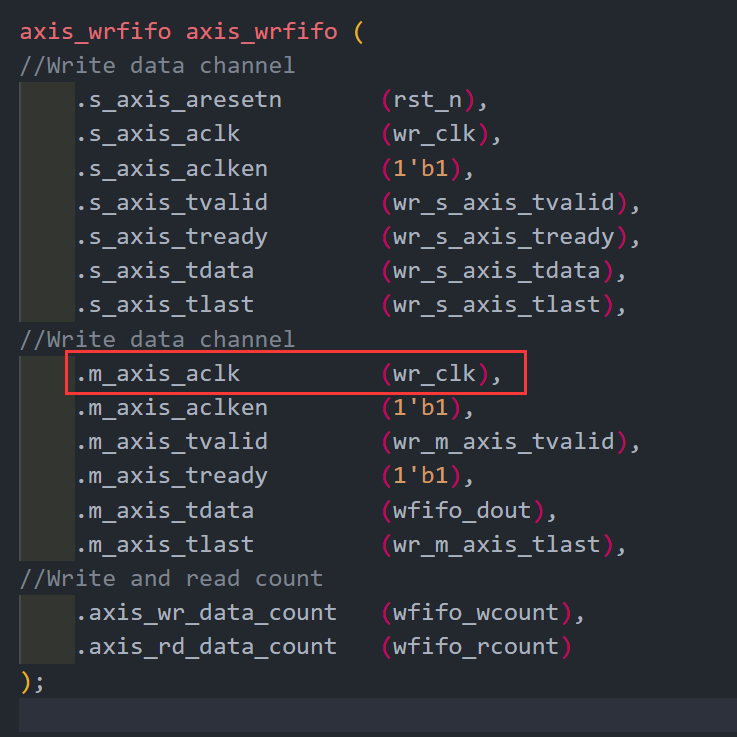

检查了一遍,然后经过测试发现,读数据端的时钟无效,然后造成s_axis_tready没有拉起来,把读数据的时钟换成正常时钟后,s_axis_tready也变正常了。

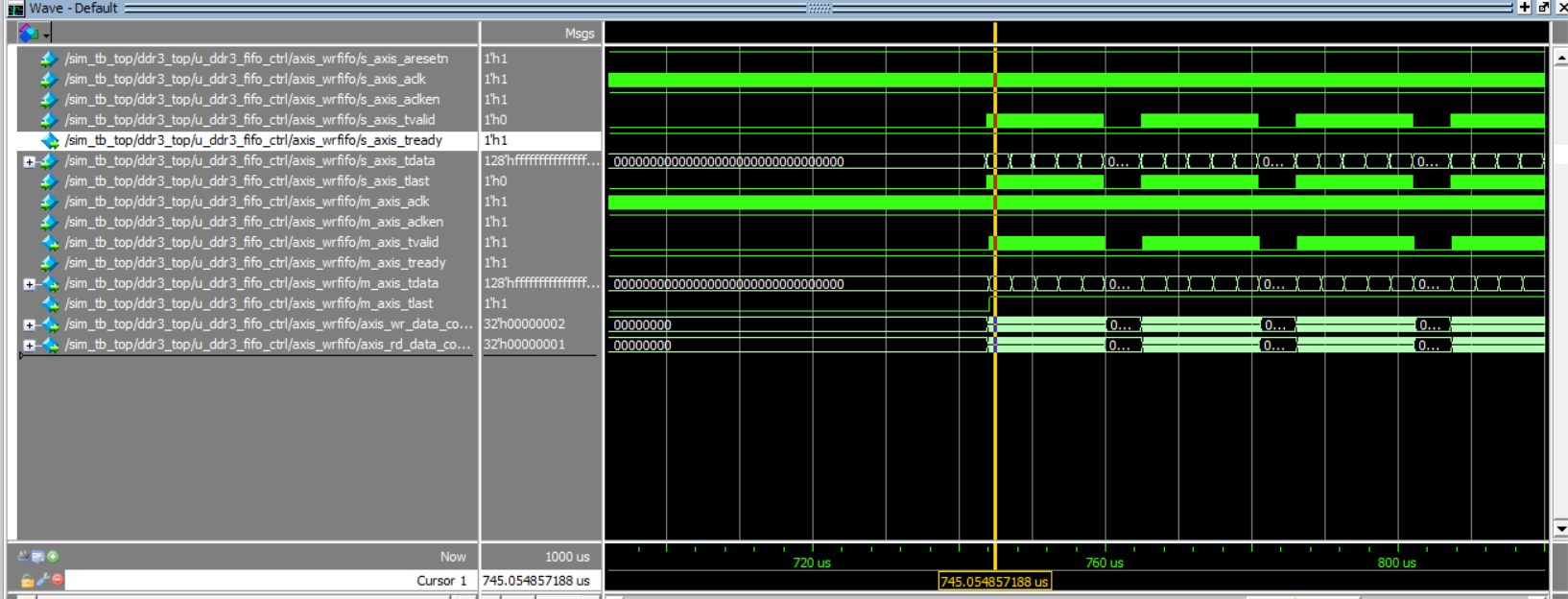

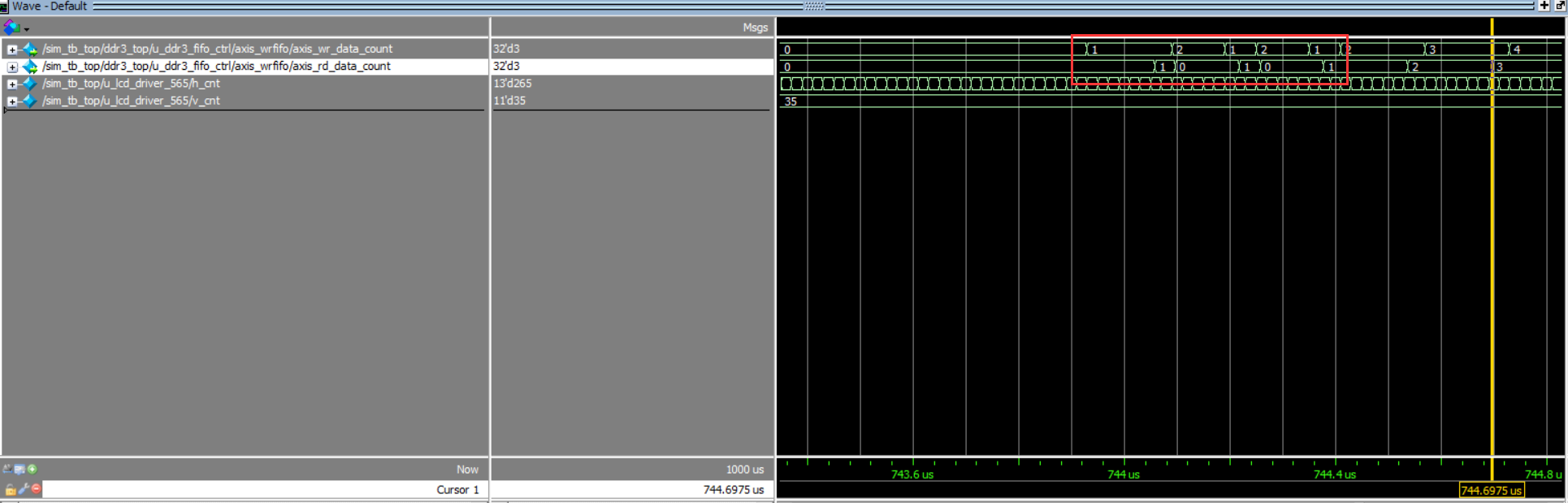

2、axis_wr_data_count计数问题

在观察axis_wr_data_count计数时,我发现一开始的读数出现几次重复的0到1计数,百思不得其解,结果如下图所示。

后来去做了一下常规FIFO IP核的仿真,发现结果也是一样

然后我翻了一下正点原子的文档,最后发现解析如下:

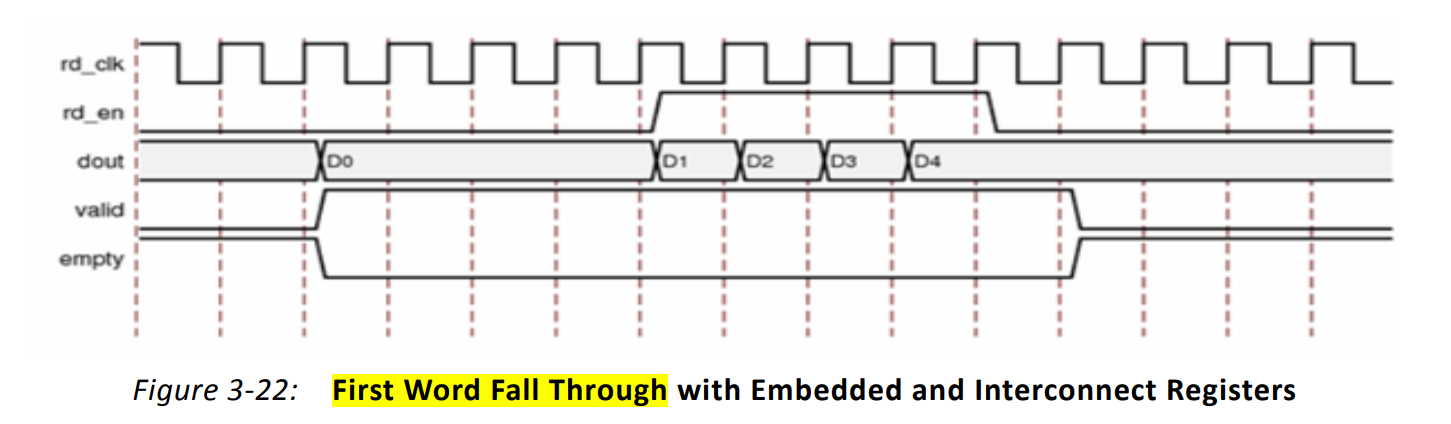

这是FIFO的First Word Fall Through模式,Xilinx官方文档PG057的解释如下:

The first word fall through maintains a similar behavior with embedded/interconnect register. The empty gives a latency of one more cycle as compared to selecting only one register, before rd_en signal is initiated. The next output is latched when rd_en initiates without any additional latency for BRAM as shown in Figure 3-22