代码

module bug(

input wire clk,

output wire BitOut

);

reg BitIn = 1;

Encoder encoder (

.clk(clk),

.BitIn(BitIn),

.BitOut(BitOut)

);

endmodule

module Encoder(

input wire clk,

input wire BitIn,

output reg BitOut

);

always @(posedge clk) begin

if (BitIn)

BitOut <= 1'b1;

else

BitOut <= 1'b0;

end

endmodule

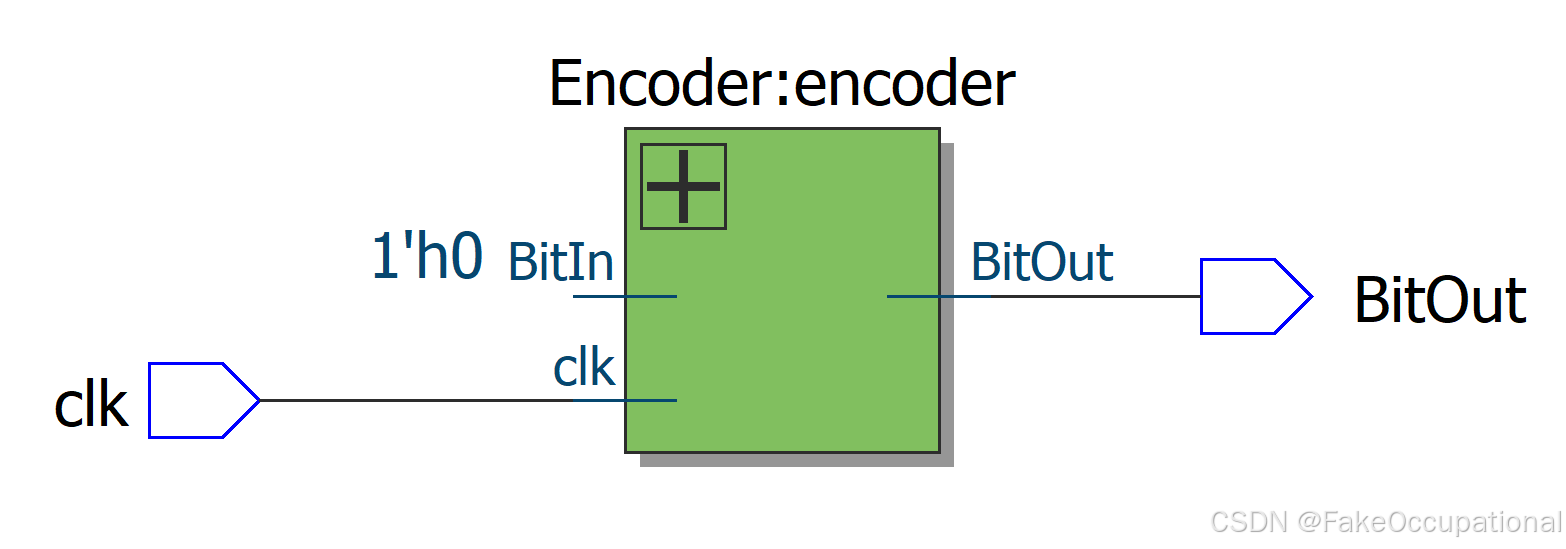

quartus13 综合结果

- 在quartus13中综合得到的BitIn为0:

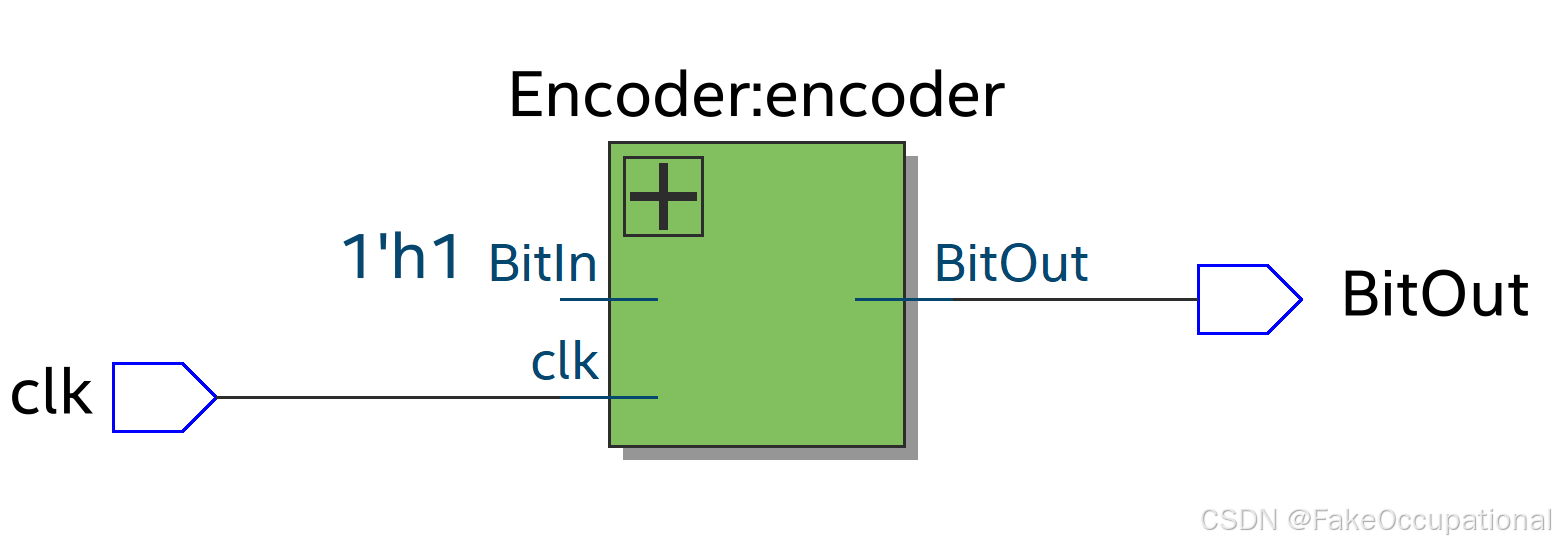

quartus18 综合结果

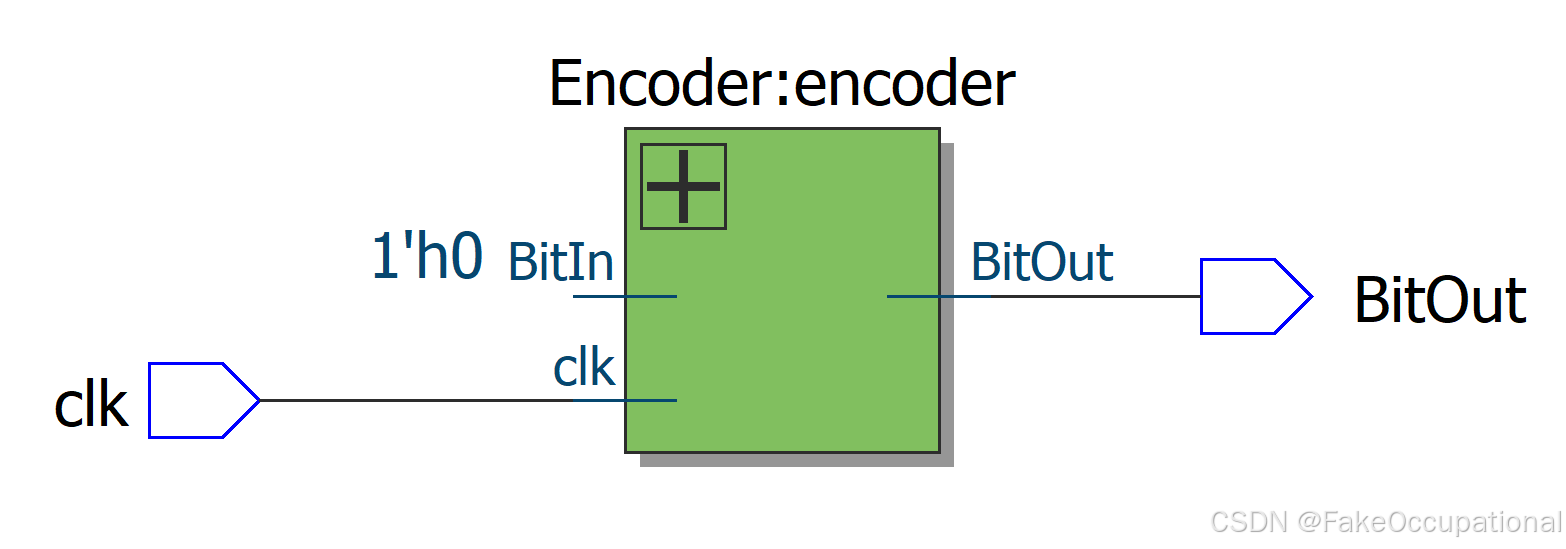

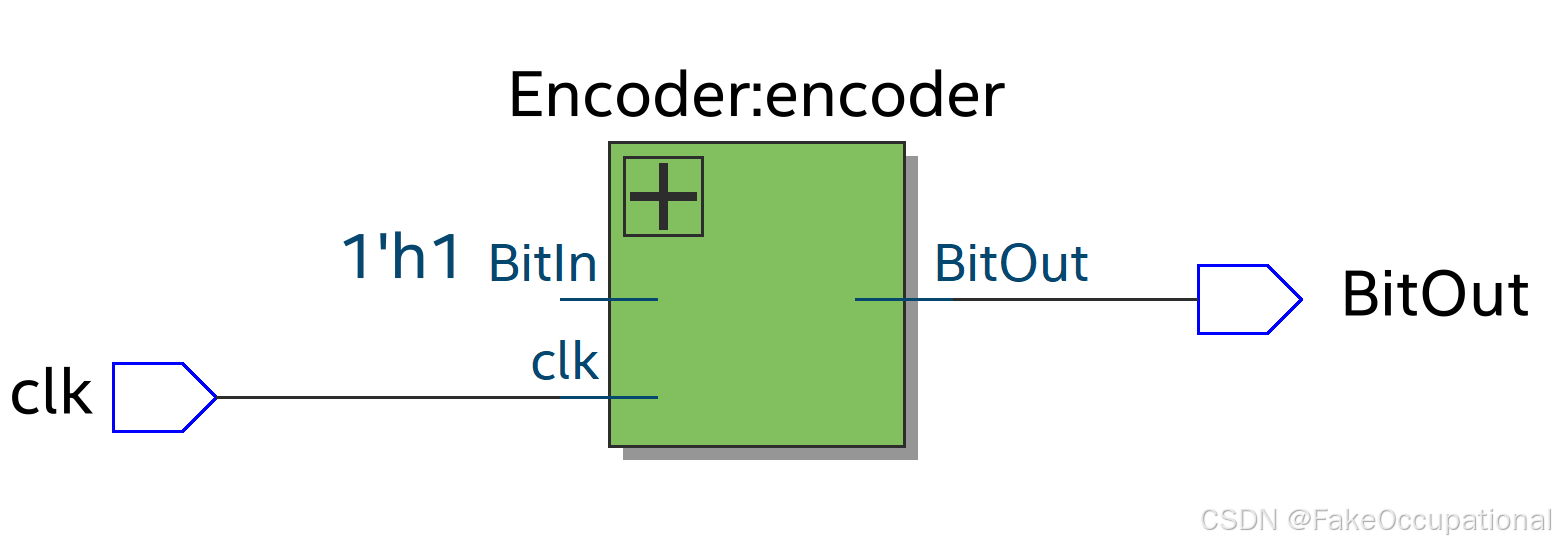

修改方法

module bug(

input wire clk,

output wire BitOut

);

reg BitIn;

always @(posedge clk) begin

BitIn <= 1;

end

Encoder encoder (

.clk(clk),

.BitIn(BitIn),

.BitOut(BitOut)

);

endmodule