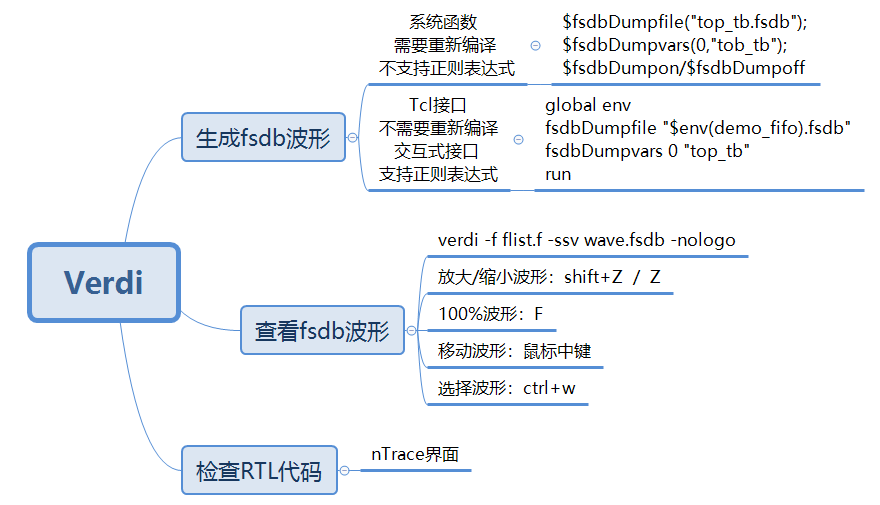

Verbi

testbench

时钟激励:

- always # 10 clk=~clk;

- initial forever #5 clk=~clk

随机数:

- a={$random}%30; //0-30之间的随机数

- a=$random%30; //-30-30之间的随机数

同步数据

- @(posedge/negedge clk) //时钟沿执行一次

打印

- $display(“XXX”); //语法同C的print

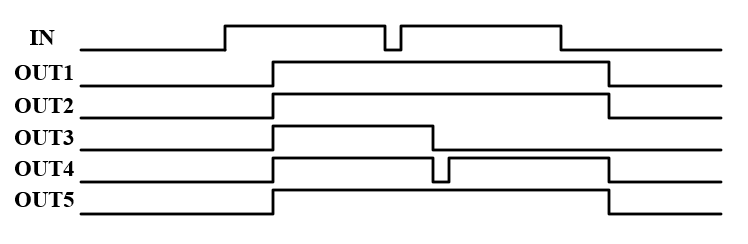

延时:

- 阻塞正规延时:#3 out1 = in; //T+N时刻将T+N时刻的in赋值给sum,小于延迟时间的输入变化被忽略

- 非阻塞正规延时:#3 out2 <= in; //T+N时刻将T+N时刻的in赋值给sum,小于延迟时间的输入变化被忽略

- 阻塞内定延时:out3 = #3 in; //T+N时刻将T时刻的in赋值给sum,小于延迟时间的输入变化被忽略

- 非阻塞内定延时:out4 <= #3 in; //T+N时刻将T时刻的in赋值给sum

- 持续赋值延时:assign #3 out5 = in; //惯性延迟,小于延迟时间的输入变化被忽略

timescale设置:

- 每个module头部设置

- VCS仿真命令添加-timescale 1ns/1ps

- 新建一个V文件,只有一行`timescale定义,在f文件首行引用