CPU Cache

何为cache:cache是内存数据的高速缓存,使用昂贵但是较快速的SRAM技术。如果cpu要访问的数据在cache中,称为“命中”,否则称为“缺失”。cache分为L1 cache、L2 cache、L3 cache,读写延迟依次增加,实现成本依次降低,这样设计是根据性能和价格的折中考虑。程序的数据和指令分别存储在两片cache中,对应数据缓存(D-cache)和指令缓存(L-cache)。

程序局部性原理:最近被CPU访问的数据短期内还要访问(时间局部性),被访问数据附近的数据短期内也会被CPU访问(空间局部性)。cache位于CPU和内存之间,存储内存中一小部分CPU即将访问的数据,CPU直接从cache中调用,加快读取速度。cache对CPU的性能影响取决于CPU数据交换顺序,以及CPU和cache之间的带宽。

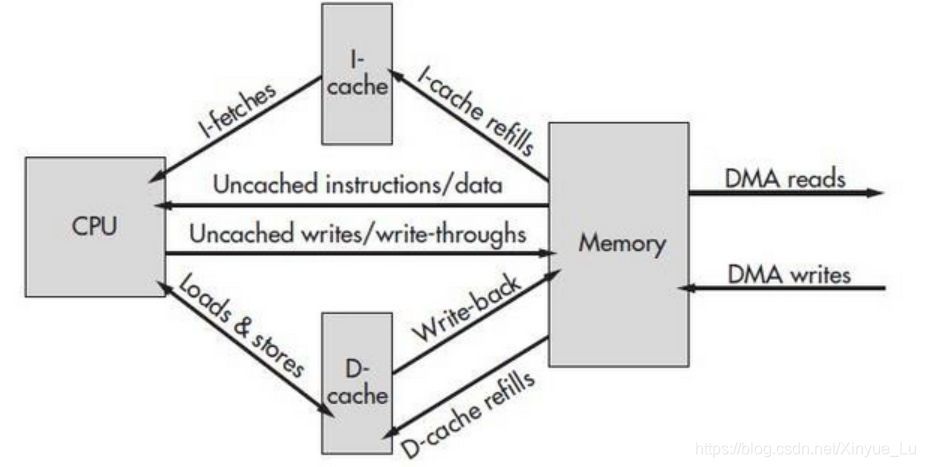

CPU、cache、内存和DMA(Direct Memory Access,直接存储器访问)之间的关系

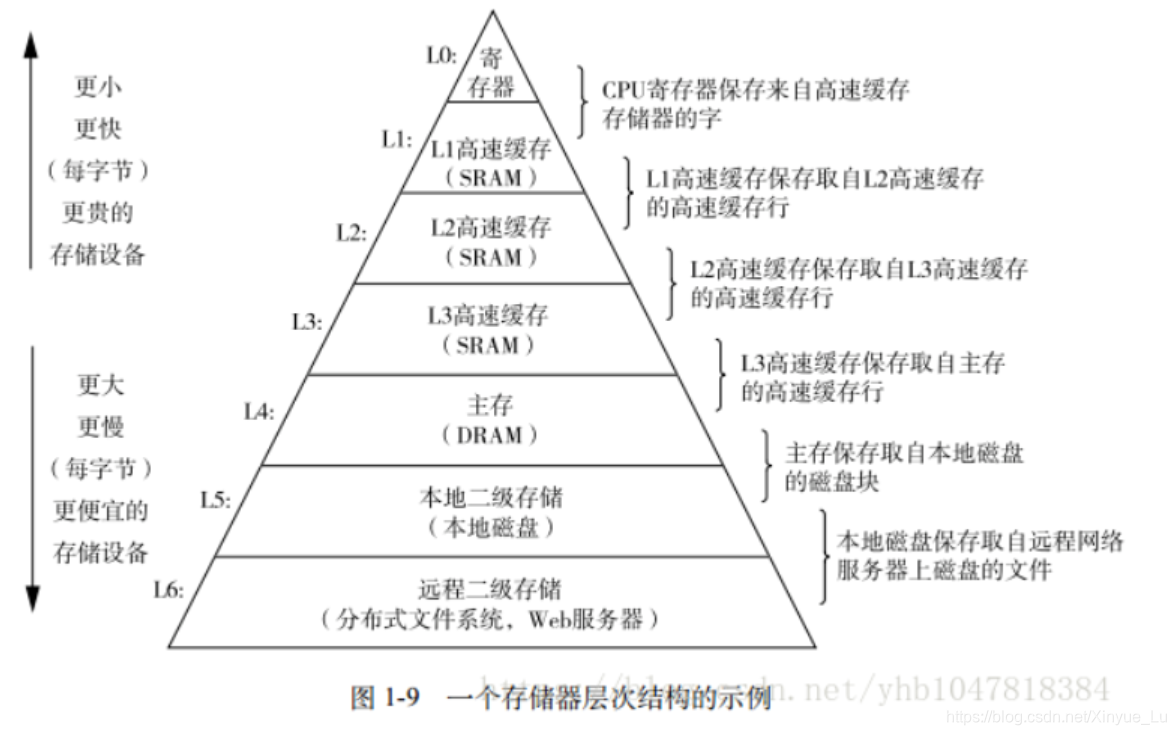

多级CPU cache:L1 cache 和 L2 cache是每个CPU core独立拥有的,L3 cache是多个cores共享的,可以认为是一个更小但是更快的内存。以下是典型的存储器层次结构,用到了三级缓存。

CPU与cache的交互过程:CPU收到指令后,会先去L1cache寻找相关数据,一级缓存和CPU同频运行,如果没有命中,则继续向下一级寻找,按L1、L2、L3、内存(主存)、硬盘依次寻找。程序运行过程中,可以使用perf工具观察cache-miss的rate。

linux里用dmidecode查看