高速ADC时钟jitter求解

高速ADC的时钟jitter会影响高速ADC的信噪比SNR,而信噪比决定了模拟前端输入的有效范围。所以需要先确定模拟前端的有效输入范围,然后确定应该满足的SNR,然后推导出时钟jitter。

一、模拟前端动态输入范围和有效位ENOB的关系

假设ADC的最大输入幅度是Vpp(单位V),分辨率位数N位,有效位数ENOB位。

有效位数ENOB是ADC的N位分辨率中实际有用的位数。N位ADC理论最小分辨率满足

然而如果ADC的噪声信号大于1LSB,则ADC采样信号的N位表示中并不是每一位都能表示采样信号,所以实际的分辨率位数会小于N,实际的分辨率位数我们称为有效位数ENOB。因此对于ADC来说,更加有效的参数是ENOB,而不是N,ADC实际的最小分辨率应该为:

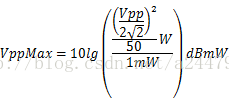

ADC的模拟输入动态范围为(VppMin,VppMax),VppMin和VppMax使用下面公式计算

模拟输入的幅度宽度:

VppMax-VppMin=6.02ENOB

二、有效位ENOB、信噪比SNR、信纳比SINAD,总谐波失真THD之间的关系

2.1、SNR

SNR的定义是信号幅度均方根与噪声幅度均方根的比值。假设信号幅度均方根是S,噪声均方根是N,则