往期内容

本文章相关专栏往期内容,PCI/PCIe子系统专栏:

- 嵌入式系统的内存访问和总线通信机制解析、PCI/PCIe引入

- 深入解析非桥PCI设备的访问和配置方法

- PCI桥设备的访问方法、软件角度讲解PCIe设备的硬件结构

- 深入解析PCIe设备事务层与配置过程

- PCIe的三种路由方式

- PCI驱动与AXI总线框架解析(RK3399)

- 深入解析PCIe地址空间与寄存器机制:从地址映射到TLP生成的完整流程

- PCIe_Host驱动分析_地址映射

- PCIe_Host驱动分析_设备枚举

- PCI/PCIe设备INTx中断机制和MSI中断机制

Uart子系统专栏:

- 专栏地址:Uart子系统

- Linux内核早期打印机制与RS485通信技术

– 末片,有专栏内容观看顺序interrupt子系统专栏:

- 专栏地址:interrupt子系统

- Linux 链式与层级中断控制器讲解:原理与驱动开发

– 末片,有专栏内容观看顺序pinctrl和gpio子系统专栏:

专栏地址:pinctrl和gpio子系统

编写虚拟的GPIO控制器的驱动程序:和pinctrl的交互使用

– 末片,有专栏内容观看顺序

input子系统专栏:

- 专栏地址:input子系统

- input角度:I2C触摸屏驱动分析和编写一个简单的I2C驱动程序

– 末片,有专栏内容观看顺序I2C子系统专栏:

- 专栏地址:IIC子系统

- 具体芯片的IIC控制器驱动程序分析:i2c-imx.c-CSDN博客

– 末篇,有专栏内容观看顺序总线和设备树专栏:

- 专栏地址:总线和设备树

- 设备树与 Linux 内核设备驱动模型的整合-CSDN博客

– 末篇,有专栏内容观看顺序

目录

前言

PCI/PCIe设备INTx中断机制和MSI中断机制-CSDN博客

在看本篇之前建议看一下上一篇关于对MSI中断机制的讲解。

1.MSI-X中断机制

1.1 MSI-X和MSI

MSI(Message Signaled Interrupts)和 MSI-X(Message Signaled Interrupts eXtended)都是 PCI/PCIe 设备用来替代传统中断机制(如 INTx)的两种中断机制。它们都通过发送消息来触发中断,而不再使用物理引脚。但 MSI 和 MSI-X 之间存在一些关键区别,主要体现在中断向量的数量和灵活性上。

1. 中断向量的数量

-

MSI:

- 最多支持 32 个中断向量。

- MSI 中的中断向量数量是 2 的幂次方,例如 1 个、2 个、4 个、8 个、16 个或 32 个。这意味着 MSI 在配置时可能会受限于系统所能提供的中断向量数量。

-

MSI-X:

- 最多支持 2048 个中断向量。

- MSI-X 提供了比 MSI 多得多的中断向量,最多支持 2048 个。这对于设备来说是一个极大的提升,尤其在复杂设备(如网络适配器、存储控制器)中,它们可以为每个不同的功能或任务分配不同的中断向量,提高中断处理的并行性和性能。

2. 中断向量表的存储位置

-

MSI:

- MSI 中断向量(即用于触发中断的消息地址和数据)是在设备配置空间中统一管理的。

- 所有向量共享同一个地址,但发送不同的消息数据。

-

MSI-X:

-

MSI-X 中断向量表是独立的,它的消息地址和数据被存储在设备的内存空间中(而不是设备的配置空间),这提供了更大的灵活性。

-

MSI-X 使用了两个表:

- 向量表(Vector Table/MSI-X Table):存储每个中断向量的消息地址和数据。

- Pending 位表(Pending Bit Array,PBA):用于跟踪中断向量的状态。

-

每个中断向量都有独立的消息地址和数据,因此每个向量可以发送到不同的 CPU 或处理不同的事件。

-

3. 灵活性和功能增强

-

MSI:

- MSI 的中断配置相对简单,所有中断向量的配置基本是统一的,所有向量使用相同的消息地址。

- MSI 支持的中断向量数量有限,因此多线程和并行处理中断处理能力不足。

-

MSI-X:

- MSI-X 具有更高的灵活性。每个中断向量都有单独的消息地址和消息数据,这意味着每个中断可以指向不同的 CPU 核心或不同的中断处理程序。这在高性能和多核处理器系统中非常有用,可以显著提高并行处理能力。

- MSI-X 支持的中断向量更多,能够适应多功能设备和复杂设备的需求。

4. 实现复杂性

-

MSI:

- 相对较为简单,适合一些中小型的设备,系统开销较低。

-

MSI-X:

- 实现更加复杂,因为它需要设备在内存空间中维护两个表,并且在设备和操作系统之间要进行更多的同步管理工作。但对于高性能设备,MSI-X 提供了更好的性能和灵活性。

5. 兼容性

-

MSI:

- MSI 是较早引入的技术,基本上所有支持 PCI/PCIe 的操作系统和硬件平台都支持 MSI。

-

MSI-X:

- MSI-X 是 MSI 的增强版本,并不是所有的设备和操作系统都支持 MSI-X,但现代的 PCIe 设备大多数已经支持 MSI-X,尤其是需要大量并行处理的设备(如网卡、存储控制器等)。

6. 中断的处理过程

-

MSI:

- 当设备触发中断时,它会向指定的 Message Address 写入 Message Data。由于 MSI 使用共享的地址,处理程序根据不同的 Message Data 来识别是哪一个中断向量。

-

MSI-X:

- MSI-X 的每个中断向量都有单独的 Message Address 和 Message Data,设备通过独立的地址和数据来触发特定的中断。这使得系统可以直接通过中断地址来区分不同的中断源,处理更加高效。

7. 性能和应用场景

-

MSI:

- 适用于一般性能要求的设备,例如通用的 PCI/PCIe 设备,支持多达 32 个中断向量,适合大多数情况。

-

MSI-X:

- 适用于高性能、多线程、多功能设备。例如,服务器网卡、存储适配器等使用 MSI-X,可以为每个 I/O 队列或网络连接分配独立的中断向量,大幅提高性能。

| 特性 | MSI | MSI-X |

|---|---|---|

| 中断向量数量 | 最多 32 个 | 最多 2048 个 |

| 向量表存储位置 | 设备配置空间 | 设备内存空间(通过两个表) |

| 灵活性 | 所有向量共享同一消息地址 | 每个向量有独立消息地址和数据 |

| 实现复杂性 | 简单 | 复杂 |

| 应用场景 | 一般性能要求设备 | 高性能、多核、多线程设备 |

1.2 提问

假设MSI-X可以支持很多中断,每个中断的"地址/数据"都不一样。提问:在哪里描述这些信息?

-

“地址/数据”:

- 不放在配置空间,空间不够

- 放在PCI设备的内存空间:哪个内存空间?哪个BAR?内存空间哪个位置(偏移地址)?

- 系统软件可以读写这些内存空间

- 位置:设备配置空间的****Table Offset/Table BIR > MSI-X Table(不在配置空间中)

-

中断的控制信息

- 使能/禁止?

- 地址是32位还是64位?

- 这些控制信息也是保存在PCI设备的内存空间

- 位置:设备配置空间的Capabilities Pointer > MSI-X capability(在配置空间中) > Message Control(在配置空间中)

-

中断的状态信息(挂起?)

- 这些信息也是保存在PCI设备的内存空间

- 位置:设备配置空间的****PBA Offset/PBA BIR > Pending Bit Array(不在配置空间中)

1.3 MSI-X capability

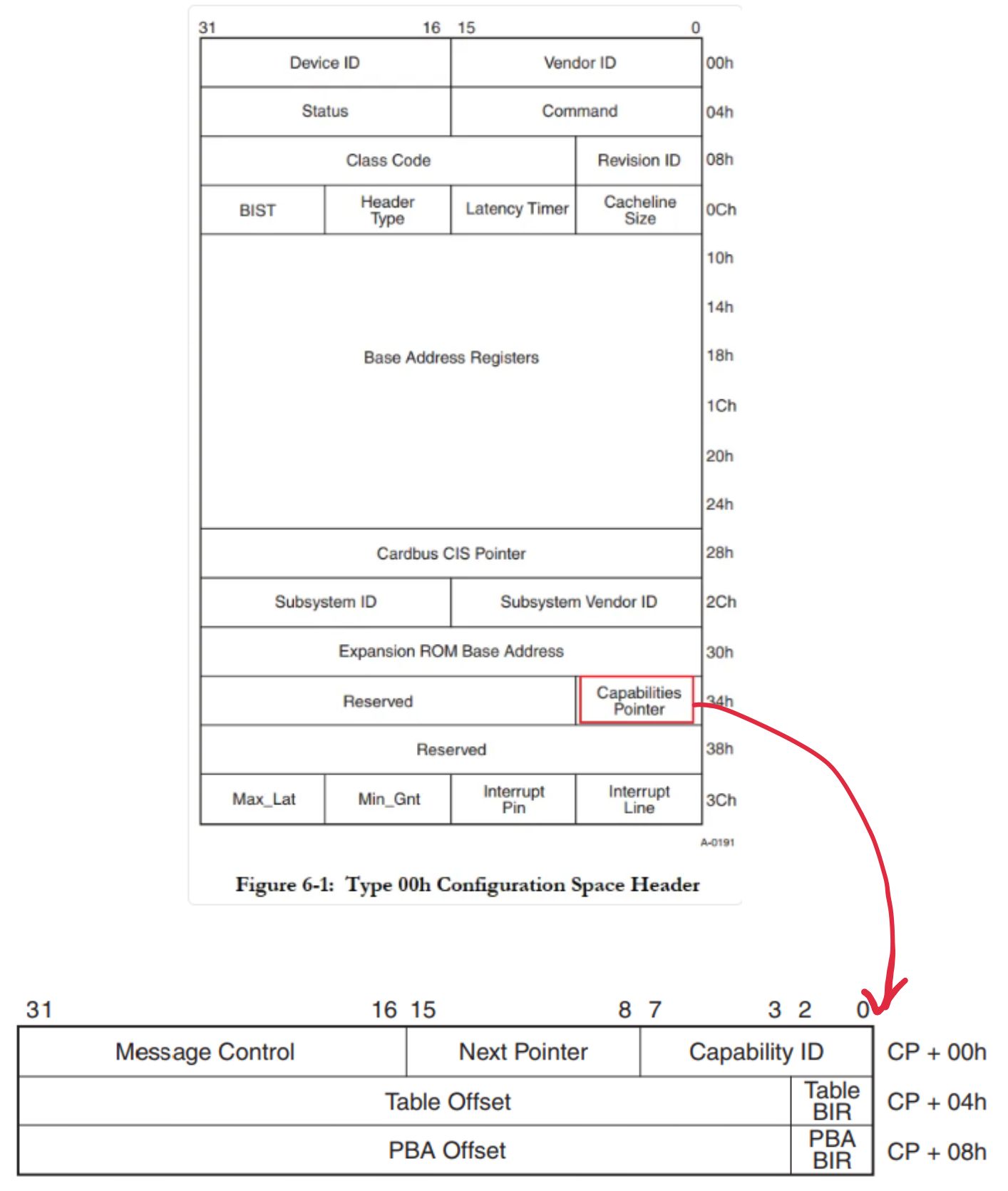

一个PCI设备是否支持MSI-X,需要读取配置空间的capability来判断: 有MSI-X capability的话就支持MSI-X机制。

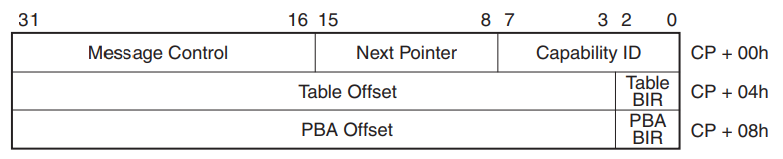

MSI-X capability格式如下:

1.MSI-X capability格式解析

格式解析如下:

- Capability ID:对于MSI-X capability,它的ID为11H

- Next Pointer:下一个capability的位置,00H表示这是最后一个capability

- Message Control

| 位 | 名 | 描述 |

|---|---|---|

| 15 | MSI-X Enable | 是否使能MSI-X: 1: 使能 0: 禁止 注意: MSI-X和MSI不能同时使能。 |

| 14 | Function Mask | 相当于MSI-X中断总开关: 1: 所有中断禁止 0: 有各个中断的Mask位决定是否使能对应中断 |

| 13 | 保留 | |

| 10:0 | Table Size | 系统软件读取这些位,算出MSI-X Table的大小,也就是支持多少个中断 读出值为"N-1",表示支持N个中断 |

- Table Offset/Table BIR :BIR意思为"BAR Indicator register",表示使用哪个BAR。

| 位 | 域 | 描述 |

|---|---|---|

| 31:3 | Table Offset | MSI-X Table保存在PCI设备的内存空间里, 在哪个内存空间?有下面的"Table BIR"表示。 在这个内存空间的哪个位置?由当前这几位表示。 |

| 2:0 | Table BIR | 使用哪个内存空间来保存MSI-X Table? 也就是系统软件使用哪个BAR来访问MSI-X Table? 取值为05,表示BAR0BAR5 |

- PBA Offset/PBA BIR:PBA意思为"Pending Bit Array",用来表示MSI-X中断的挂起状态。

| 位 | 域 | 描述 |

|---|---|---|

| 31:3 | PBA Offset | PBA保存在PCI设备的内存空间里, 在哪个内存空间?有下面的"PBA BIR"表示。 在这个内存空间的哪个位置?由当前这几位表示。 |

| 2:0 | PBA BIR | 使用哪个内存空间来保存PBA? 也就是系统软件使用哪个BAR来访问PBA? 取值为05,表示BAR0BAR5 |

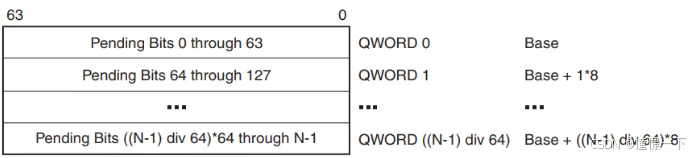

2.MSI-X Table

PCI设备可以往某个地址写入某个数据,从而触发MSI-X中断。

这些"地址/数据"信息,是由系统软件分配的,系统软件要把"地址/数据"发给PCI设备。

PCI设备在哪里保存这些信息?

- 在PCI设备的内存空间

- 在哪个内存空间?由MSI-X capability的"Table BIR"决定

- 在这个内存空间的哪个位置?由MSI-X capability的"Table Offset"决定

MSI-X Table格式如何?如下图所示:

上图中,Msg Data、Msg Addr Msg Upper Addr含义与MSI机制相同:PCI设备要发出MSI-X中断时,往这个地址写入这个数据。如果使用32位地址的话,写哪个地址由Msg Addr寄存器决定;如果使用64位地址的话,写哪个地址由Msg Addr和Msg Upper Addr这两个寄存器决定。

Vector Control寄存器中,只有Bit0有作用,表示"Mask Bit"。系统软件写入1表示禁止对应中断,写入0表示使能对应中断。

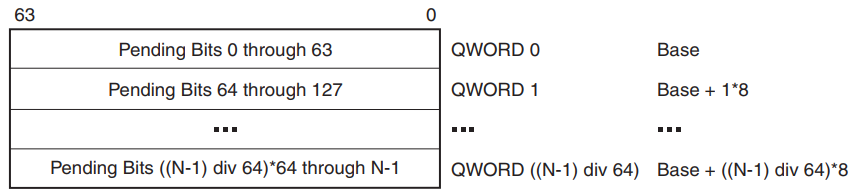

3.PBA

PBA意思为"Pending Bit Array",用来表示MSI-X中断的挂起状态。它的格式如下:

这些"挂起"信息,是由PCI设备设置,系统软件只能读取这些信息。

PCI设备在哪里保存这些信息?

- 在PCI设备的内存空间

- 在哪个内存空间?由MSI-X capability的"PBA BIR"决定

- 在这个内存空间的哪个位置?由MSI-X capability的"PBA Offset"决定

PBA格式如下:每一位对应一个中断,值为1表示中断发生了、等待处理。

2.MSI/MSI-X操作流程

2.1 设备扫描流程

设备扫描是 PCI/PCIe 总线探测的第一步,它遍历 PCI 总线,查找设备并为其分配资源。对于支持 MSI 或 MSI-X 的设备,操作系统会在配置空间的 Capability Pointer 字段中检测是否支持 MSI 或 MSI-X,并根据设备的特性进行相应的配置。

PCI/PCIe 设备扫描

-

扫描根总线:操作系统通过 PCI 总线的根总线扫描挂接的所有设备。

-

读取设备的配置空间:

- 查找设备配置空间中的

Capability Pointer字段,判断设备是否支持 MSI 或 MSI-X。Capability Pointer指向设备配置空间中的第一个扩展能力(如 MSI、MSI-X)。 - 如果设备支持 MSI 或 MSI-X,会找到相应的能力结构,并读取相关的配置寄存器。

- 查找设备配置空间中的

2.2 设备的配置:MSI 和 MSI-X 配置

当配置 PCI/PCIe 设备的中断机制时,可能需要选择启用 INTx、MSI 或 MSI-X 这三种中断方式中的一种。它们在中断的处理方式上有所不同,通常情况下,MSI 或 MSI-X 是首选,因为它们比传统的 INTx 中断机制更高效。

2.2.1 MSI 配置

在配置 MSI(Message Signaled Interrupts)时,系统软件必须通过读取设备的 MSI Capability 寄存器来了解设备对 MSI 的支持情况以及设备能够请求多少个中断向量。

MSI 配置的详细步骤:

-

读取 MSI Capability 寄存器:

- 在设备的配置空间中找到 MSI Capability,其位置由设备的 Capability Pointer 指定。

- MSI Capability 结构包含了

Message Control寄存器,用于指示设备支持的中断向量数量和是否支持多向量中断。

-

确定分配的中断向量数量:

- 系统软件读取设备的

Message Control寄存器,检查设备能够支持的中断向量的最大数量(比如 1、2、4、8 等)。 - 操作系统决定实际分配给设备的中断向量数量,通常由系统的资源和设备需求共同决定。

- 系统软件读取设备的

-

配置中断消息地址和数据:

- 操作系统分配一个中断消息地址(

Message Address),它通常是映射到系统中断控制器(如 APIC 或 GIC)的物理地址。 - 操作系统分配一个中断消息数据(

Message Data),用来表示该中断属于哪个设备和具体哪个中断向量。 Message Address和Message Data会写入设备的 MSI Capability 寄存器中。

- 操作系统分配一个中断消息地址(

-

启用 MSI 中断:

-

- MSI 中断通常由软件通过设置设备的 MSI Enable 位来启用。

- 该位位于

Message Control寄存器中,通过将该位设置为 1,设备即启用 MSI 中断。

-

MSI 多向量支持:

-

如果设备支持多个 MSI 中断向量,所有的中断向量共享一个

Message Address,但Message Data的低位会发生变化,用来标识具体是哪一个中断。例如:- 对于 4 个 MSI 中断,

Message Data的低 2 位可以用来区分不同的中断。

- 对于 4 个 MSI 中断,

-

例子:

- 假设一个设备支持 4 个 MSI 向量,中断消息地址固定为

0xfee00000,每次中断发出的消息数据可以是0x40、0x41、0x42或0x43,这些值通过Message Data的低两位来区分。

2.2.2 MSI-X 配置

MSI-X 是一种扩展的中断机制,相对于 MSI,它支持更多的中断向量并且更加灵活。MSI-X 的相关配置信息不仅位于设备的配置空间中,还存储在设备的内存空间中,称为 MSI-X Table。

MSI-X 配置的详细步骤:

-

读取 MSI-X Capability 寄存器:

- 系统软件通过读取设备配置空间中的 MSI-X Capability,确认设备支持 MSI-X 中断。

- MSI-X Capability 中有指向 MSI-X Table 和 Pending Bit Array(PBA) 的偏移量,这两个表都位于设备的 BAR(Base Address Registers)区域内存中。

-

分配中断向量数量:

- 系统软件读取 MSI-X Capability 的

Message Control寄存器,检查设备支持的中断向量的数量。 - MSI-X 通常支持更多的中断向量,最多可以支持 2048 个独立的中断向量。

- 操作系统决定实际分配多少个中断向量给设备,并为每个中断向量配置唯一的消息地址和消息数据。

- 系统软件读取 MSI-X Capability 的

-

配置 MSI-X Table:

- 系统软件在 MSI-X Table 中填充中断消息地址和中断消息数据。不同于 MSI,MSI-X 的每个中断向量都有独立的消息地址和数据。

- 这些地址和数据会存储在设备的内存空间中,而不是配置空间。

- 操作系统确保

Message Address和Message Data对应正确的中断源。

-

启用 MSI-X 中断:

- 操作系统通过设置设备配置空间中的 MSI-X Enable 位来启用 MSI-X。

- 此外,MSI-X 还允许启用或禁用特定中断向量,通过修改 MSI-X Table 中的相关字段来实现。

-

MSI-X 中断处理:

- 当设备需要触发中断时,它向

MSI-X Table中配置的 Message Address 写入对应的 Message Data。这个操作会导致系统中断控制器收到中断请求。 - 与 MSI 不同,MSI-X 的

Message Data是固定不变的,也就是说 MSI-X 每个中断向量有独立的地址和数据,而不是通过修改Message Data的低位来区分中断。

- 当设备需要触发中断时,它向

-

Pending Bit Array (PBA):

- PBA 用来保存设备中断向量的挂起状态。如果设备尝试发送一个中断请求,但由于中断处理器忙无法立即处理,该中断会被标记为挂起状态并记录在 PBA 中。

- 当中断处理器空闲时,会再次处理这些挂起的中断。

例子:

-

一个设备支持 8 个 MSI-X 中断,每个中断都有独立的

Message Address和Message Data,例如:- 中断向量 1:

Message Address=0xfee00000,Message Data=0x50 - 中断向量 2:

Message Address=0xfee00004,Message Data=0x51 - ……

- 中断向量 1:

-

当设备触发中断时,它会向相应的

Message Address写入Message Data,从而触发中断。

2.3 设备发出中断

当 PCIe 设备需要触发中断时,它会执行以下流程:

2.3.1 MSI 中断触发流程

-

内存写操作触发中断:

- 当设备需要触发中断时,它会向事先配置的

Message Address执行一次写操作,将Message Data写入该地址。 Message Address通常映射到 CPU 的中断控制器,比如 APIC(Advanced Programmable Interrupt Controller)或 GIC(Generic Interrupt Controller)。

- 当设备需要触发中断时,它会向事先配置的

-

中断控制器接收中断:

- 当 APIC 或 GIC 接收到这个写操作后,会解析

Message Data,识别哪个中断源发出了中断,然后通知相应的 CPU 核心处理这个中断。

- 当 APIC 或 GIC 接收到这个写操作后,会解析

2.3.2 MSI-X 中断触发流程

-

内存写操作触发中断:

- MSI-X 设备在向

Vector Table中的Message Address执行写操作时,会将相应的Message Data写入地址。这和 MSI 的触发机制类似,但 MSI-X 允许设备发送多个不同的中断向量。

- MSI-X 设备在向

-

中断控制器处理:

- 中断控制器接收到消息后,解析消息地址和消息数据,然后将中断路由到对应的处理程序。

3.中断处理函数

当系统的中断控制器(如 APIC、GIC)接收到中断后,它会将中断传递给操作系统的中断处理程序。以下是中断处理的典型流程:

3.1 中断处理流程

-

中断控制器发起中断:

- APIC/GIC 将中断请求发送到 CPU,并根据中断向量选择合适的中断处理程序。

-

中断处理程序执行:

- 操作系统内核根据中断向量找到与设备驱动程序注册的中断处理函数,并开始执行。

-

中断处理程序的工作:

-

中断处理函数通常执行以下操作:

- 读取设备的状态寄存器,检查中断的具体来源(如某个传输完成、错误发生等)。

- 根据中断类型执行相应的处理逻辑(如清理传输队列、触发进一步操作等)。

- 向设备写入某些控制寄存器,以确认中断处理完毕,并准备接收下一个中断。

-

3.2 中断结束

- 当中断处理完毕后,中断处理程序会通知 CPU 清除中断状态,并可能启用新的中断请求。

- 系统恢复到正常运行状态,继续执行其他任务。

4.中断处理优化

- 在多核系统中,MSI/MSI-X 可以通过路由不同的中断到不同的 CPU 核心,从而提高中断处理的并行度。

- MSI-X 通过支持更多的中断向量和更灵活的路由,可以显著提升设备性能,特别是在高带宽设备(如网络适配器、存储设备)中。

总结

MSI 和 MSI-X 提供了一种比传统中断机制更高效的中断处理方式。通过内存写操作触发中断,减少了对物理中断引脚的依赖,提升了系统的中断处理效率。具体操作流程如下:

- 设备扫描:系统扫描设备的配置空间,查找

Capability Pointer,判断是否支持 MSI/MSI-X。 - 设备配置:为设备分配中断消息地址和数据,写入设备的配置空间(MSI)或内存空间(MSI-X)。

- 中断触发:设备通过内存写操作向中断控制器发送中断消息,触发中断。

- 中断处理:操作系统调用相应的中断处理函数,处理中断事件,完成后通知设备清除中断状态。

MSI-X 在 MSI 的基础上提供了更灵活和高效的中断处理机制,支持更多中断向量,并且每个中断可以独立配置,适用于复杂、高性能设备。