edge_check.v

module edge_check(

input clk,

input in,

output neg_edge,

output pos_edge

);

reg r1=1'd0;

reg r2=1'd0;

assign neg_edge=(~r1)&r2;

assign pos_edge=r1&(~r2);

always@(posedge clk)

begin

r1<=in;

r2<=r1;

end

endmoduletb.v

`timescale 1ns/1ns

module tb;

//被测模块的输入信号必须在tb中必须是reg型

reg clk;

reg in;

wire neg_edge;

wire pos_edge;

edge_check u1(

.clk(clk),

.in(in),

.neg_edge(neg_edge),

.pos_edge(pos_edge)

);

//产生时钟激励

initial clk = 1;

always #10 clk = ~clk;

//输入激励

initial begin

in=0;

#20;

in = 1;

#20

in=0;

#20;

in=1;

#20;

in=0;

#20;

in=1;

#20;

in=0;

$stop;

end

endmodule

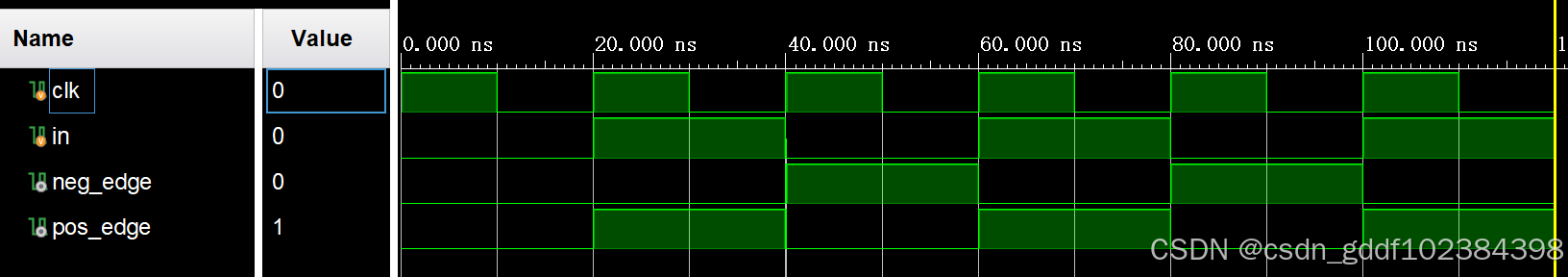

仿真波形: