PWM DAC应用背景

STM32的DAC只有两路输出通道,有些应用可能需要多路DAC,外扩DAC成本会高不少

在精度要求不高的场合,可以用一种廉价的解决方案实现DAC输出:PWM + RC滤波器

什么是PWM DAC技术?

PWM是周期固定,占空比可调的数字信号

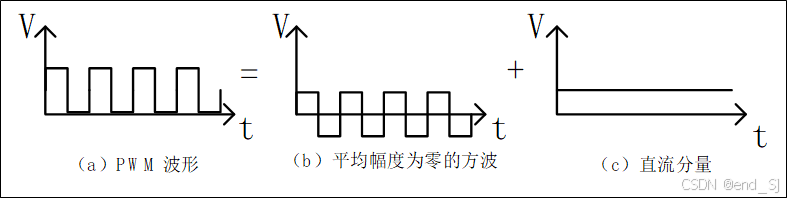

PWM可以被分解为一个直流分量和一个占空比固定,但是平均幅度为零的方波

如果使PWM 信号的占空比随时间改变,那么其直流分量随之改变,信号滤除交流分量后,将输出幅度变化的模拟信号。这种技术称为PWM DAC

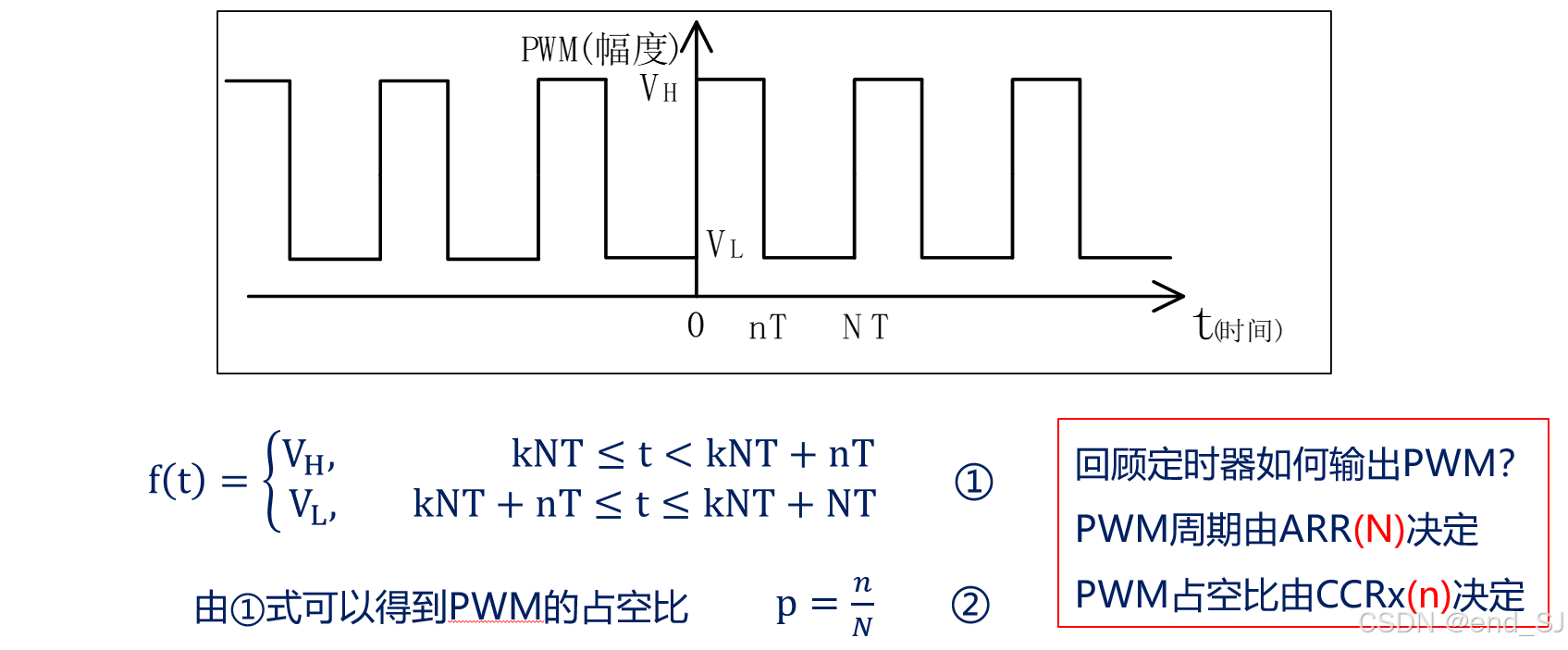

用分段函数表示PWM波

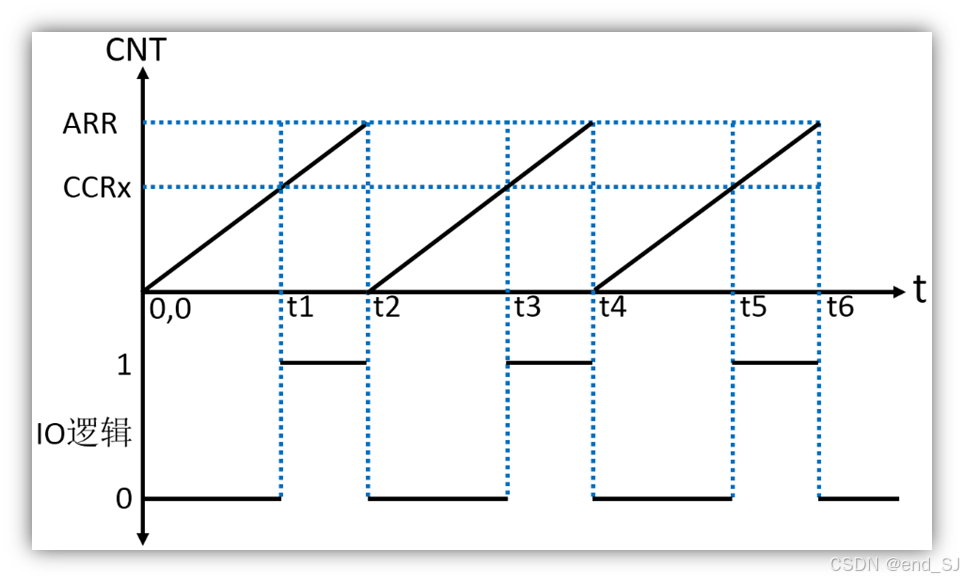

回顾定时器输出PWM原理

假设:递增计数模式

ARR:自动重装载寄存器的值

CCRx:捕获/比较寄存器x的值

当CNT < CCRx,IO输出0, 当CNT >= CCRx,IO输出1

总结:PWM波周期或频率由ARR决定,PWM波占空比由CCRx决定

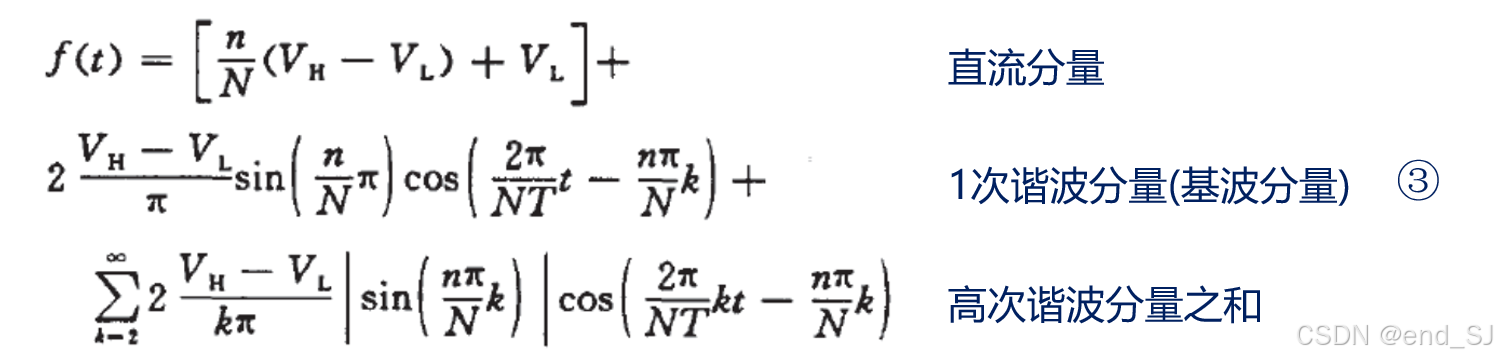

将PWM波分段函数进行傅里叶级数展开

根据傅里叶理论,任意周期波形都可以分解为无限个频率为其整数倍的谐波之和

于是将①式展开成傅里叶级数,可以得到③式:

想要得到PWM DAC输出,我们只保留直流分量,通过低通滤波器过滤掉谐波分量即可

直流分量从0到VH之间随n线性变化

PWM DAC分辨率

由④式可以知道,PWM DAC分辨率的表达式为:

假设n的最小变化是1:

当N=256时,分辨率就是8位(本实验就是以8位分辨率为例);

当N=4096时,分辨率就是12位,以此类推

STM32的定时器都是16位/32位的,可以很容易得到更高分辨率的PWM DAC

当然分辨率越高,速度就慢,低通滤波电路的要求也越高

8位分辨率下对RC滤波器的设计要求

1,精度要求

一般要求1次谐波对输出电压的影响不要超过1个位的精度,也就是3.3/256=0.01289V

2,1次谐波最大值

假设VH为3.3V,VL为0V,那么一次谐波的最大值是2*3.3/π=2.1V

3,RC滤波电路要求

RC滤波电路提供至少-20lg(2.1/0.01289)=-44dB的衰减

4,截止频率要求

当定时器的计数频率为72Mhz,PWM DAC分辨率为8位时,PWM频率为72M/256=281.25Khz

若是1阶RC滤波,则要求截止频率为1.77Khz,若是2阶RC滤波,则要求截止频率为22.34Khz

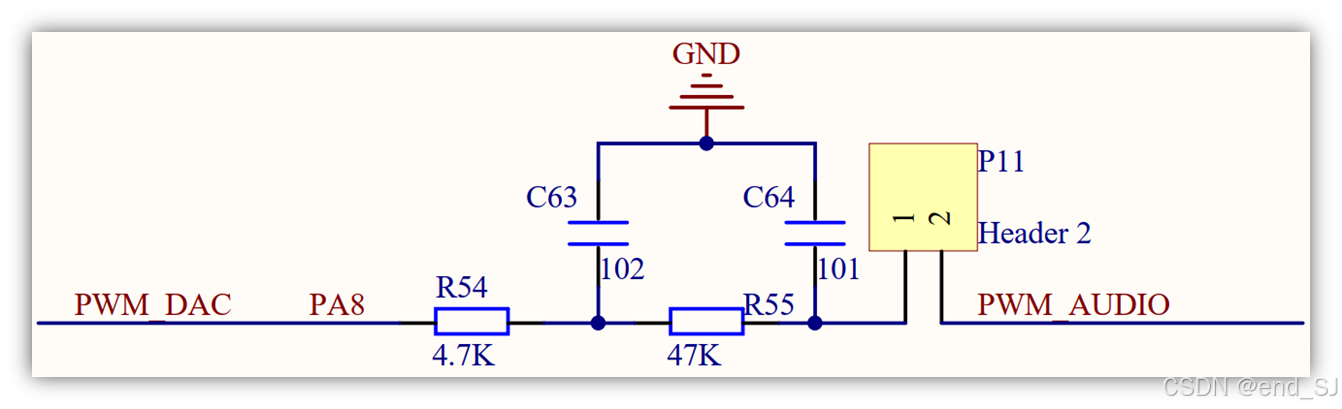

PWM DAC二阶低通滤波器原理图

二阶RC滤波器截止频率计算公式:f = 1/2πRC, 该公式要求R54 * C63 = R55 * C64 = RC

上图中,二阶RC滤波器截止频率为33.88KHz,超过了22.34KHz,原因是该电路我们还需要用作PWM DAC音频输出,而音频信号带宽是22.05Khz,为了让音频信号能够通过该低通滤波,同时为了标准化参数选取,所以确定了这样的参数。实测精度在0.5LSB以内。