一、基本的加法和减法器

1. 一位全加器

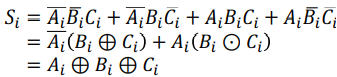

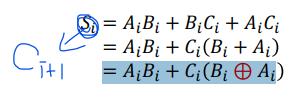

输入由两个加数Ai,Bi和一位进位Ci组成,输出为运算结果Si和进位标志C(i+1)

由真值表可得到结果的运算公式

逻辑电路由进位链和部分和组成,延迟为:6T

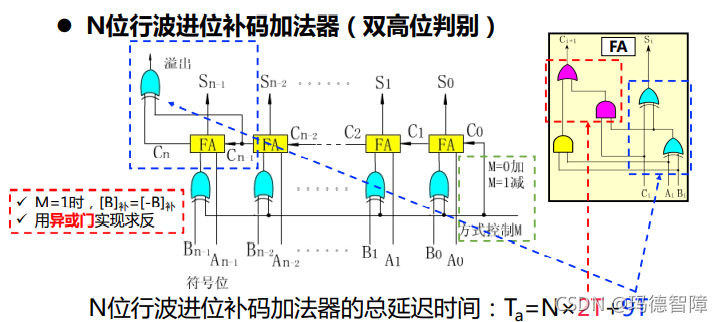

2. N位行波进位补码加法器

电路中的部分功能:

M = 0时,做加法运算,反之做减法运算,做减法运算时,A - B转化成[A]补 + [-B]补来进行

Cn = C(n+1)时,运算无溢出,反之有溢出

总延迟时间:N × 2T + 9T

二、定点乘法运算

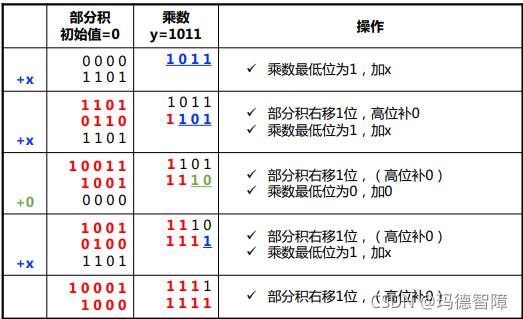

1. 原码一位乘

运算分为移位 +求和

2. 阵列乘法器

1)不带符号位的阵列乘法器与手算方法类似,包括了进位输出、和的输出

2)带符号为的阵列乘法器分为两种

当输入均为原码时,无需进行求补运算,和不带符号位的乘法运算相同,符号位单独运算;

当输入均为补码时,采用间接补码乘法:需要进行三次求补运算,其中算前两次求补得到原码,算后一次求补得到结果补码,符号位单独运算,最后补上符号位

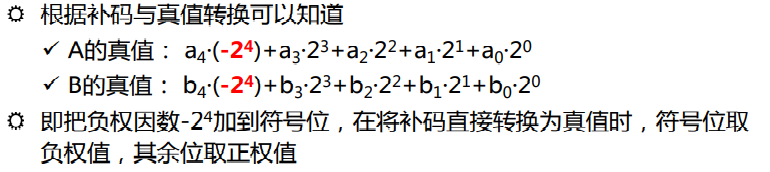

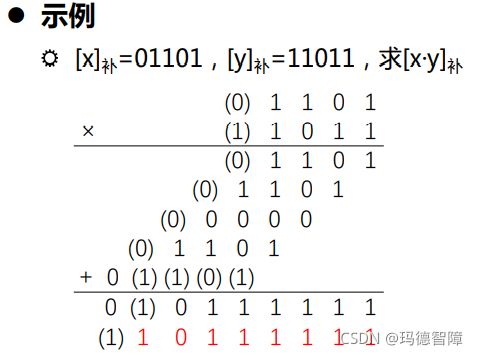

除此之外,还有直接补码乘法,采用了带负权的运算方式。

在运算时,负权位相乘负负得正,正负得负;相加可以进位,负权位与正权位相加可以相互抵消,最后得到的结果如果是0(1),可以变换为(1)0