//##########################################################################//

此开机优化为相对极限式的测试,没有考虑功耗及稳定性!仅作测试及优化方向参考!当然也存在进一步优化的空间待各位发现完善!

速度的优化,很大程度是以提高CPU、DDR及EMMC的速率为基础的。所以使用的较好物料及板子,优化较为显著!

此文档主要是参考3228的《开机优化说明》编写的,针对3288 5.1公板测试。

第一部分:思路分析

开机时间包括四部分时间:

1.硬件响应power按键时间

2.Uboot 初始化系统以及加载kernel image的时间

3.Kernel 启动所需要的时间

4.Init 挂载文件系统以及Android系统启动的时间

优化思路:

1.针对影响响应时间,探讨最佳响应时间,这个主要是考虑长短按的区别。

2.Uboot 去掉不必要的模块,提高cpu,ddr的频率、emmc跑在较高频率来减少加载kernel image的时间,使用非ota固件减少kernel大小等。

3.把一些外围设备的porbe函数中的一些初始化动作放到delay work中去做,减少kernel启动时间,降低kernel中log的输出等级等。

4.优化Init 启动流程,尽可能早启动Android系统。

时间统计方法:

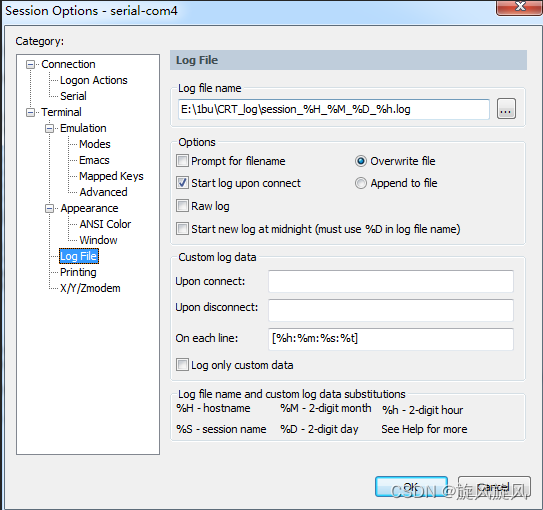

一、可以用serure CRT 设置:打印各部分的时间戳

各部分时间的确认:

3288 8846 sdk公板上目前启动时间是11S-12S之间。

以下是uboot及kernel几个log标志性信息:

10:43:59:019:DDR Version 1.00 2015928_dbg

② 10:43:59:446:U-Boot 2014.10-RK3288-10-g45ba757-dirty (Mar 30 2016 - 08:49:46)

③ 10:44:00:499:Starting kernel ...

④ 10:44:00:969:[ 0.000000] Booting Linux on physical CPU 0x500

⑤ 10:44:05:029:[ 1.136549] Freeing unused kernel memory: 352K (c0b7a000 - c0bd2000)- uboot部分:

uboot时间为分为两部份

①~②为miniloader时间 ,此时间基本固定为400多ms ;

②~③可由u-boot编译调整优化,可控到1秒内;

- kernel:

③~④为kernel解压缩时间,450ms左右与kernel.img包大小相关,img越小,时间越短;

④~⑤可由kernel编译调整优化;

-

android部分(使用logcat -b events | grep boot 打印,④~⑤间的部份时间也包含在内) I/boot_progress_start( 182): 2233 I/boot_progress_preload_start( 182): 3308 I/boot_progress_system_run( 470): 3564 I/boot_progress_pms_start( 470): 4361 I/boot_progress_pms_system_scan_start( 470): 4481 I/boot_progress_pms_data_scan_start( 470): 6233 I/boot_progress_pms_scan_end( 470): 6243 I/boot_progress_pms_ready( 470): 6300 I/boot_progress_preload_end( 182): 6477 I/boot_progress_ams_ready( 470): 7065 I/boot_progress_enable_screen( 470): 8286 8286 减去 2233基本为android所用时间

第二部分:具体优化

开机速度与EMMC以及DDR的性能密切相关。EMMC最好能跑在HS200模式,125M(150M)以上;DDR要1G或者以上,频率越高越好。

POWER按键响应时间

这部分涉及硬件调整,暂不讨论

UBOOT时间优化

1.考虑提高uboot中cpu和ddr的频率默认是(600M,300M),

提高cpu频率为1.2G 如不稳定,请使用1G 关键字CONFIG_RKCLK_APLLB_FREQ_HIGH

提高 ddr频率为双通528M,需使用补丁中的tools/rk_tools/bin/rk32/32_LPDDR2_200MHz_LPDDR3_200MHz_DDR3_200MHz_20150318.bin文件,请慎用!此bin不适用于早期3288 ic

project u-boot/

a/arch/arm/cpu/armv7/rk32xx/clock-rk3288.c b/arch/arm/cpu/armv7/rk32xx/clock-rk3288.c

index b3ea333..066a00e 100755

--- a/arch/arm/cpu/armv7/rk32xx/clock-rk3288.c

+++ b/arch/arm/cpu/armv7/rk32xx/clock-rk3288.c

@@ -14,6 +14,8 @@ DECLARE_GLOBAL_DATA_PTR;

/* ARM/General/Codec pll freq config */

#define CONFIG_RKCLK_APLL_FREQ 600 /* MHZ */

+#define CONFIG_RKCLK_APLLB_FREQ_HIGH 1200/* 1008*/ /* MHZ */

+#define CONFIG_RKCLK_APLLL_FREQ_HIGH 816 /* MHZ */

#ifdef CONFIG_PRODUCT_BOX

#define CONFIG_RKCLK_GPLL_FREQ 300 /* MHZ */

@@ -151,6 +153,10 @@ struct pll_data {

/* apll clock table, should be from high to low */

static struct pll_clk_set apll_clks[] = {

//rate, nr, nf, no, a12_div, mp_div, m0_div, l2, atclk, pclk_dbg

+ /*_APLL_SET_CLKS(1608000,1, 67, 1, 1, 4, 2, 2, 4, 4),

+ _APLL_SET_CLKS(1512000,1, 63, 1, 1, 4, 2, 2, 4, 4),

+ _APLL_SET_CLKS(1416000,1, 59, 1, 1, 4, 2, 2, 4, 4),*/

+ _APLL_SET_CLKS(1200000,1, 50, 1, 1, 4, 2, 2, 4, 4),

_APLL_SET_CLKS(1008000,1, 84, 2, 1, 4, 2, 2, 4, 4),

_APLL_SET_CLKS(816000, 1, 68, 2, 1, 4, 2, 2, 4, 4),

_APLL_SET_CLKS(600000, 1, 50, 2, 1, 4, 2, 2, 4, 4),

@@ -747,6 +753,12 @@ void rkclk_set_pll(void)

rkclk_pll_set_rate(CPLL_ID, CONFIG_RKCLK_CPLL_FREQ, NULL);

}

+void rkclk_set_pll_high(void)

+{

+ rkclk_pll_set_rate(APLL_ID, CONFIG_RKCLK_APLLB_FREQ_HIGH, rkclk_apll_cb);

+ // rkclk_pll_set_rate(APLLB_ID, CONFIG_RKCLK_APLLB_FREQ_HIGH, rkclk_apllb_cb);

+ // rkclk_pll_set_rate(APLLL_ID, CONFIG_RKCLK_APLLL_FREQ_HIGH, rkclk_aplll_cb);

+}