一、简介

IlC(inter-Integrated circuit)总线是一种由NXP(原PHILIPS)公司开发的两线式串行总线,用于连接微控制器及其外围设备。多用于主控制器和从器件间的主从通信,在小数据量场合使用,传输距离短,任意时刻只能有一个主机等特性。

在 CPU 与被控 IC 之间、IC 与 IC 之间进行双向传送,高速 IIC 总线一般可达 400kbps 以上。

SDA:数据线 (inout) SCL:时钟线

通信类别:半双工通信(主机给从机发的时候从机不能给主机发)

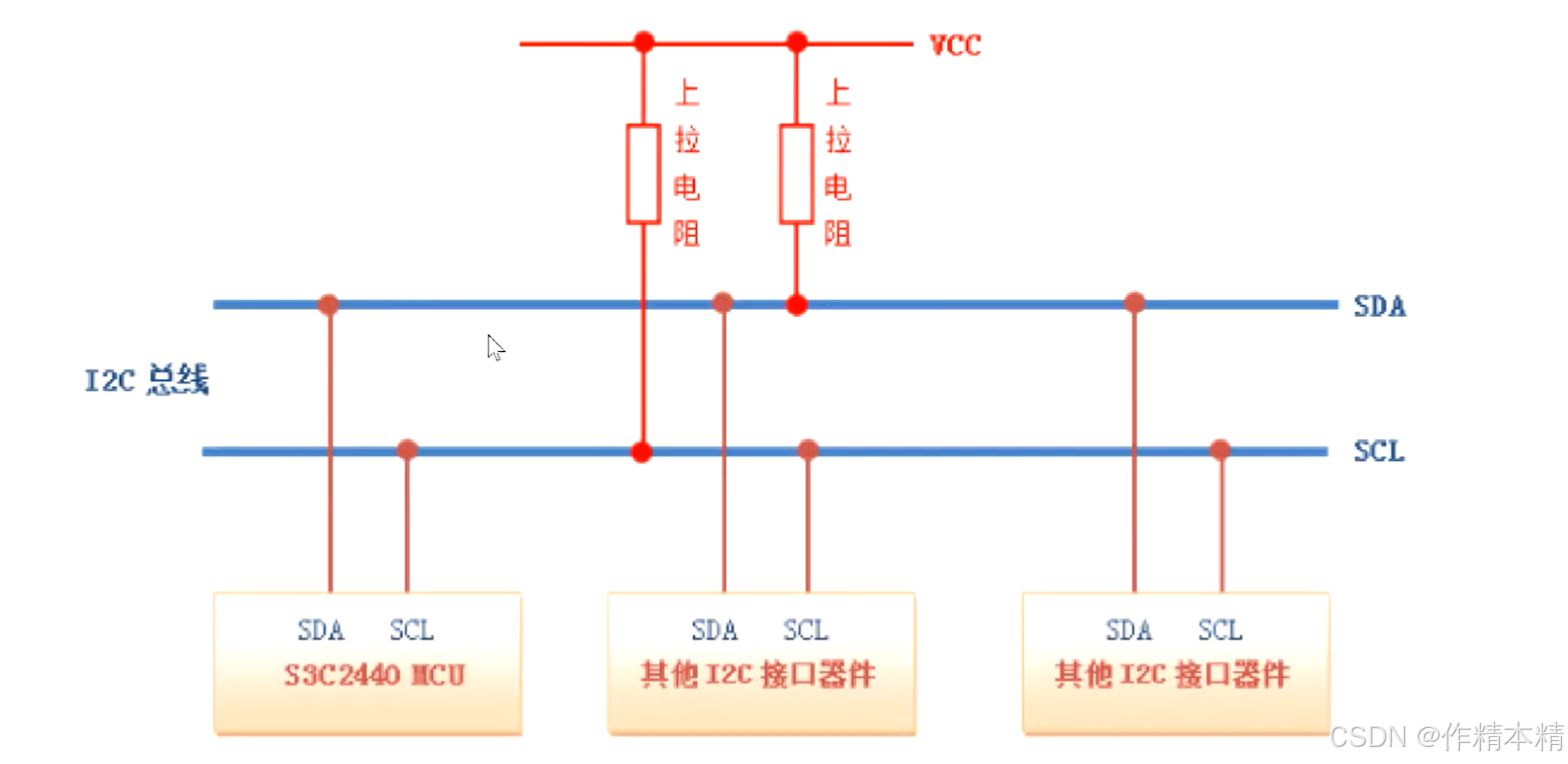

二、物理层链接

IIC一共有只有两个总线:一条是双向的串行数据线SDA,一条是串行时钟线SCL。

SDA(Serial data)是数据线,D代表Data也就是数据,Send Data 也就是用来传输数据的。

SCL(Serial clock line)是时钟线,C代表Clock 也就是时钟 也就是控制数据发送的时序的。

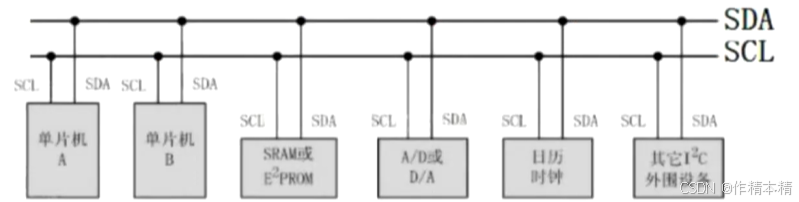

所有接到12C总线设备上的串行数据SDA都接到总线的SDA上,各设备的时钟线SCL接到总线的SCL上12C总线上的每个设备都自己一个唯一的地址,来确保不同设备之间访问的准确性。

(一)IIC的特点

1、IIC主设备功能:主要产生时钟,产生起始信号和停止信号

2、IIC从设备功能:可编程的IIC地址检测,停止位检测。

3、IIC的一个优点是它支持多主控(multimastering),其中任何一个能够进行发送和接收的设备都可以成为主总线。一个主控能够控制信号的传输和时钟频率。当然,在任何时间点上只能有一个主控。

4、支持不同速率的通讯速度,标准速度(最高速度100kHZ),快速(最高400kHZ)。

5、SCL和SDA都需要接上拉电阻(大小由速度和容性负载决定一般在3.3K-10K之间) 保证数据的稳定性,减少干扰。

6、IIC是半双工,而不是全双工,同一时间只可以单向通信。

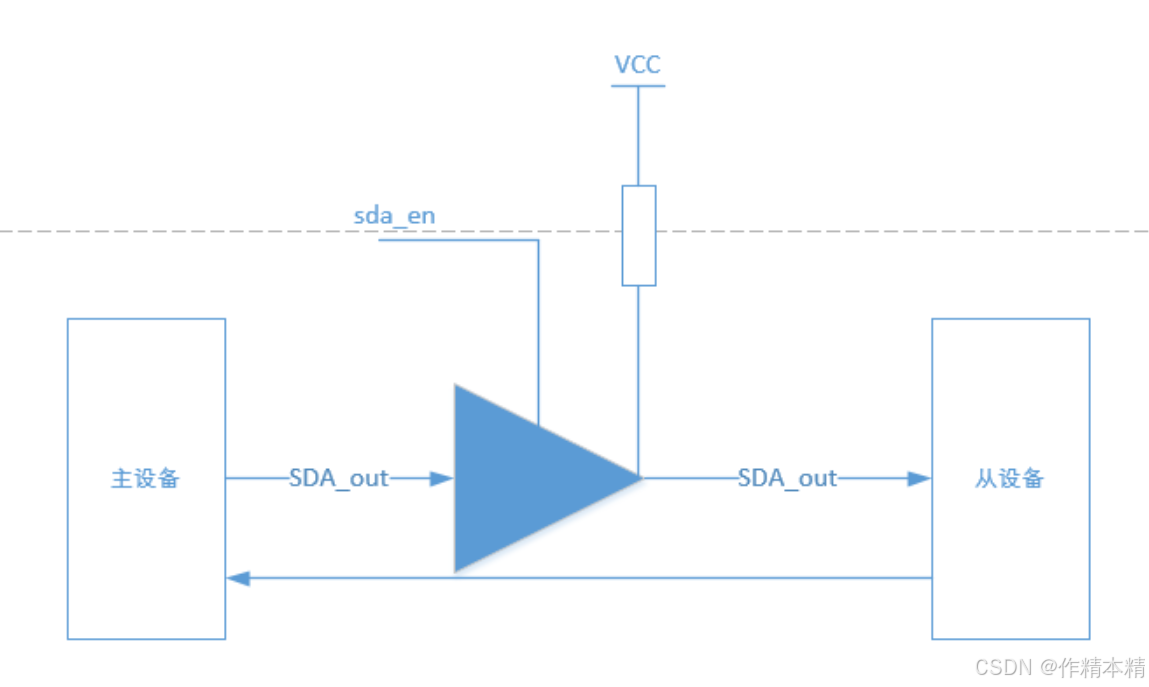

(二)IIC的高阻态

高阻态 = 1'bz = 物理层面断开 = SDA线上电压是VCC = 在数据线上被识别为1

打开sda_en,主设备给从设备传输数据;

关闭sda_en,拉高上拉电阻,让数据线处于高阻态,数据由之前的从设备发送给之前的主设备,之前的从设备作为主机。

高阻状态:高阻状态是三态门电路的一种状态。逻辑门的输出除有高、低电平两种状态外,还有第三种状态--高阻状态的门电路。电路分析时高阻态可做开路理解。

我们知道IIC的所有设备是接在一根总线上的,那么我们进行通信的时候往往只是几个设备进行通信,那么这时候其余的空闲设备可能会受到总线干扰,或者干扰到总线,怎么办呢?

为了避免总线信号的混乱,IIC的空闲状态只能有外部上拉,而此时空闲设备被拉到了高阻态,也就是相当于断路,整个IIC总线只有开启了的设备才会正常进行通信,而不会干扰到其他设备。

(三)器件地址

IIC器件地址: 每一个IIC器件都有一个器件地址,有的器件地址在出厂时地址就设定好了,用户不可以更改,比如OV7670的地址为0x42。有的器件例如EEPROM,前四个地址已经确定为1010,后三个地址是由硬件链接确定的,所以一IIC总线最多能连8个EEPROM芯片

三、协议层

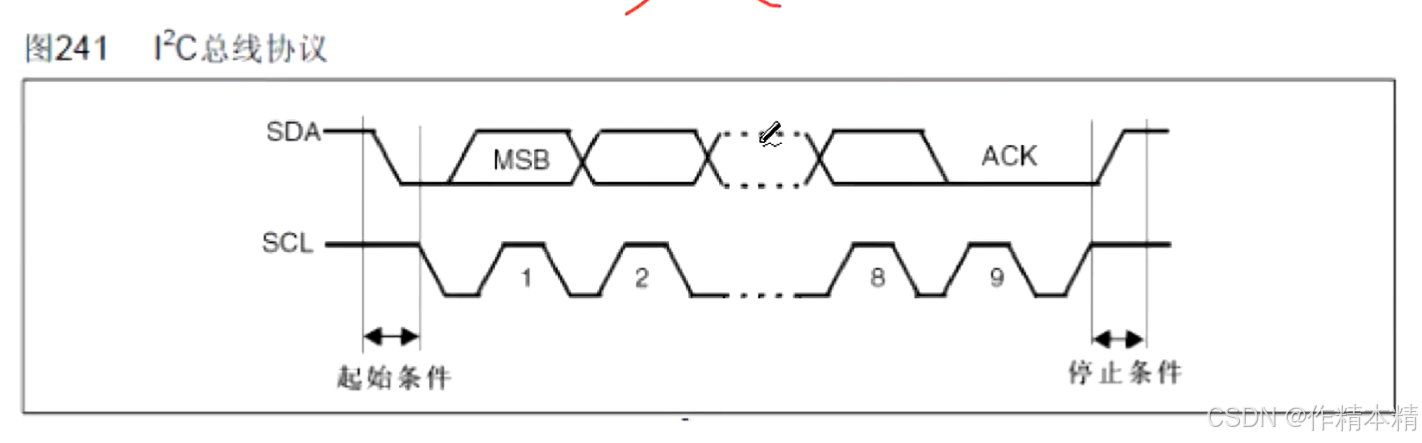

(一)总时序图

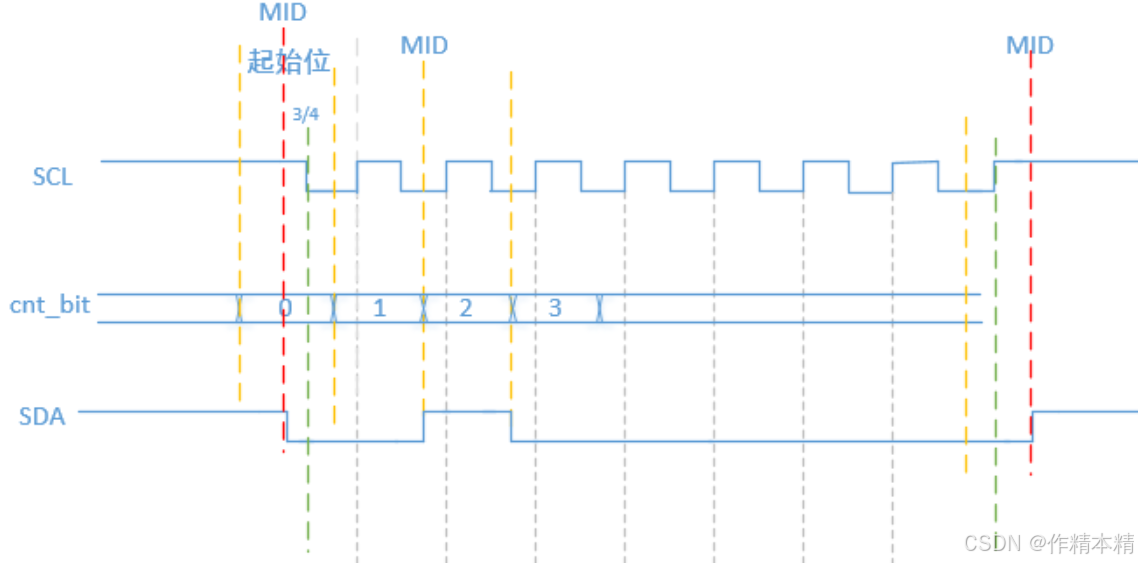

IIC总线在传输数据过程中共有三种类型信号,它们分别是开始信号、结束信号和应答信号。

开始信号:SCL 为高电平时,SDA 由高电平向低电平跳变,开始传送数据。

结束信号:SCL为高电平时,SDA 由低电平向高电平跳变,结束传送数据。

应答信号:接收数据的 I 在接收到 8bit 数据后,向发送数据的 I发出特定的低电平脉冲,表示已收到数据。CPU 向受控单元发出一个信号后,等待受控单元发出一个应答信号,CPU接收到应答信号后,根据实际情况作出是否继续传递信号的判断。若未收到应答信号,由判断为受控单元出现故障。

(二)单个时序图分析

空闲状态

因为IIC的SCL和SDA都需要接上拉电阻,保证空闲状态的稳定性,所以IIC总线在空闲状态下SCL和SDA都保持高电平。

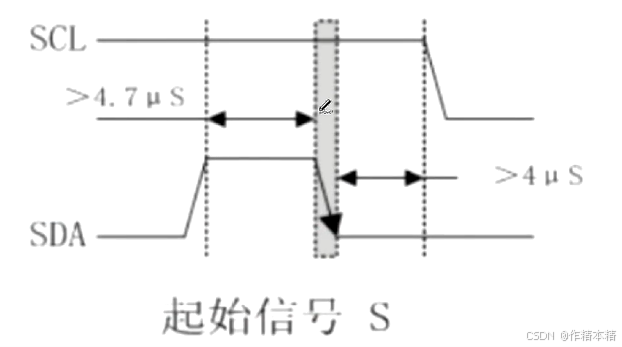

起始信号

SCL保持高电平,SDA由高电平变为低电平,延时(>4.7us),SCL变为低电平。

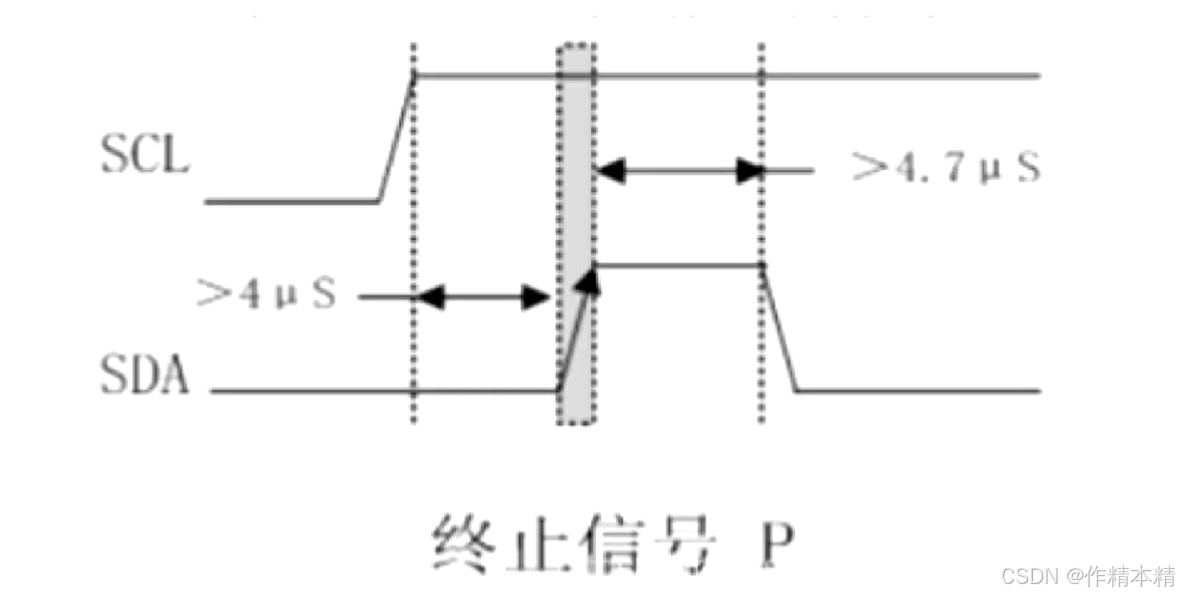

停止信号

SCL保持高电平,SDA由低电平变为高电平。

应答信号

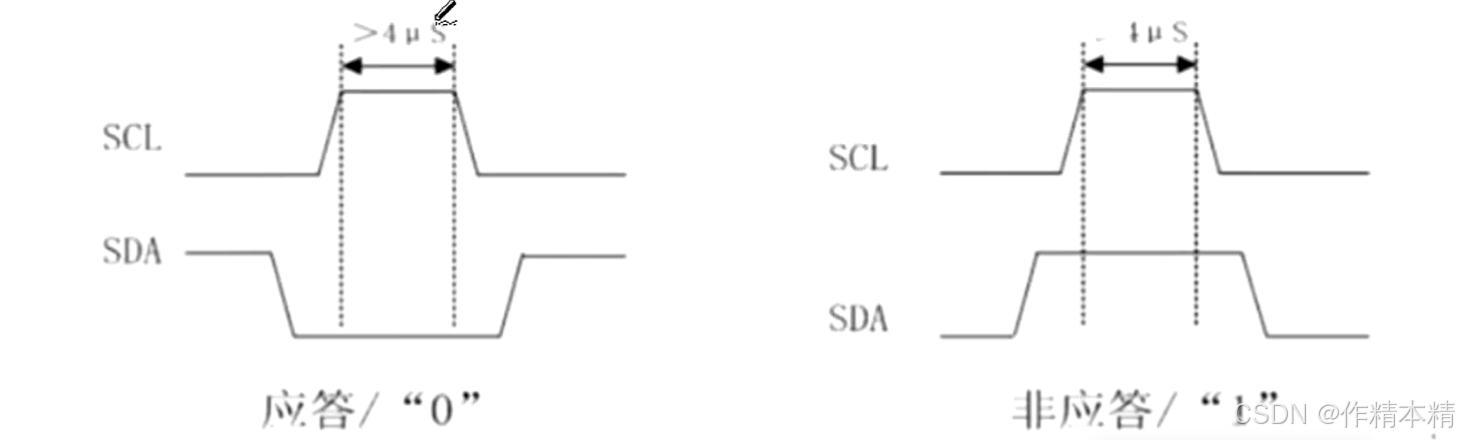

每当主机向从机发送完一个字节的数据,主机总是需要等待从机给出一个应答信号,以确认从机是否成功接收到了数据。

应答信号:主机SCL拉高,读取从机SDA的电平,为低电平表示产生应答

应答信号为低电平时,规定为有效应答位(ACK,简称应答位),表示接收器已经成功地接收了该字节;

应答信号为高电平时,规定为非应答位(NACK),一般表示接收器接收该字节没有成功。

注:每发送一个字节(8bit),在一个字节传输的8个时钟后的第九个时钟期间,接收器收到数据后必须回一个ACK应答信号给发送器,这样才能进行数据传输。应答出现在每一次主机完成8个数据位传输后紧跟着的时钟周期,低电平0表示应答,1表示非应答。

(三)数据传输

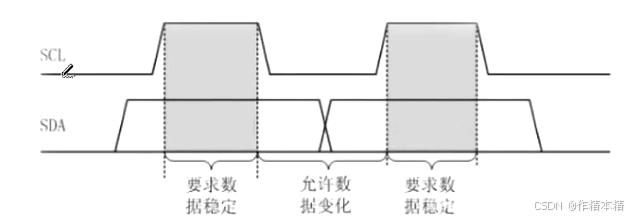

IIC信号在数据传输的过程中,当SCL=1高电平时,数据线SDA必须保持稳定状态,不允许电平跳变,只有在时钟线上的信号为低电平期间,数据线上的高电平或低电平状态才允许变化。

注:SCL=1时 数据线SDA的任何电平变换会看做是总线的起始信号或者停止信号。

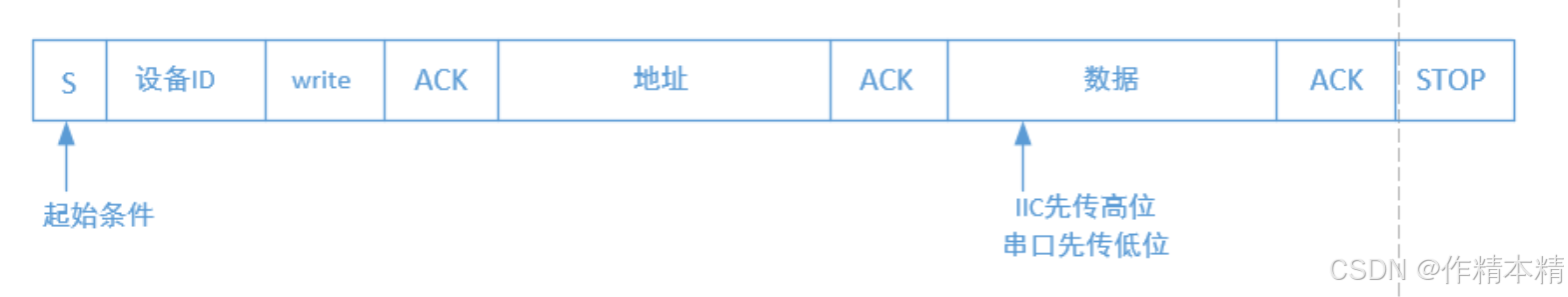

数据传输格式

SDA线上的数据在SCL时钟“高“期间必须是稳定的,只有当SCL线上的时钟信号为低时,数据线上的“高或“低”状态才可以改变。输出到SDA线上的每个字节必须是8位,数据传送时,先传送最高位(MSB),每一个被传送的字节后面都必须跟随一位应答位(即一共有9位)。

当一个字节按数据位从高位到低位的顺序传输完后,紧接着从设备将拉低SDA线,回传给主设备一个应答位ACK(此时SDA线为高阻),此时才认为一个字节真正的被传输完成,如果一段时间内没有收到从机的应答信号,则自动认为从机已正确接收到数据。

多数从设备的地址为7位或10位,一般用7位。

八位设备地址=7位从机地址+读/写标志位

0表示主设备向从设备写数据

1表示主设备向从设备读数据

注:在起始信号后必须传送一个从机的地址(7位),1-7位为7位接收器件地址,第8位为读写位,“0”表示主机发送数据,“1”表示主机接收数据,第9位为ACK应答位,紧接着的为第一个数据字节,然后是一位应答位,后面继续第二个数据字节。

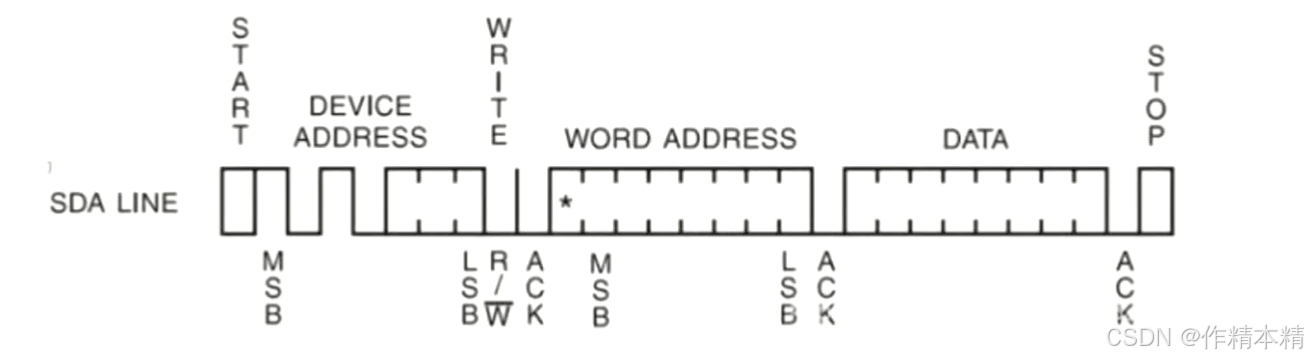

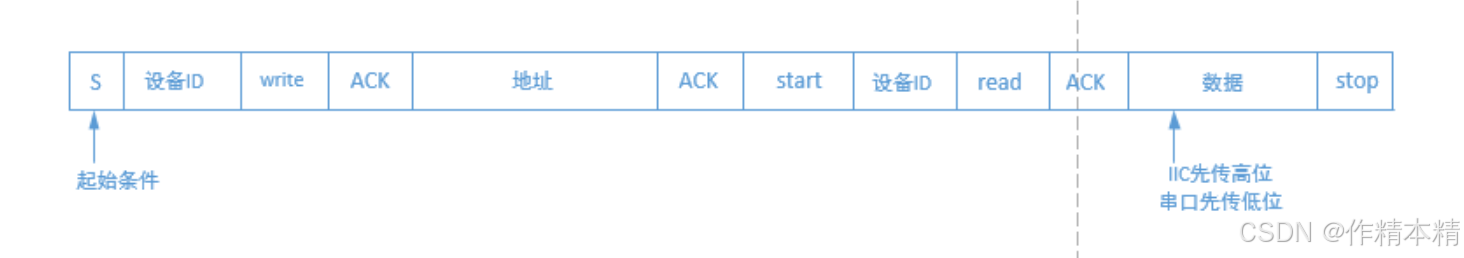

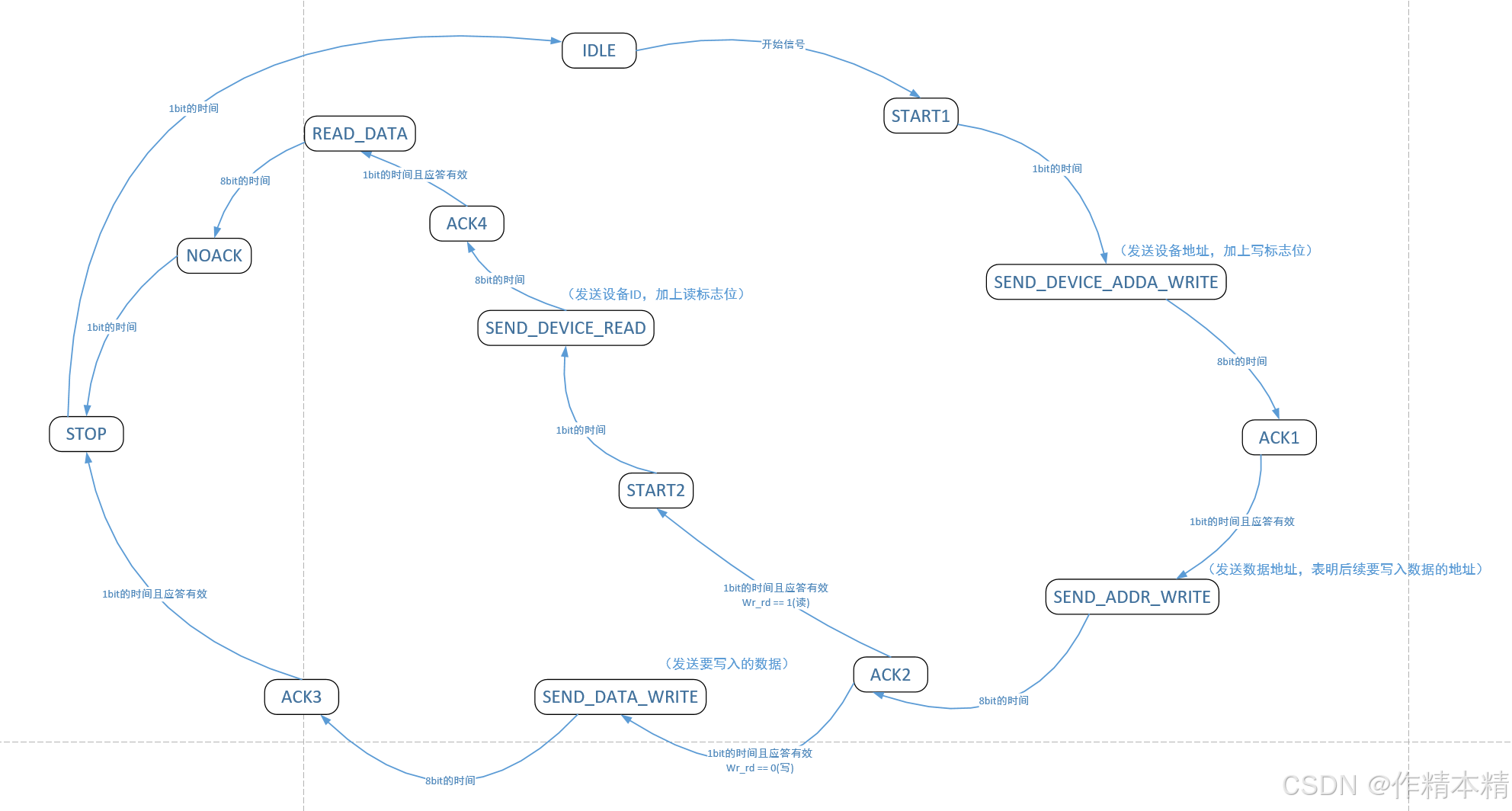

写:

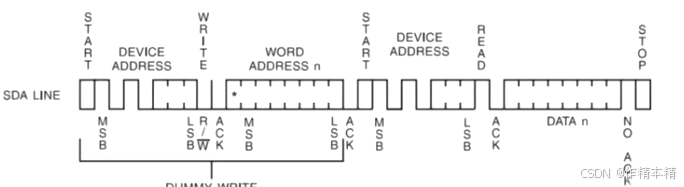

读: