为什么多比特数据跨时钟域时不能采用打两拍的方式处理?

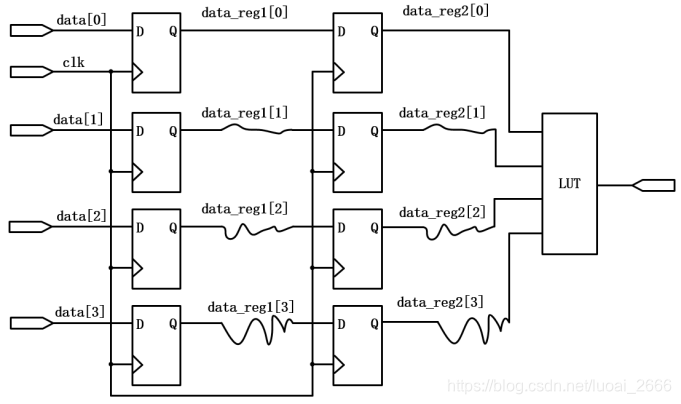

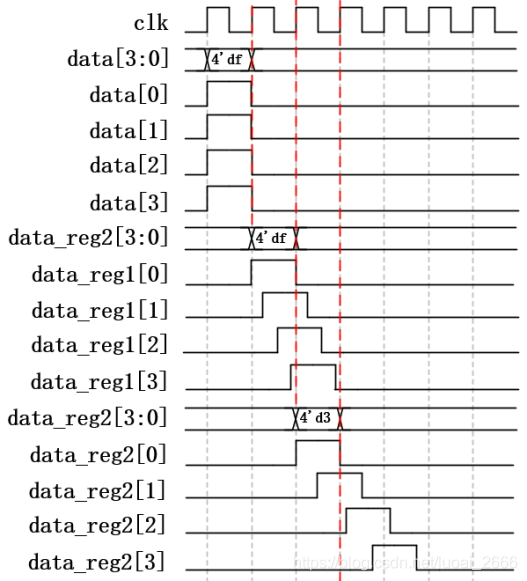

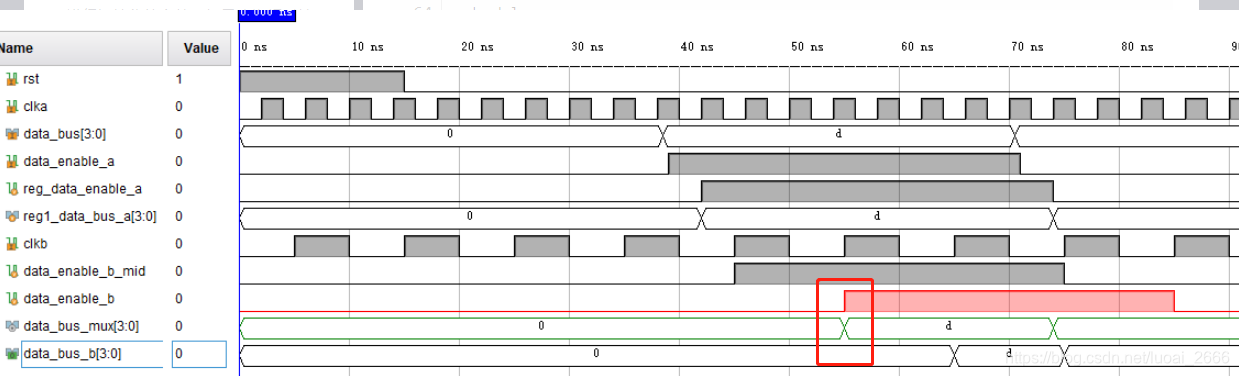

如下图所示,每个寄存器的位置不同,布局布线和逻辑的不同会导致每比特数据到达下一级寄存器的延时不同,而且延时会随着打拍数的增加、数据位宽的增加、时钟频率的增大而变得更加恶劣,所导致时钟采样的数据从最初的4’df变成4’d3,从而导致系统出错。

多比特数据跨时钟域的本质,最终也要转化成单比特跨时钟域来处理,对于MUX/DUMX我们知道通过对数据有效标志信号的同步,来间接实现数据的同步,那双口RAM和异步FIFO呢?对于双口RAM来说,通过读地址实现数据的同步,而读地址什么时候有效、什么时候自加需要有控制信号,这个控制信号就作为两边时钟域同步的桥梁,它往往是单比特的,判断写的状态,控制读的开始。而异步FIFO也是如此,异步FIFO通过另一种巧妙的设计,虽然数据是随机的,但是地址却是连续的,此时可以借助格雷码的特点通过同步2^n的地址来实现数据的同步,将地址转成成格雷码后就转换为仅变化一位的单比特跨时钟域情况,地址同步后,数据也就跟着同步了。

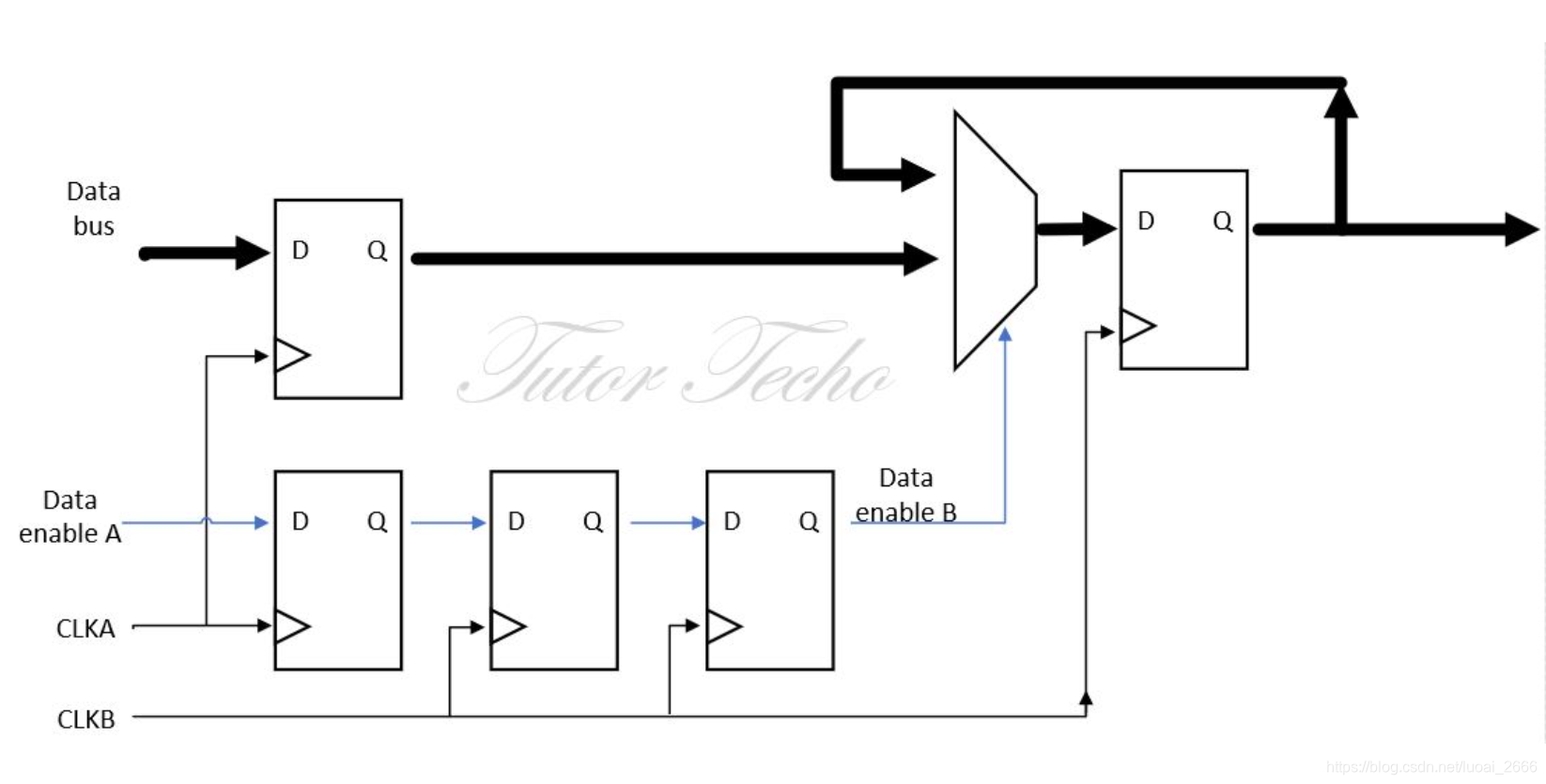

1 MUX同步器

场景:带数据有效标志信号的多比特数据做跨时钟域

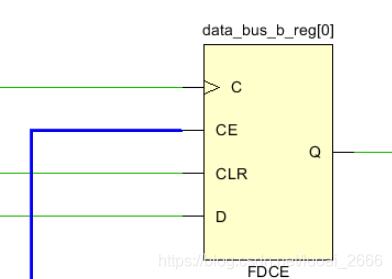

(1)对单比特的数据有效标志信号在clkB时钟域打两拍

(2)将同步后的数据有效标志信号作为多路选择器的选通信号,由于data enable A 的时序等同于 data bus,也就保证了 data bus已经对齐

//时钟域a下同步本地数据及其有效标志信号,改善时序

always@(posedge clka or posedge rst) begin

if(rst) begin

reg_data_enable_a <= 1'b0 ;

reg1_data_bus_a <= 4'd0 ;

end

else begin

reg_data_enable_a <= data_enable_a ;

reg1_data_bus_a <= data_bus ;

end

end

//将数据有效标志信号同步到b时钟域,两级同步器

always@(posedge clkb or posedge rst) begin

if(rst) begin

data_enable_b_mid <= 1'b0 ;

data_enable_b <= 1'b0;

end

else begin

data_enable_b_mid <= reg_data_enable_a;

data_enable_b <= data_enable_b_mid;

end

end

assign data_bus_mux = data_enable_b ? reg1_data_bus_a : data_bus_b;

always@(posedge clkb or posedge rst) begin

if(rst) begin

data_bus_b <= 4'b0;

end

else begin

data_bus_b <= data_bus_mux;

end

end

其实MUX充当的作用就是触发器的一个使能信号。判断源时钟域的单比特信号是否在目的时钟域成功同步,如果是,那么这个时间长度下多比特信号也可以同步过来,而不违背建立时间。

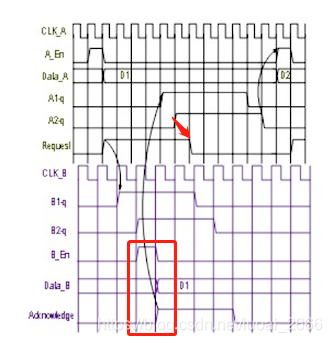

2 握手同步

场景:带en脉冲信号的多比特数据做跨时钟域

本质上和单bit握手同步一样,A_EN和B_EN就是单bit信号。当B_EN同步之后,Data也就同步了。不同之处在于CLKB的ACK信号由B2_q换成了下图中的ACK,显然是因为收到了Data_B才能反馈。

缺点:实现较为复杂,效率不高,在对设计性能要求较高的场合应该慎用。

3 格雷码

场景:连续变化的多bit信号

将CLKA的数据转为格雷码,然后再将此格雷码进行打两拍,之后在CLKB将格雷码恢复成原始数据。

assign Gray = (Bin >> 1) ^ Bin;

always @ (*)begin

Bin[length-1]=Gry[length-1];

for(i=length-2;i>=0;i=i-1)

Bin[i]=Bin[i+1]^Gry[i];

//感觉这样的组合逻辑很长,有没有优化的方法?

end

4 格雷码+异步双口RAM

场景:无限制。尤其在有大量的数据需要进行跨时钟域传输, 并且对数据传输速度要求比较高的场合 。

假设我们现在有一个信号采集平台,ADC芯片提供源同步时钟60MHz,而FPGA内部需要使用100MHz的时钟来处理ADC采集到的数据。

需要100MHz的时钟对RAM的写地址进行判断,当写地址大于某个值之后再去读取RAM。

将RAM的写地址转为格雷码,然后再将写地址的格雷码进行打两拍,之后再在RAM的读时钟域将格雷码恢复成原始地址。

5 异步FIFO

等于上面的。

一个异步 FIFO 一般由如下部分组成:

1. Memory, 作为数据的存储器;

2. 写逻辑部分,主要负责产生写信号和地址;

3. 读逻辑部分,主要负责产生读信号和地址;

4. 地址比较部分,主要负责产生 FIFO 空、满的标志。