组合逻辑回路(combinational loop)经常是由于组合逻辑输出经过一定的组合逻辑电路后再次回到原组合逻辑输入端的情况,在整个回路中没有任何时序逻辑。

在具体的电路设计中应该尽量避免组合逻辑回路的出现,如果电路中出现组合逻辑回路可能会导致以下情况出现:

- 电路可能陷入死锁状态,并且会以很高的频率形成振荡电路,并且其时序和功能行为依赖于逻辑门和线延迟,不同的库实现将会导致不同的结果,影响设计功能的正确性;

- 组合逻辑回路会降低ATPG(Automatic Test Pattern Generation)能达到的故障覆盖率,增加了控制组合逻辑回路路径的难度;

- 如果组合逻辑回路在设计中被作为锁存器,那么设计就需要利用ASIC供应商的库把组合逻辑回路中的对应功能单元转换成等效的锁存器,那么不同的供应商对应的锁存器可能会不同,即电路单元转换也可能不同;

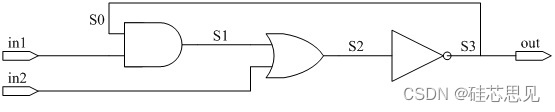

【示例】下图为一个典型的组合逻辑回路的电路原理图:

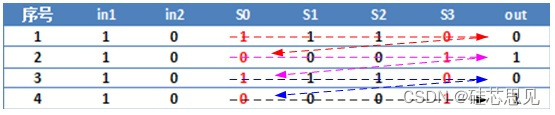

仿真死锁序列如下表:

当输入为in1和in2的取值如上表所示,且电路中各连线的初始态如表格第一行所示,当电路上电后,电路将按照序号“1->2->3->4....”不断地反复循环,前仿真阶段电路将进入死锁环,仿真时间将不向前推进,即仿真器时间将保持不变,仿真波形也不会再表现出任何变化。当物理实现后,因为元件间存在连线延迟,具体的连线延迟不同,该部分电路将处于震荡中。

推荐使用以下工具进行代码规则的检查:

Synopsys:Leda,SpyGlass,nLint

Cadence:HAL