状态机verilog例程

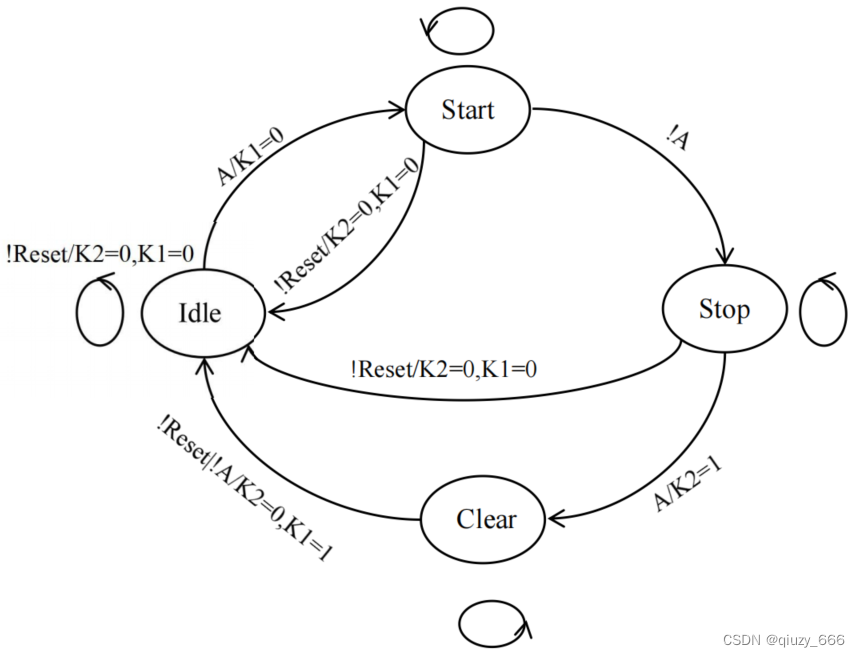

上图所示的状态转移图表示了一个4状态的有限状态机,同步始终为clk,输入信号是A和Reset,输出信号是K2和K1,状态转移在同步始终clk的上升沿发生,由Reset和A的状态决定状态的转移。

verilog实现设计代码如下:

module at7(Clock,Reset,A,K2,K1);

input Clock,Reset,A;

output K2,K1;

reg K2,K1;

reg[1:0] state,nextstate;

//定义状态机的四个状态

parameter

Idle = 2'b00,

Start = 2'b01,

Stop = 2'b10,

Clear = 2'b11;

//同步时钟下的状态转移设置

always @(posedge Clock)

if(!Reset) state <= Idle;

else state <= nextstate;

//产生下一个状态的组合逻辑

always @(state or A)

case(state)

Idle: if(A) nextstate = Start;

else nextstate = Idle;

Start: if(!A) nextstate = Stop;

else nextstate = Start;

Stop: if(A) nextstate = Clear;

else nextstate = Stop;

Clear: if(!A) nextstate = Idle;

else nextstate = Clear;

default: nextstate = 2'bxx;

endcase

//产生输出K1的组合逻辑

always @(state or Reset or A)

if(!Reset) K1 = 0;

else if(state == Clear && !A) K1 = 1;

else K1 = 0;

//产生输出K2的组合逻辑

always @(state or Reset or A)

if(!Reset) K2 = 0;

else if(state == Stop && A) K2 = 1;

else K2 = 0;

endmodule

测试代码如下:

`timescale 1ns / 1ps //定义时间基本单位以及时间精度

//声明输入输出信号

module sim_at7();

reg a;

reg clock,rst;

wire k2,k1;

at7 uut_at7(

.Clock(clock),

.Reset(rst),

.A(a),

.K2(k2),

.K1(k1)

);

initial

begin

a = 0;

rst = 1;

clock = 0;

#20 rst = 0;

#120 rst = 1;

end

always #50 clock = ~clock; //产生周期脉冲信号

//在clock时钟上升沿,每隔固定单位时间随机生成a

always @ (posedge clock)

begin

#30 a = {$random} % 2; //a的值在0和1之间随机产生

#180;

end

endmodule

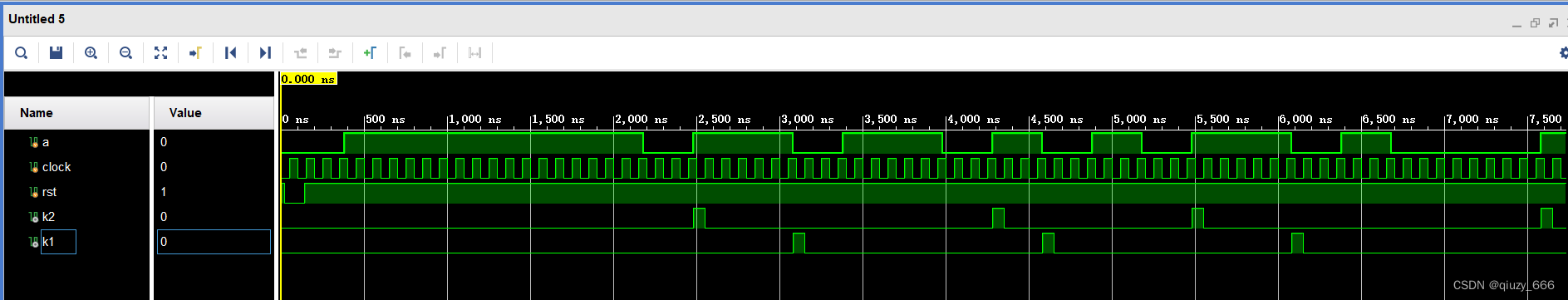

调试波形如下: