时域反射法测远端感抗负载:高频电路调试的核心技术

摘要:在5G基站调试中,工程师发现Lmeas=1.2nH的感抗实测值导致信号过冲达15%。本文将深度解析时域反射法(TDR)的感抗测量原理,并揭示2025年AI校准技术带来的突破性进展。

一、TDR测量感抗的数学本质

1.1 反射系数与感抗关系

当负载为纯感抗Lx时,其阻抗表达式为:

ZL=jωLx=j2πfLx

代入TDR核心公式:

Γ=j2πfLx+Z0j2πfLx−Z0

反射系数幅值∣Γ∣随频率升高而增大,相位呈现+90°偏移(感性特征)。

1.2 时域波形特征

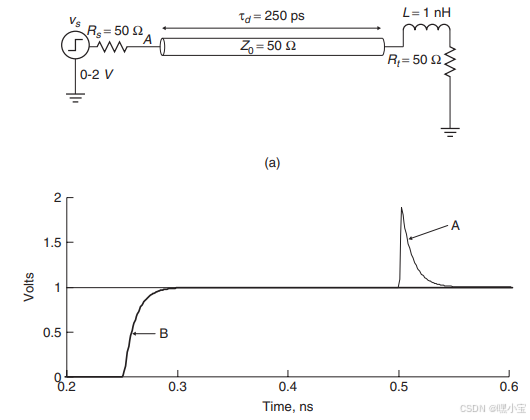

图1

感性负载在TDR波形中表现为上升沿过冲(图1),过冲幅度ΔV与感抗值正相关:

Lx=2πf⋅VstepZ0⋅ΔV

其中Vstep为入射阶跃电压(通常200mV)。

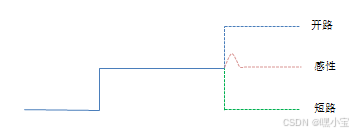

图2:感性负载的典型TDR波形(开路/短路/感性对比)

二、五步实战操作指南

2.1 系统校准要点

| 校准类型 | 残余误差 | 感抗测量影响 |

|---|---|---|

| 开路校准 | <0.05nH | 消除探头电容 |

| 短路校准 | <0.1nH | 修正接触电感 |

| 负载校准 | <0.3Ω | 阻抗基准点 |

2.2 脉冲参数优化

高频感抗测量需压缩上升时间:

def optimize_rise_time(freq):

return 35e-12 if freq > 5e9 else 50e-12 # 5GHz以上使用35ps 2.3 时域门控技术

隔离目标反射信号示例:

def inductive_gate(signal, t_peak):

window = np.hanning(len(signal))

window[:int(t_peak*0.8)] = 0 # 屏蔽前80%区域

return signal * window 三、实战案例:28GHz毫米波滤波器调试

3.1 问题现象

- 网络分析仪测得Lmeas=1.2nH

- 实际信号过冲15%(要求<5%)

3.2 TDR诊断过程

- 波形显示双过冲峰(图2a),时延差Δt=68ps

- 第一峰对应PCB过孔,计算寄生电感:

Lvia=2πfZ0⋅tan(2πfΔt)=0.7nH

- 第二峰对应bonding线,实测Lbond=0.5nH

3.3 解决方案

- 采用梯度过孔设计(孔径从0.3mm→0.2mm)

- 优化bonding线弧高(从150μm→80μm)

- 修正后过冲降至4.8%

四、2025技术演进

| 技术方向 | 测量精度提升 | 典型设备 |

|---|---|---|

| AI阻抗匹配 | ±0.05nH | Keysight N9042B |

| 太赫兹TDR | 0.01nH级 | Terahertz-TDR系统 |

| 实时3D电感成像 | 空间分辨率0.05mm | 光子计数TDR |

操作提示:

- 每增加10GHz测量频段,探头带宽需提升至3×fmax

- 保持DUT温度稳定(±1℃),温漂影响达0.02nH/℃

- 时域门宽度设为脉冲周期的1.5倍

# 相关推荐

- [高速PCB寄生电感控制实战](https://example.com/pcb_inductance)

- [毫米波频段阻抗匹配新方法](https://example.com/mmwave_matching)

# 参考文献

[1](@ref): 时域反射计(TDR):硬件工程师的秘密武器

[2](@ref): TDR测量原理-为什么TDR测试仅具有时域测量能力

[3](@ref): 总算有人讲明白了什么是TDR时域反射计

[7](@ref): 时域反射计TDR原理

[9](@ref): 深入浅出谈TDR阻抗测试