计算机组成原理重要知识点摘录(考研用)——第五章:中央处理器

本文参考于《2021年计算机组成原理考研复习指导》(王道考研),《计算机组成原理》

控制器由程序计数器(PC)、指令寄存器(IR)、指令译码器、存储器地址寄存器MAR、存储器数据寄存器MDR、时序系统和微操作信号发生器等组成

一个完整的指令周期应包括取指、间址、执行和中断4个周期

中断周期中的进栈操作是将SP减1,这和传统意义上的进栈操作相反,原因是计算机的堆栈中都是向低地址增加,所以进栈操作是减1而不是加1

机器周期可看作是所有指令执行过程中的一个基准时间,机器内的各种操作大致可归属为对CPU内部的操作和对主存的操作两大类,由于CPU内部的操作速度较快,CPU访存的操作时间较长,因此通常以访问一次存储器的时间定为基准时间较为合理,这个基准时间就是机器周期。 因此在存储字长等于指令字长的情况下,取指周期也可看作机器周期。

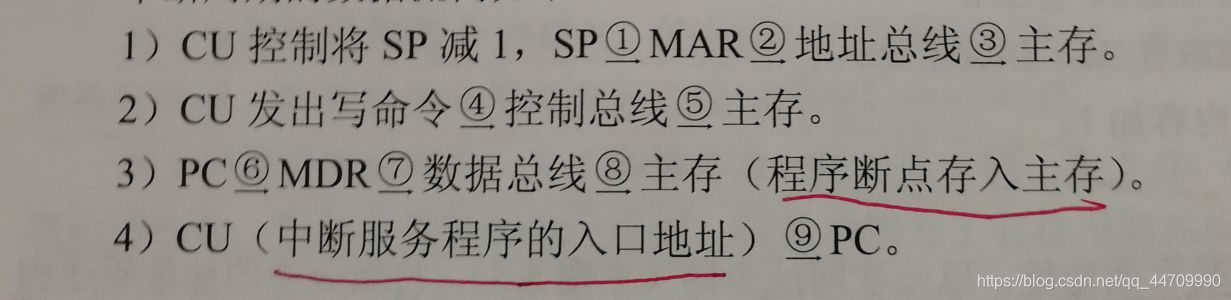

中断周期的数据流向如下:

3.执行算术或逻辑运算

执行算术或逻辑操作时,由于ALU本身是没有内部存储功能的组合电路,因此如要执行加法运算,相加的两个数必须在ALU的两个输入端同时有效。 暂存器Y即用于该目的。先将一个操作数经CPU内部总线送入暂存器Y保存,Y的内容在ALU的左输入端始终有效,再将另一个操作数经总线直接送到ALU的右输入端。 这样两个操作数都送入了ALU,运算结果暂存在暂存器Z中。 (设置暂存器Z的原因是:ALU的输出不能直接与内部总线相连,因为其输出又会通过总线反馈到ALU的输入,影响运算的正确性)

Ad(IR)——>Bus——>MAR MDRout和MARin有效

1——>R CU发读命令

MEM——>数据线——>MDR 操作数从存储器——>数据线——>MDR

MDR——>Bus——>Y MDRout和Yin有效,操作数——>Y

(ACC)+(Y)——>Z ACCout和ALUin有效,CU向ALU发加命令,结果——>Z

Z——>ACC Zout和ACCin有效,结果——>ACC

(2