本工程实现调用ZYNQ-7000的内部ARM处理器,通过UART给电脑发送字符串。

硬件:正点原子领航者-7020

开发平台:Vivado 2018、 SDK

1 Vivado部分操作

1.1 新建工程

设置工程名,选择芯片型号。

1.2 添加和配置PS IP

点击IP INTEGRATOR,Create Block Design。

1.2.1添加IP

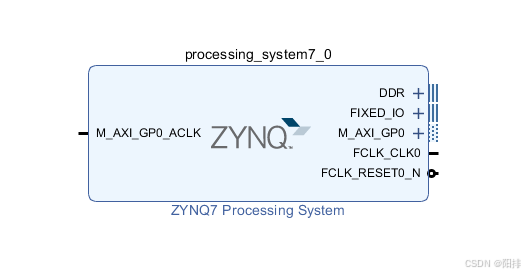

添加ZYNQ7 Processing System。

1.2.2 配置PS

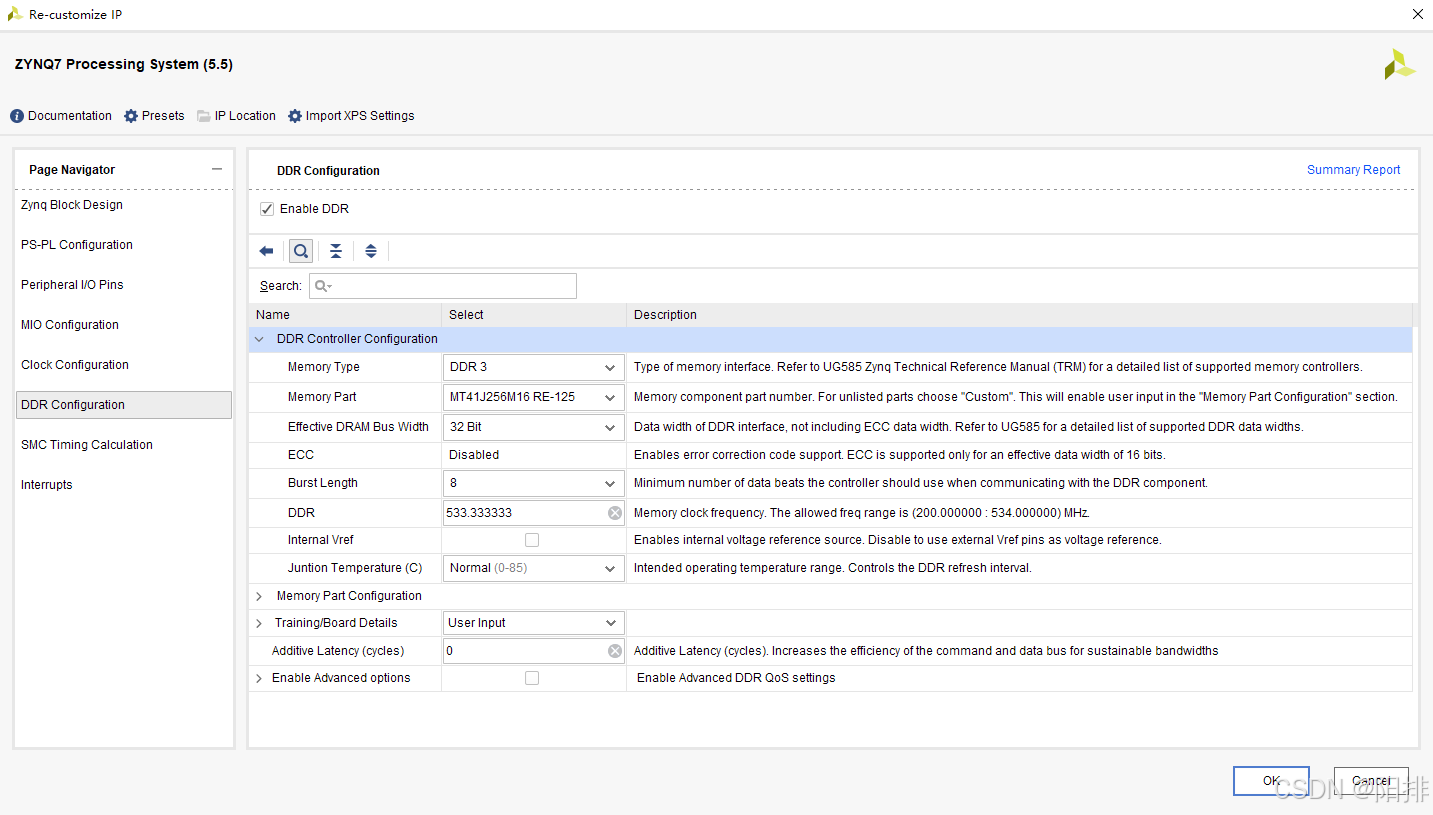

- 修改DDR Configuration:

- 7020选择MT41J256M16 RE-125(256M162=8190Mbit=8Gbit)两片DDR3,位宽16,深度256M

- 7010选择MT41J128M16 HA-125 (128M162=4096Mbit=4Gbit)两片DDR3,位宽16,深度128M

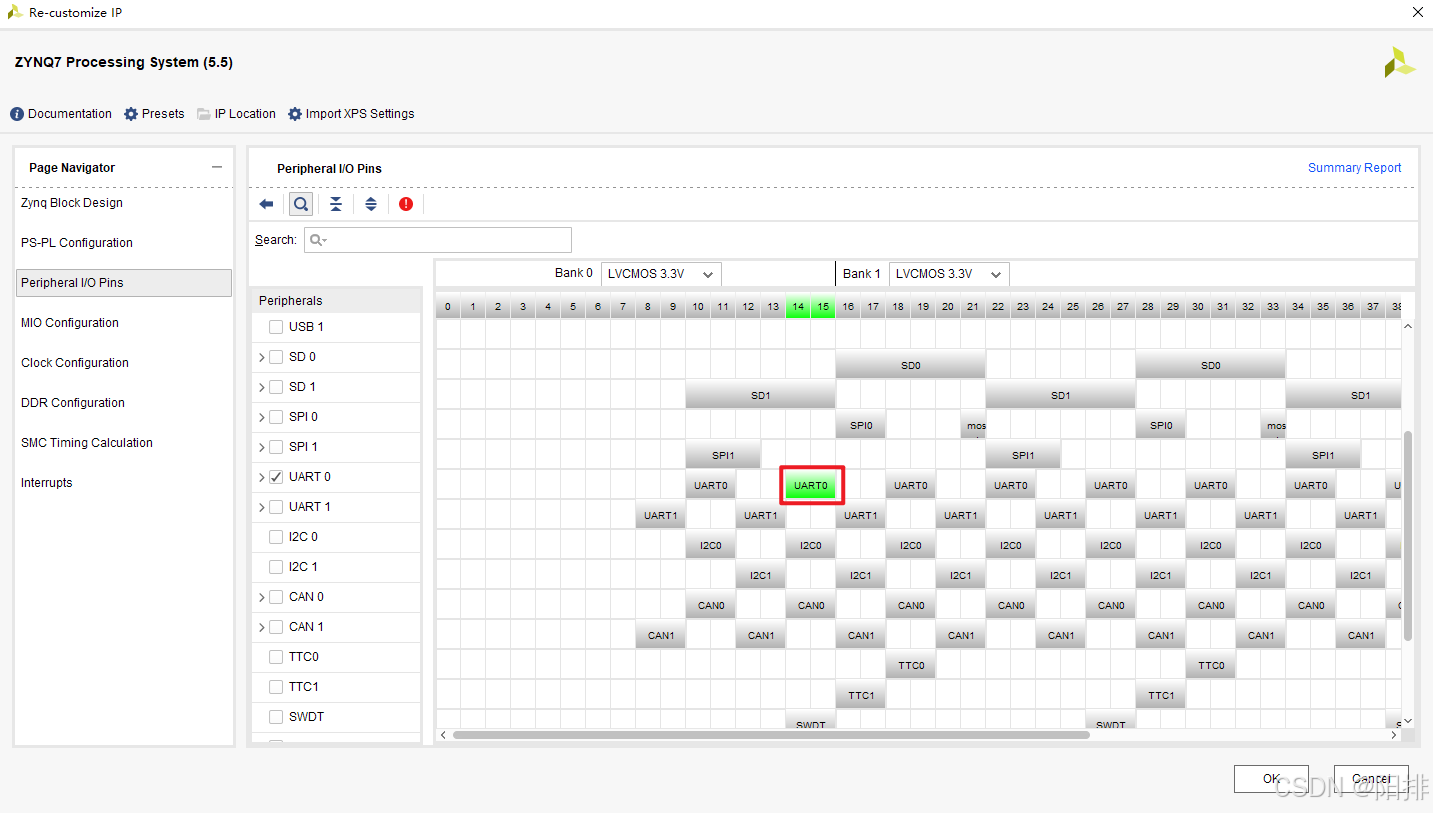

- 选择外设引脚Peripheral I/O Pins:

由于入门教程需要使用串口输出“Hello World”,因此只要选择UART。

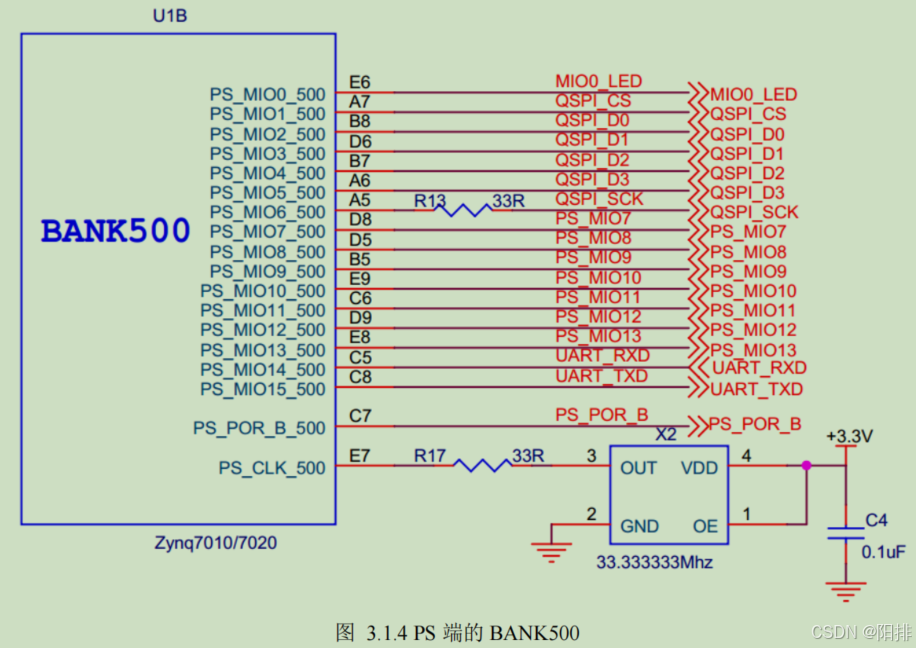

由于开发板硬件设计如上图所示:串口输出的引脚已经对应好了,为PS_MIO14_500和PS_MIO15_500。

查看设置界面,只能选择UART0行的第二个UART0。

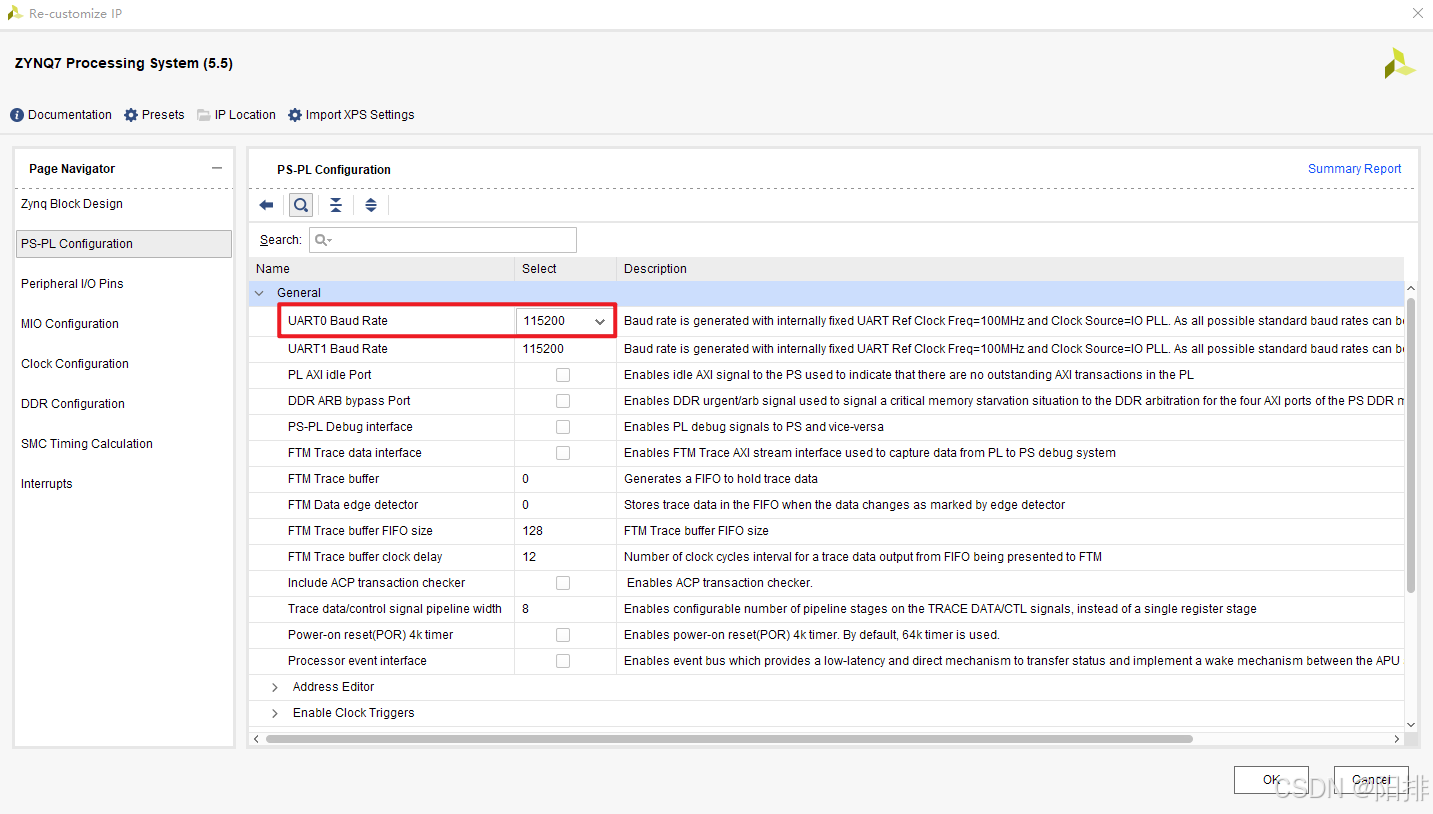

- 设置 PS-PL Configuration:

UART0串口波特率任意设置,一般为9600、115200。

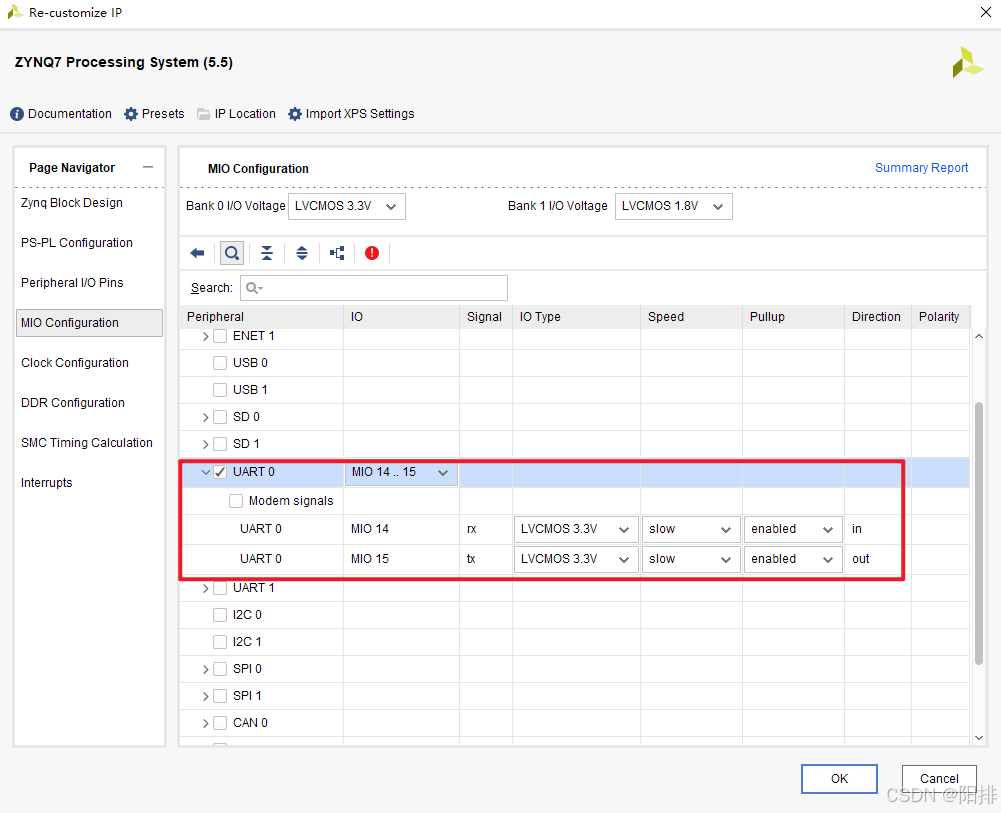

- 设置MIO Configuration:

设置串口引脚的电平和速度。

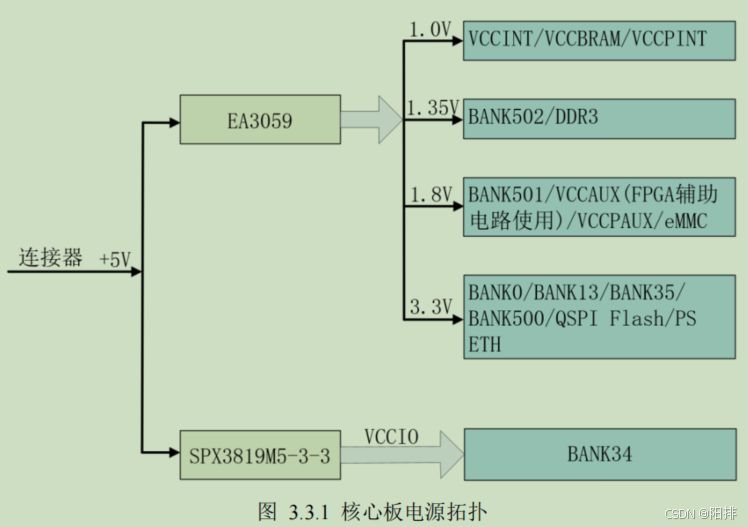

查看原理图或电源拓扑,可以看到BANK500的电源电压为3.3V,BANK501的电源电压为1.8V。

因此设置BANK0为LVCMOS 3.3V,BANK1为LVCMOS 1.8V。

- 配置完成,点击OK。

1.2.3 关闭不需要的接口

由于是初始工程,大部分接口是不需要的,包括:M_AXI_GP0_ACLK、M_AXI_GP0、FCLK_CLK0、FCLK_RESET0_N。

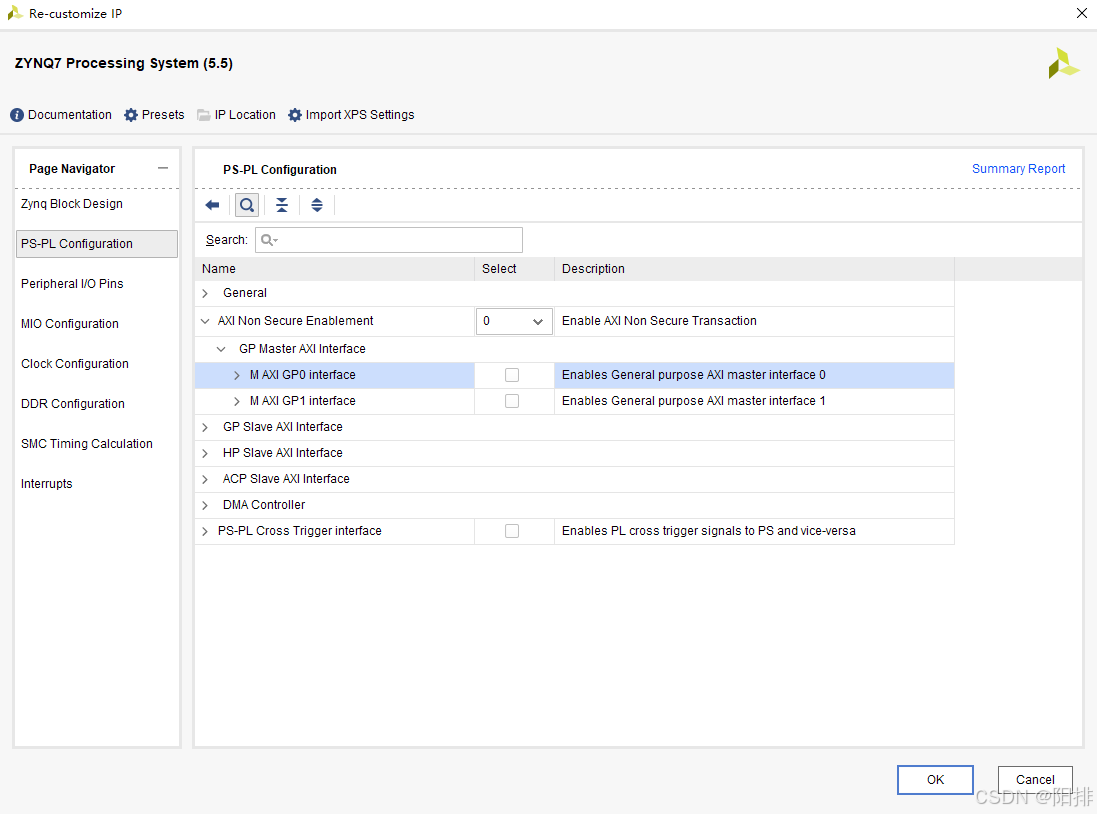

- 关闭AXI接口:接口双击进入PS配置界面,选择

PS-PL Configuration->AXI Non Secure Enablement->GP Master AXI Interface,取消勾选M AXI GP0 interface。

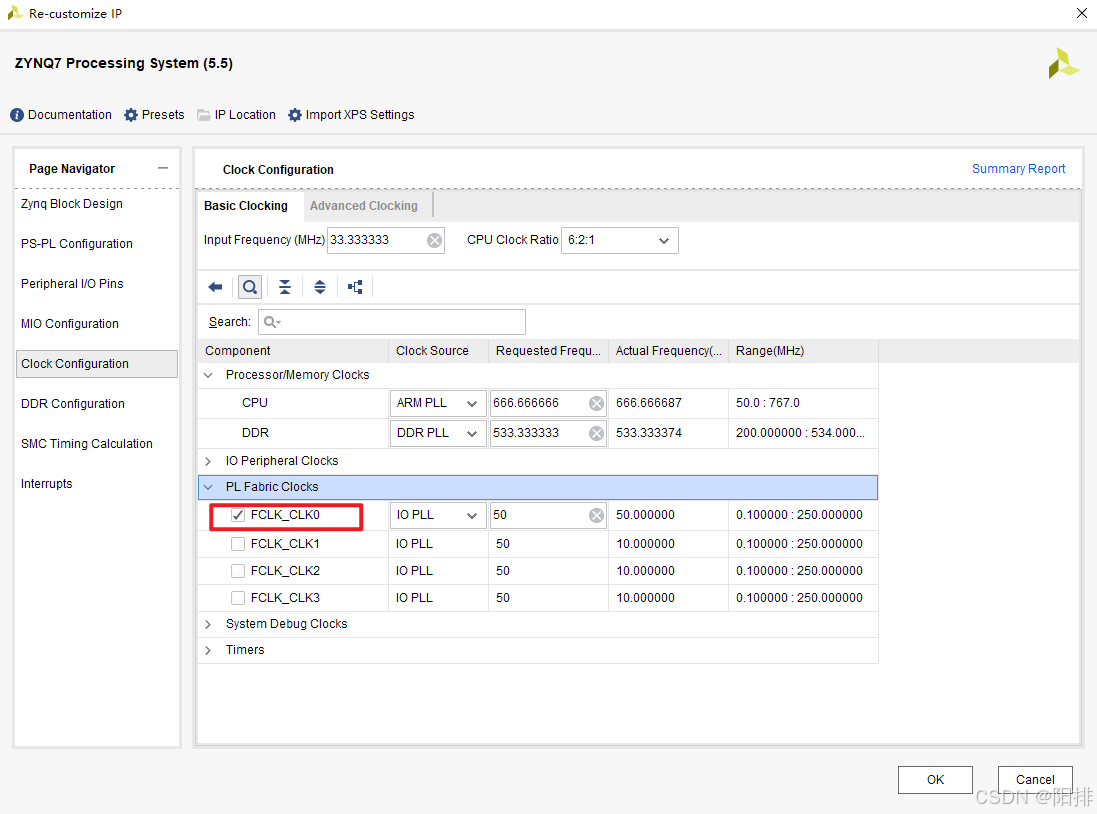

- 关闭CLK接口:进入

Clock Configuration->PL Fabric Clocks,取消勾选FCLK_CLK0。

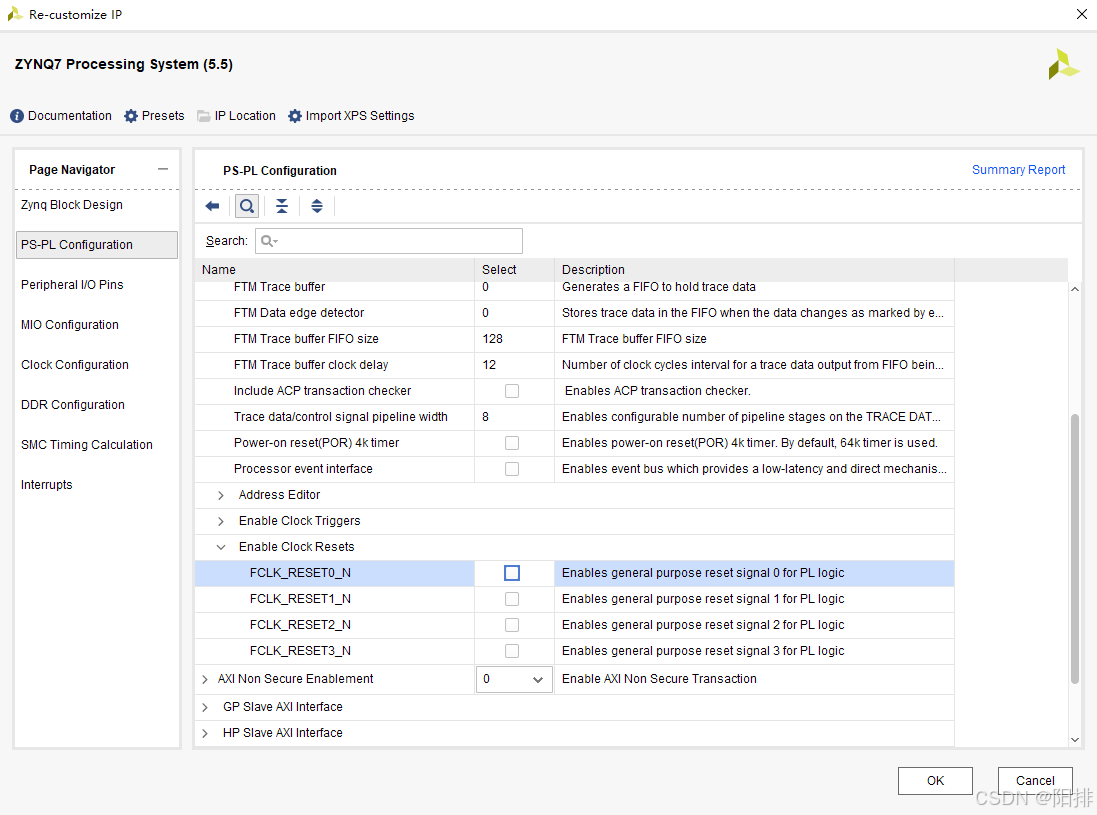

- 关闭RESET接口:进入

PS-PL Configuration->General->Enable Clock Resets,取消勾选FCLK_RESET0_N。

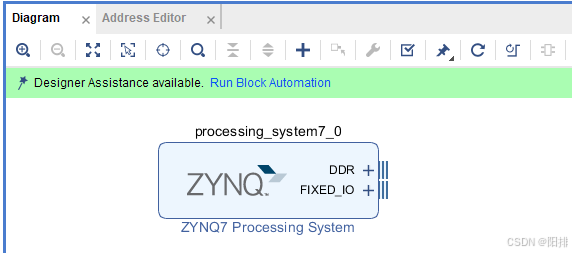

多余接口都关闭,可以得到如下模块:

1.2.4 生成连接和验证

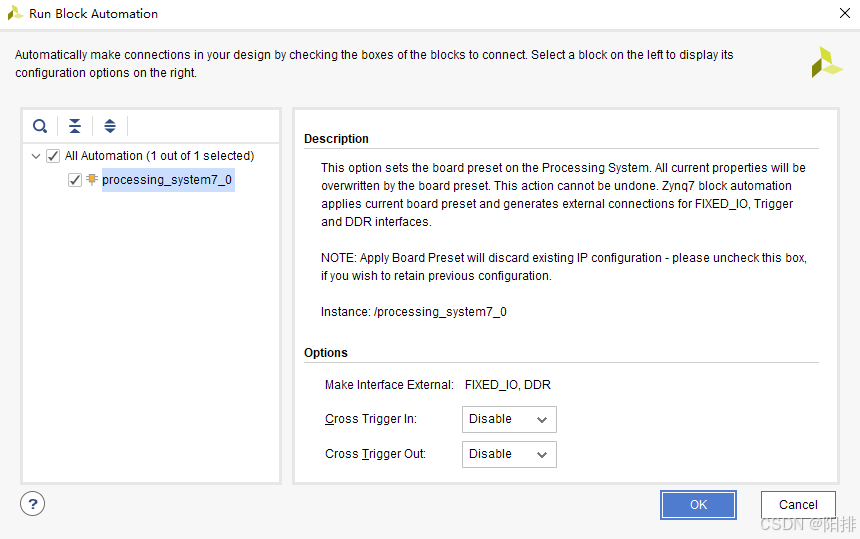

- 自动化连接:

点击Run Block Automation,进入界面,选中模块,点击OK。

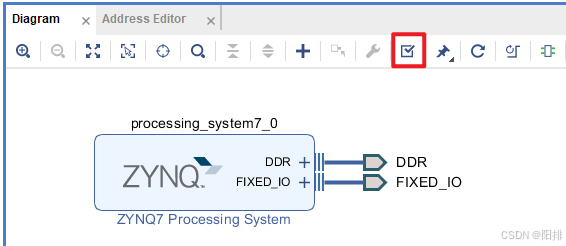

模块会自动生成引脚,连接外部DDR3和串口引脚。

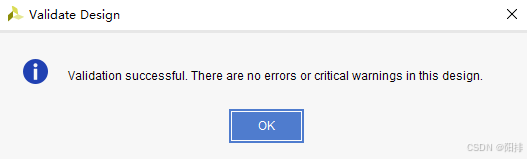

- 验证:

点击Validate Design,自动验证模块是否有错误或警告。

1.3 生成子模块和顶层文件

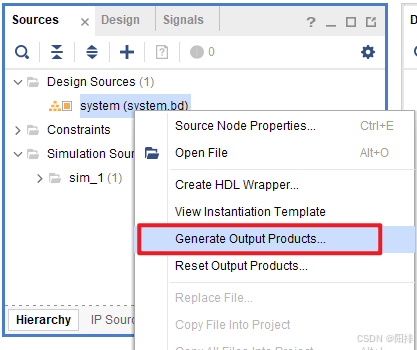

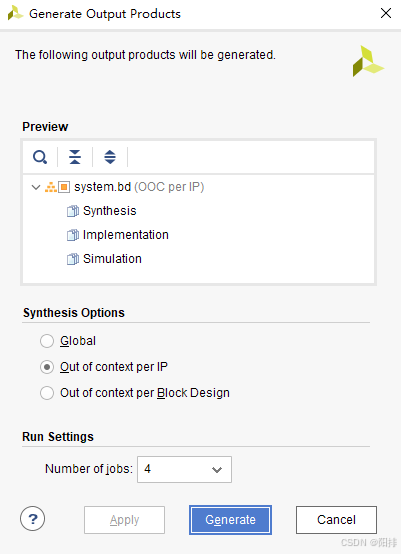

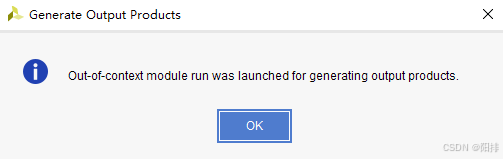

- 生成子模块:

右键IP,Generate Output Products,对模块进行综合和约束。

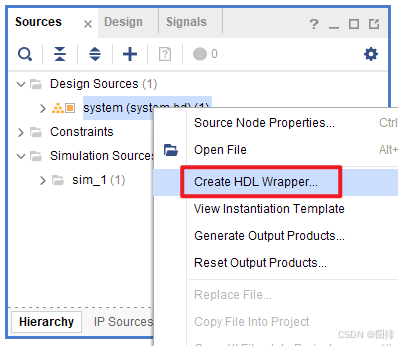

- 创建顶层文件:

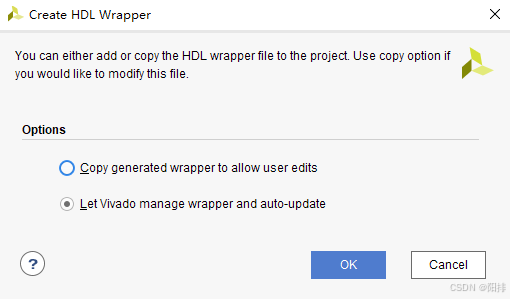

右键IP,Create HDL Wrapper。

选择第二个Let Vivado manage wrapper and auto-update。如果修改IP内部细节,Vivado会自动修改外部接口等。

- 由于本工程内没有用到PL部分,只有PS部分,因此不需要

Generate Bitstream,直接可以导出硬件。

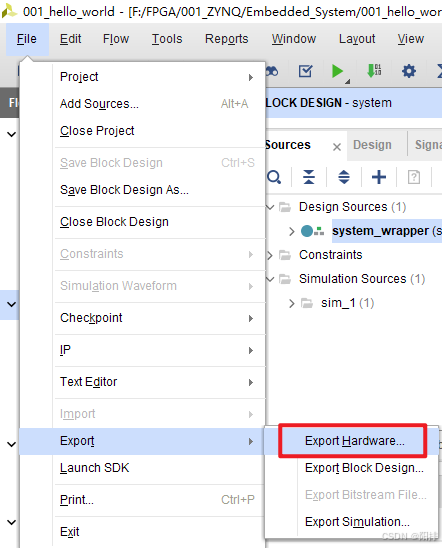

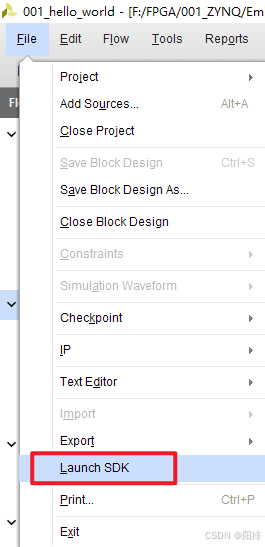

1.4 导出硬件

- 导出硬件:

点击菜单栏File->Export->Export Hardware。

此处不需要选择Include bitstream,其他工程如果用到了PL部分,那就需要选择。

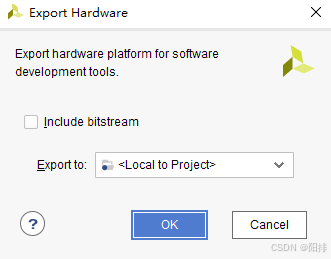

- 以上操作会在工程目录下新建一个.sdk文件夹,内部有一个

system_wrapper.hdf文件,该文件可以用解压软件打开,内部包括*.c、*.h等文件。

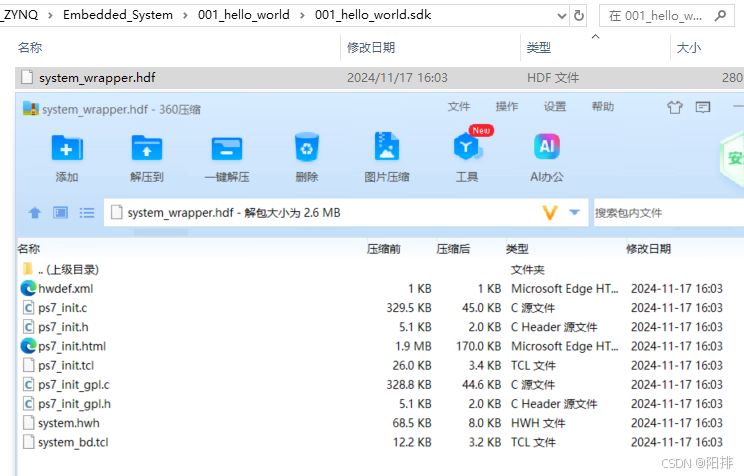

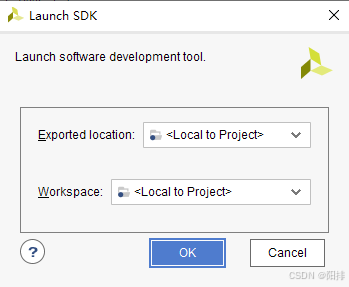

- 打开SDK:

菜单栏File->Launch SDK。

点击OK。

2 Software Development Kit部分操作

软件基于Eclipse开发,以下就是进行C语言的编写。

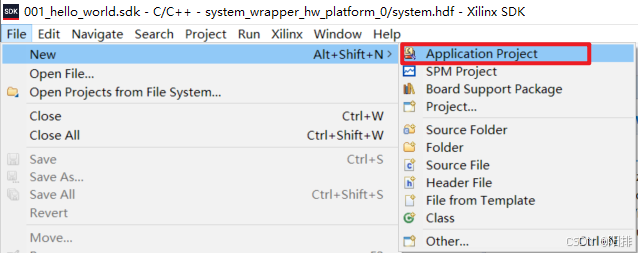

2.1 新建工程

-

点击

File->New->Application Project。

-

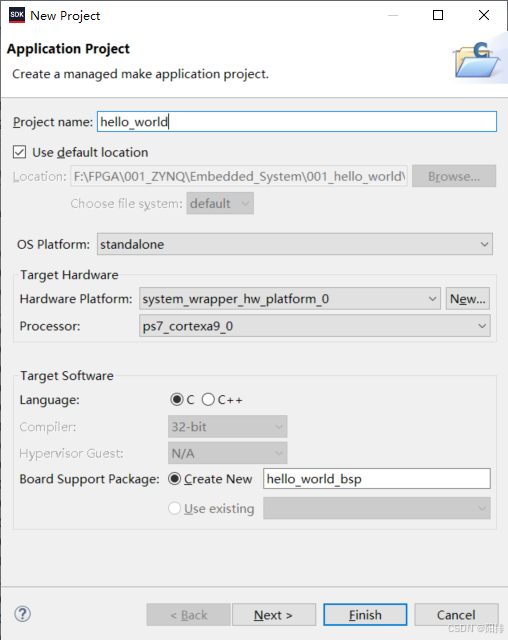

设置工程信息:

添加工程名,然后点击Next。

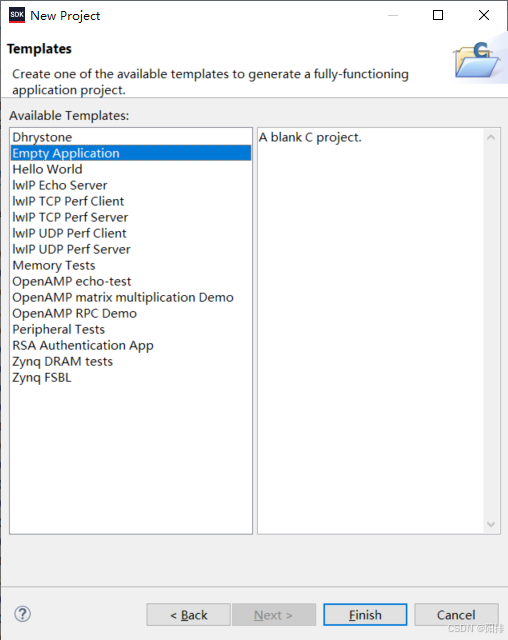

- 选择

Empty Application,点击Finish。

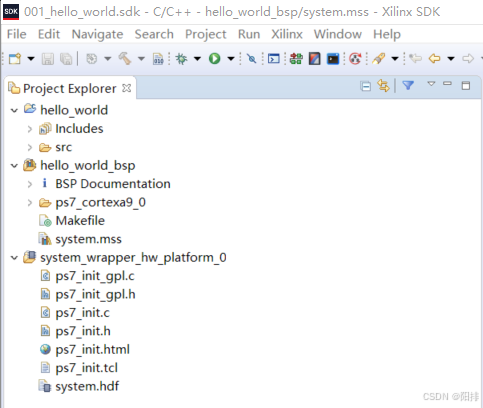

- 可以看到SDK界面的Project Explorer中生成了两个文件夹hello_world和hello_world_bsp。

- hello_world:存放自己编写的软件。

- hello_world_bsp:存放板级支持包,相当于硬件驱动,作为硬件和软件之间的桥梁。

- system_wrapper_hw_platform_0:存放系统硬件信息。

2.2 编写软件

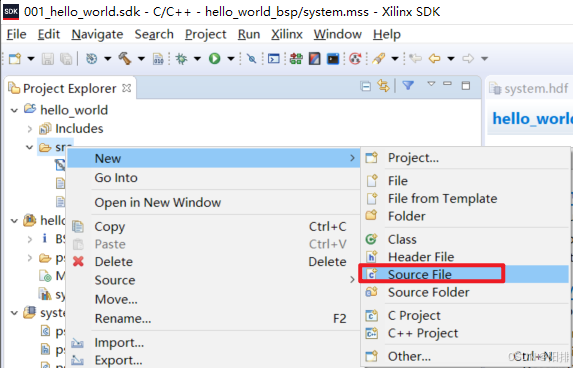

-

创建工程文件:

右键hello_world->src,New->Source File,新建文件名必须为main.c。

-

编写并保存

main.c

/*

* main.c

*

* Created on: 2024年11月17日

* Author: win10

*/

#include "stdio.h"

int main(){

printf("hello world\n");

return 0;

}

保存后会自动编译,如果编译错误,会在界面底部Problems中报错。

- 通过编译之后,即可将软件烧录到FPGA中。

2.3 FPGA板配置

由于FPGA板设计时PL和PS的UART共用了同一个串口芯片,因此,需要修改跳线帽到PS端。

连接JTAG调试线,电源线和USB_UART的TYPE-C线。

2.4 连接串口

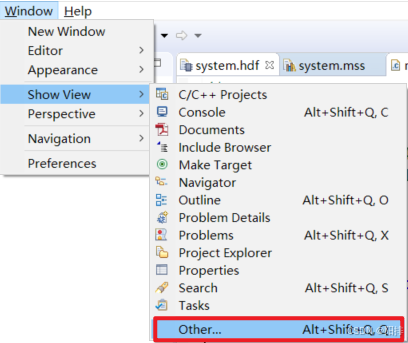

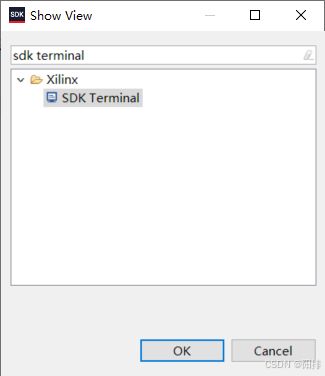

- 找到SDK Terminal:Window->Show View -> Other

输入关键词,选择对应窗口,点击OK。

- 由于上一步已经连接串口,此时可以通过SDK Terminal连接。

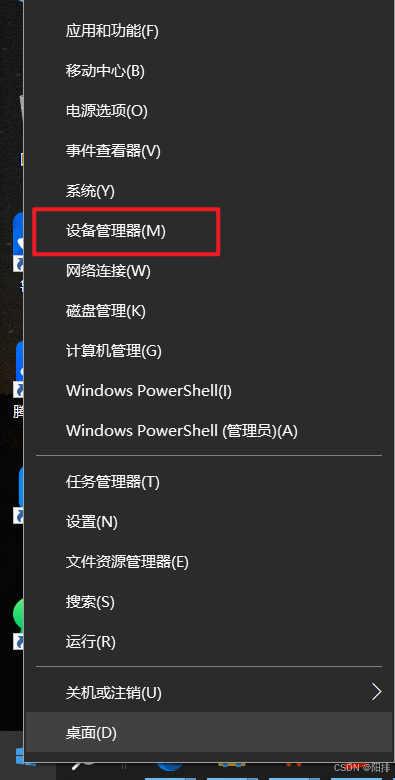

(1)打开电脑设备管理器,查看COM口。

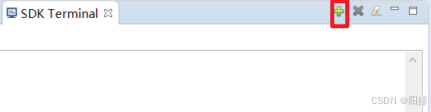

(2)点击加号连接串口。

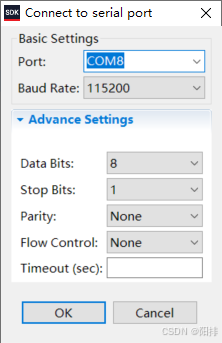

选择对应串口号,设置波特率,其他默认。

如果显示以下信息,则说明连接成功。

Connected to COM8 at 115200

2.4 下载程序

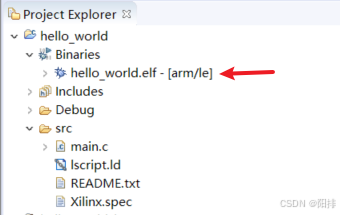

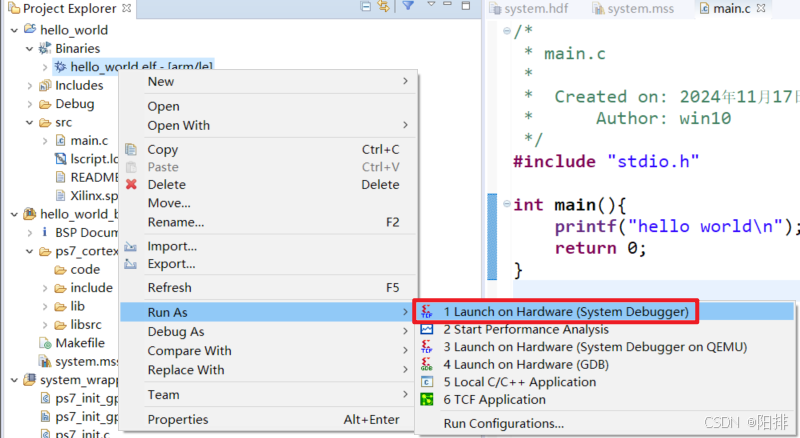

由于刚才保存的时候,系统已经自动编译了.elf文件,可以从左侧hello_world,Binaries目录看到。

右键.elf文件,选择Run As -> 1 Launch on Hardware (System Debugger)。

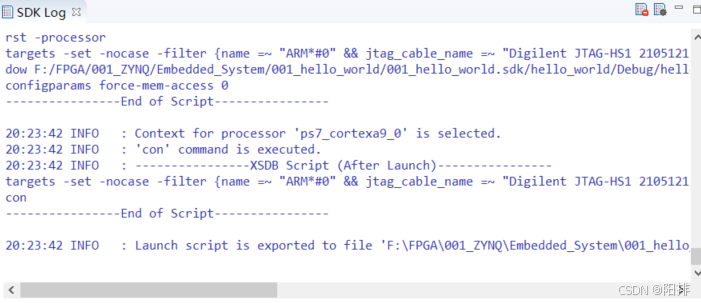

SDK log输出:

串口输出结果:

Connected to COM8 at 115200

口

Connected to COM8 at 115200

9莌ello world

Connected to COM9 at 115200

hello world

本结果进行多次尝试,前面数据错误,可能与USB线的质量和信号干扰有关。