作者的开发板: STM32L431(Cotex-M4)

开发环境: Keil5 MDK+ STM32CubeMX

官方例程+源码: UCOSIII 3.04.zip - 蓝奏云

第一步使用CubeMX生成一个HAL库的Keil工程

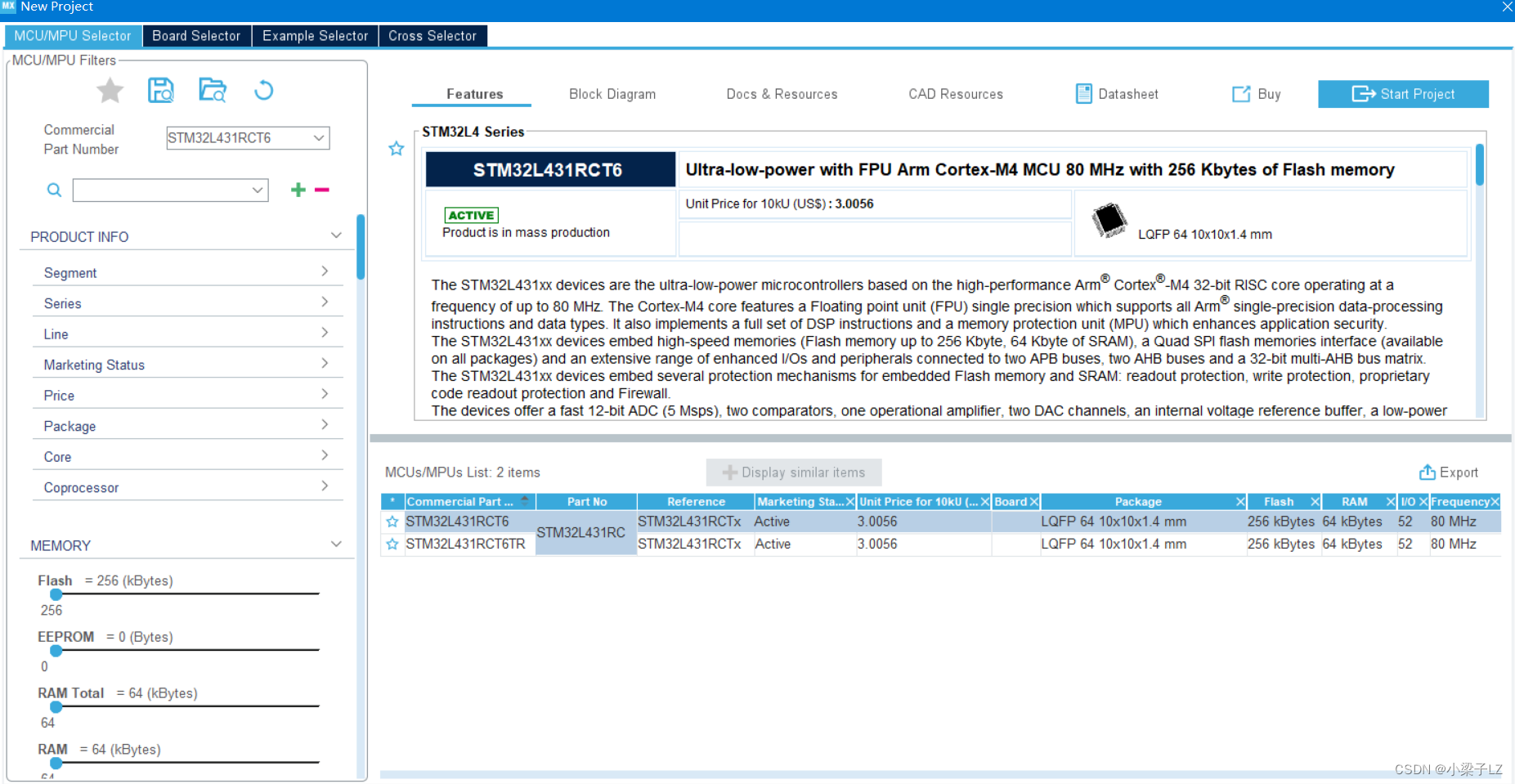

选择芯片,作者是STM32L431,兄弟们根据自己的芯片选择就好,选择好后点击右上角的Start Project创建工程

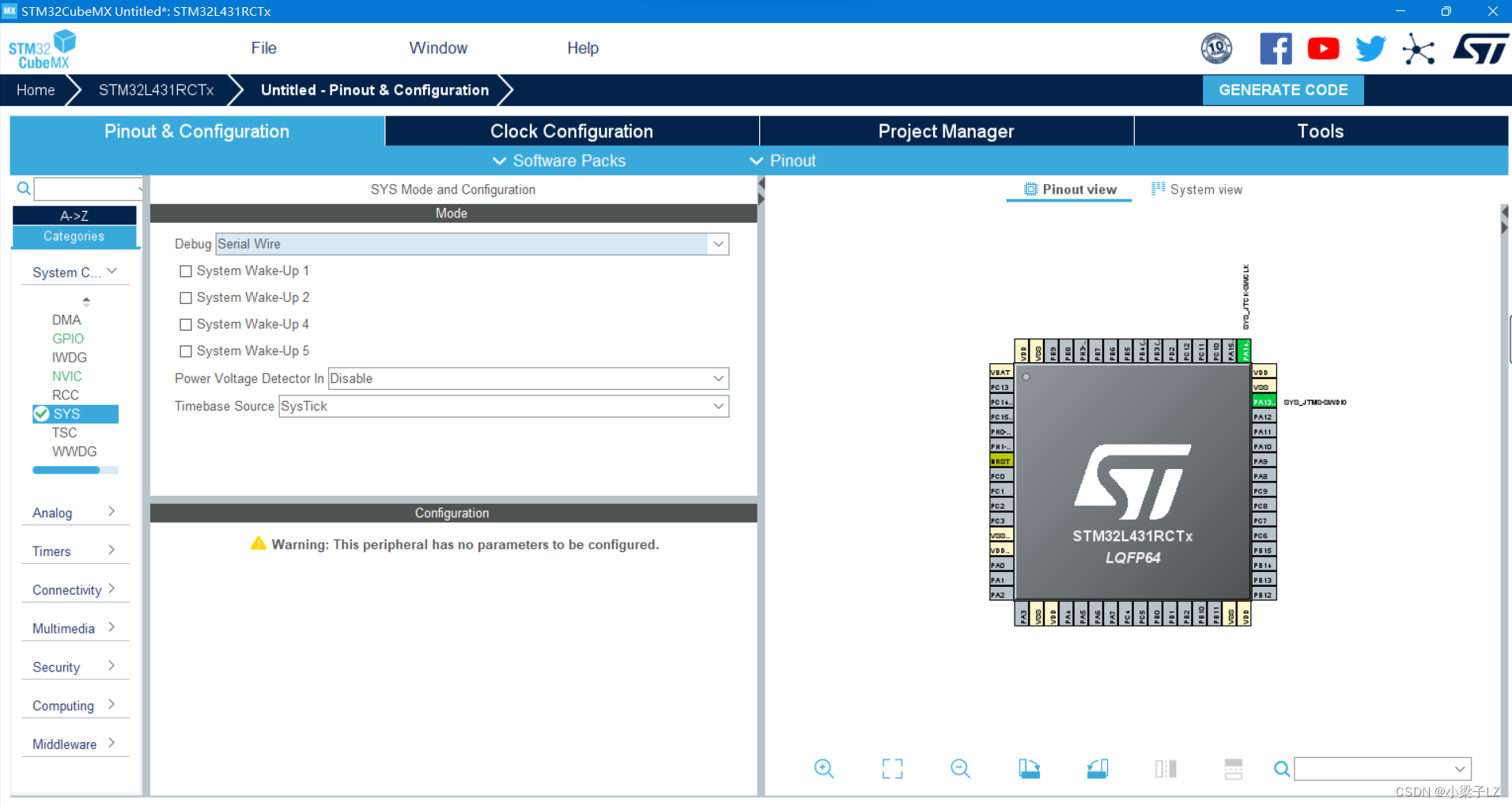

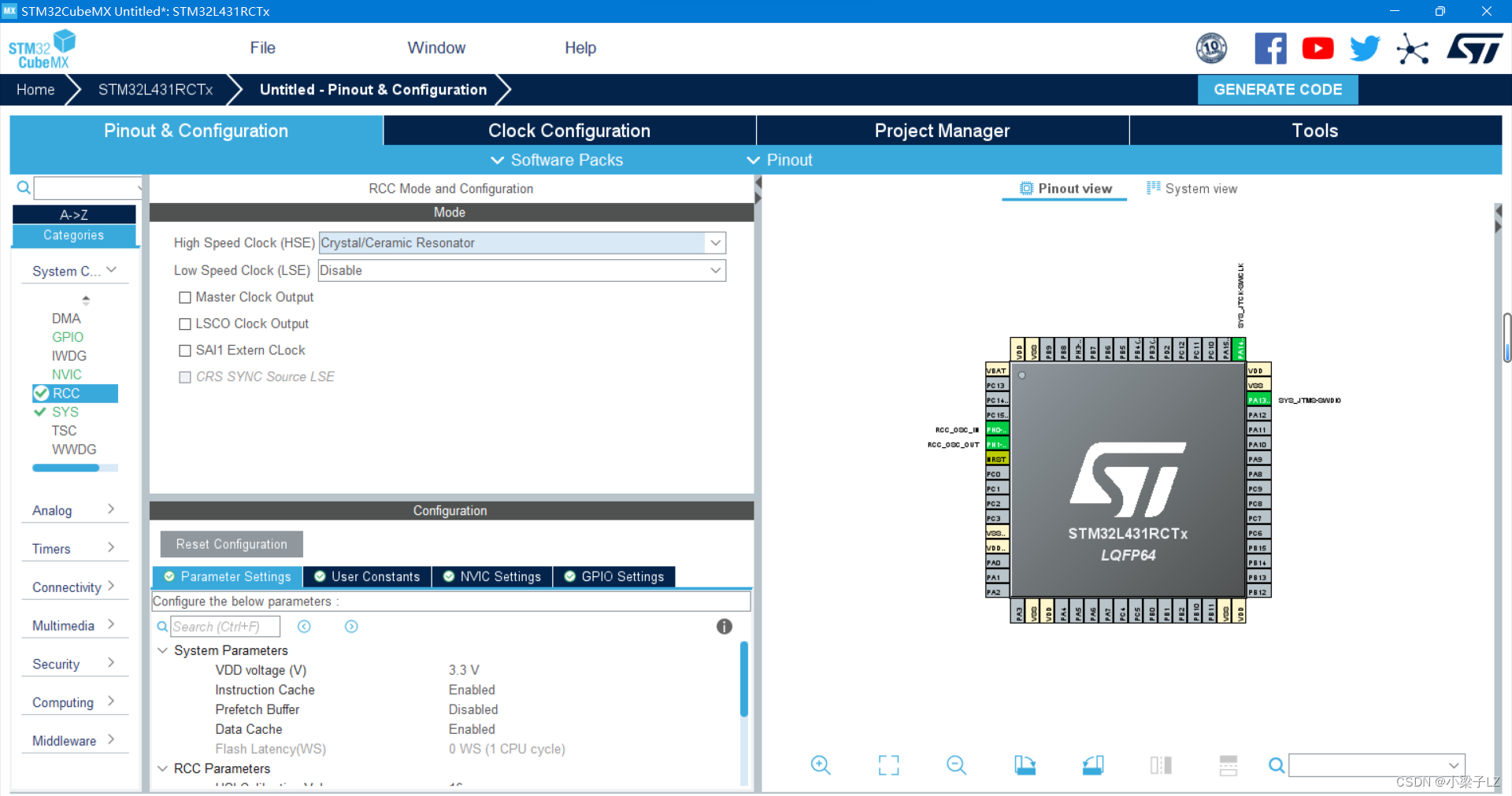

配置相关引脚和时钟

这里的PA0是作者板子上的LED灯,兄弟们可以改成自己的

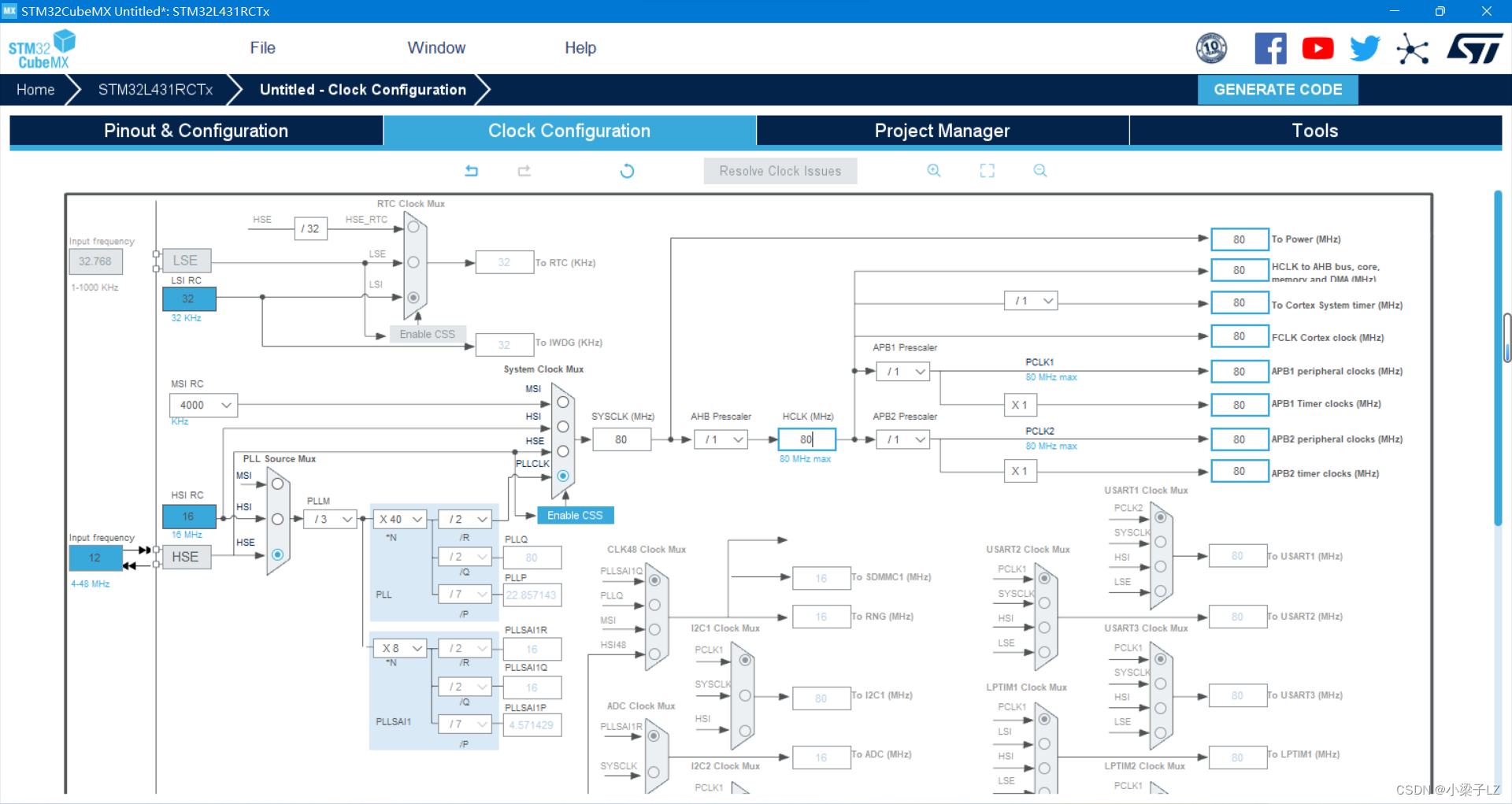

关于时钟树,作者的开发板的外部晶振是12MHZ,兄弟们自行更改

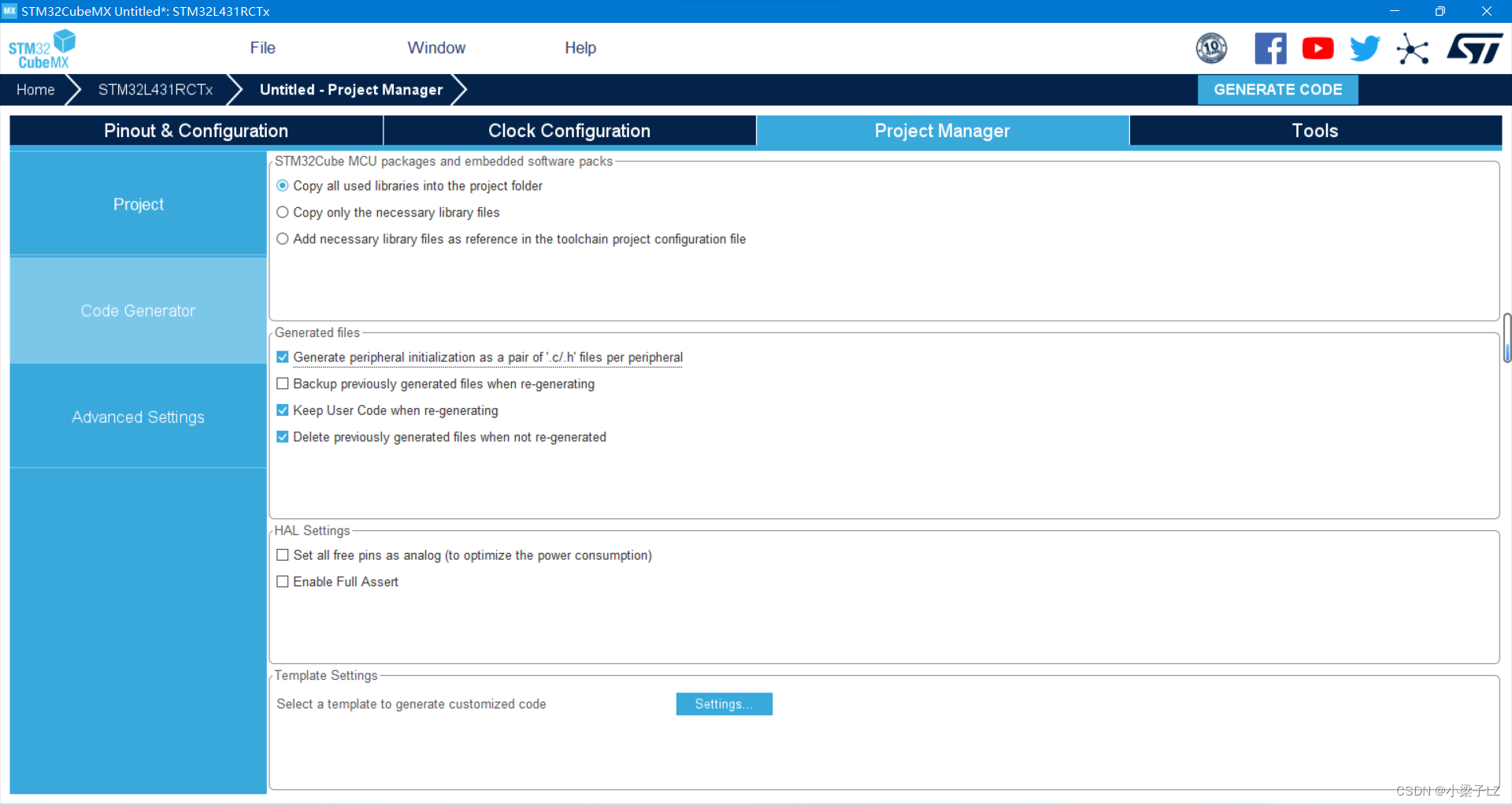

然后点击Project Manager,设置文件名、保存位置、生成MDK-ARM工程,并把.c和.h文件分开

最后点击右上上角的GENERATE CODE,弹出如下提示,点击Close,并退出CubeMX

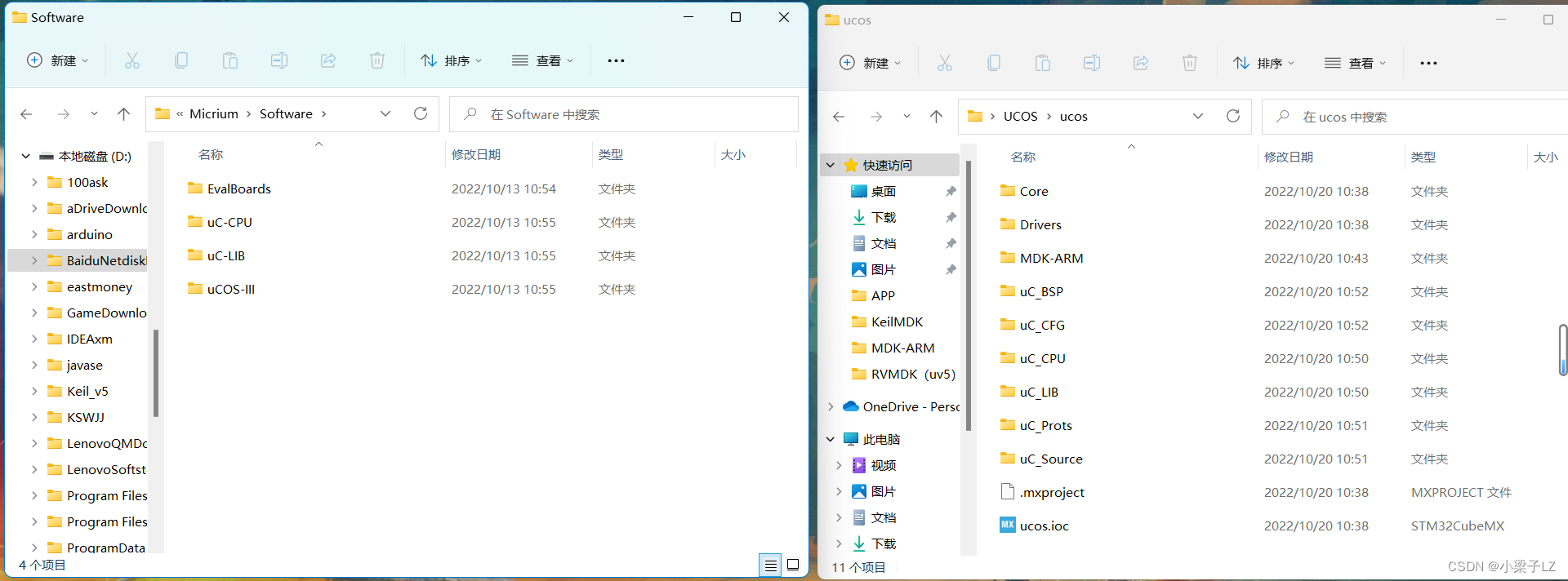

第二步复制官方源码,这里以Cotex-M4内核为例,Cotex-M3的移植过程类似,兄弟们自行尝试

打开文章前面提供的官方源码,没下载的现在去下载,下载好后是一个UCOS3.04.zip的文件,解压放到桌面方便查找,这里不截图了,比较简单

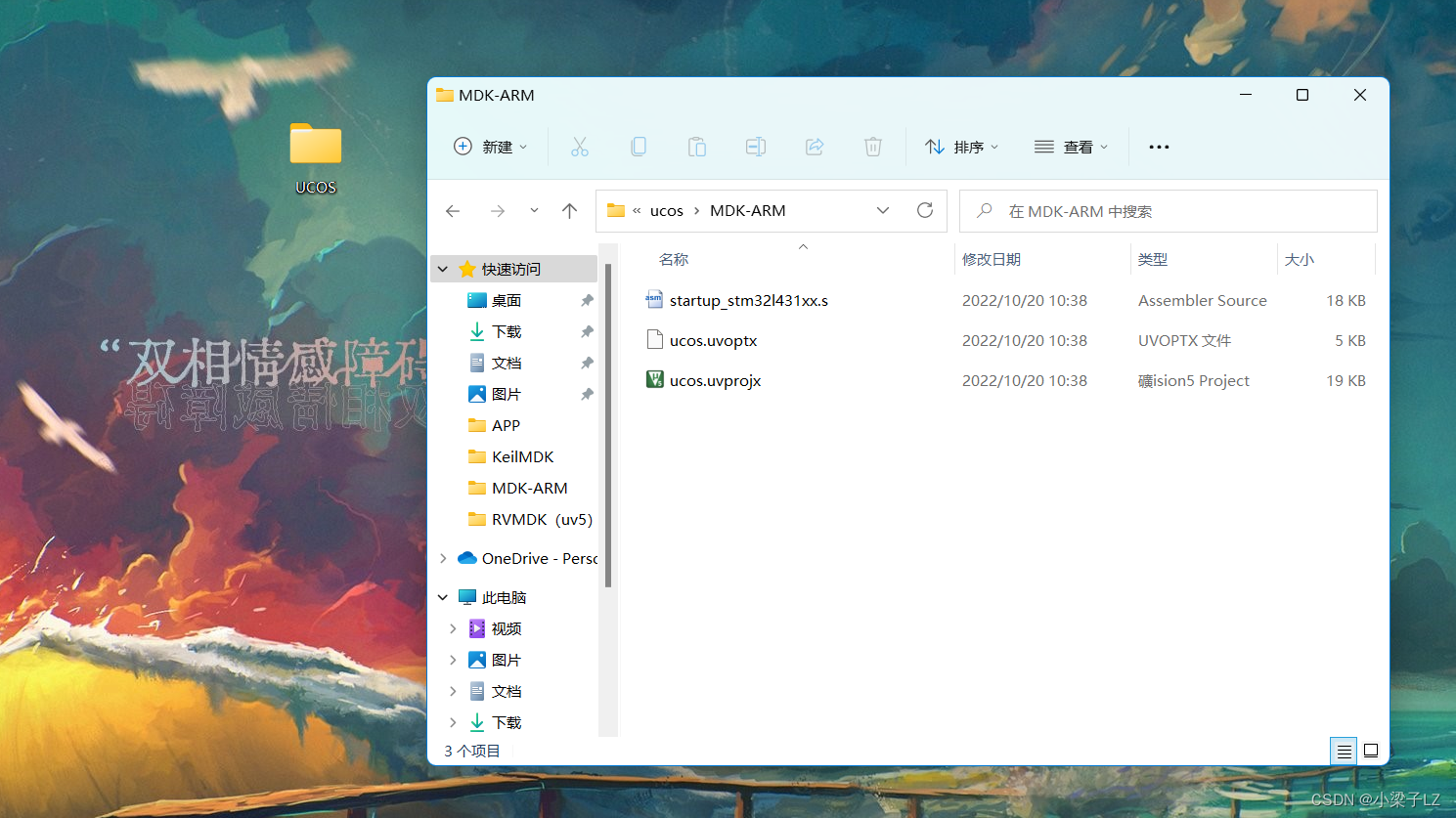

在我们自己创建的工程文件夹里,创建uC_CPU、uC_LIB、uC_BSP、uC_Ports、uC_Source、uC_CFG这几个文件夹

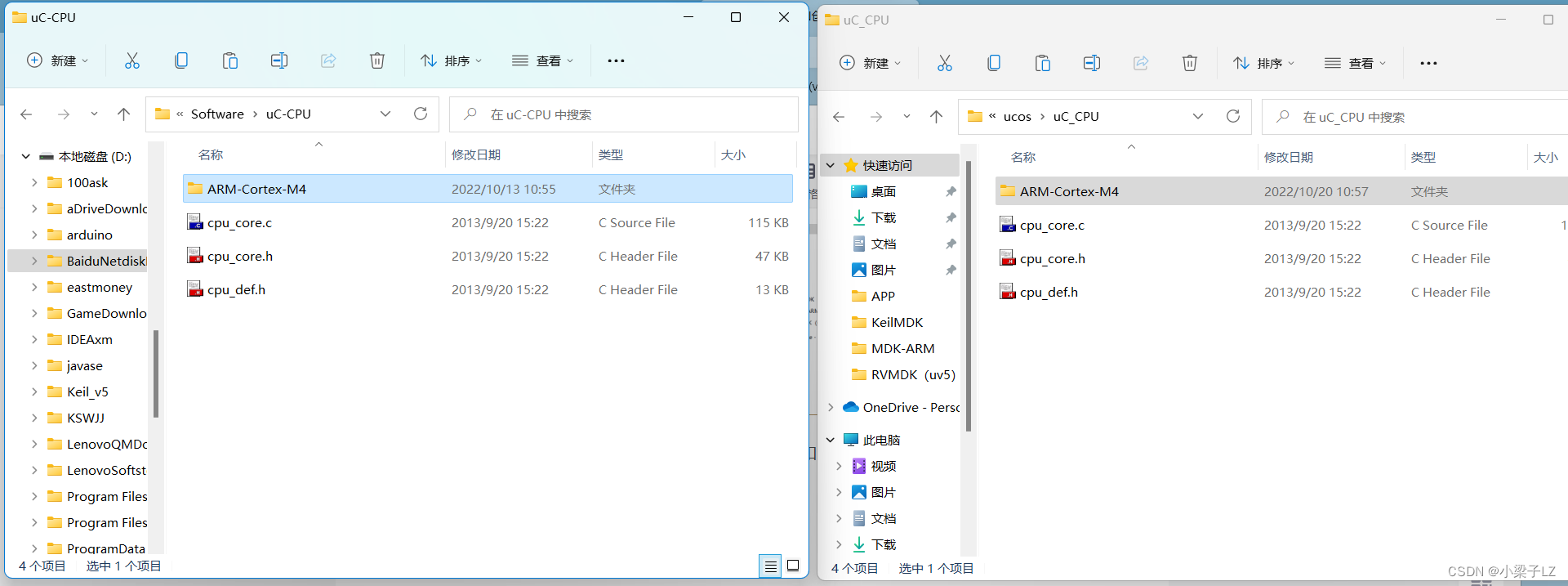

uC_CPU存放的内容如下,并把ARM-Cotex-M4里的GNU和IAR文件删除

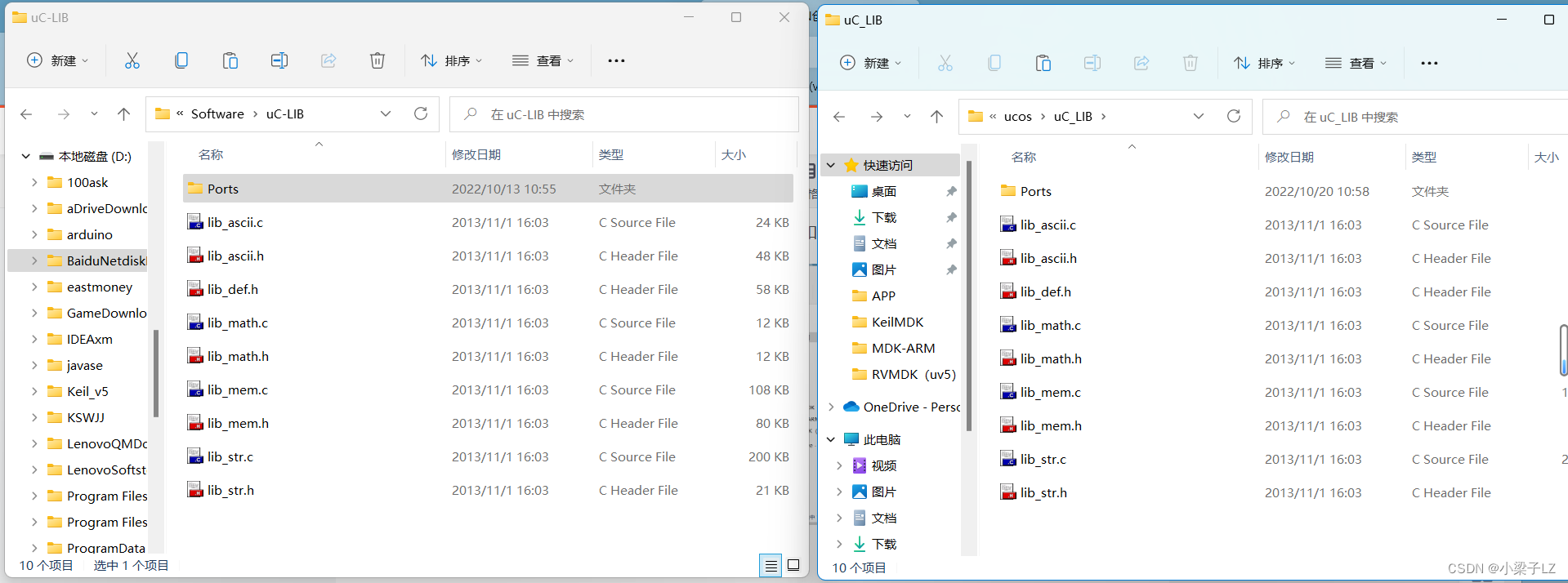

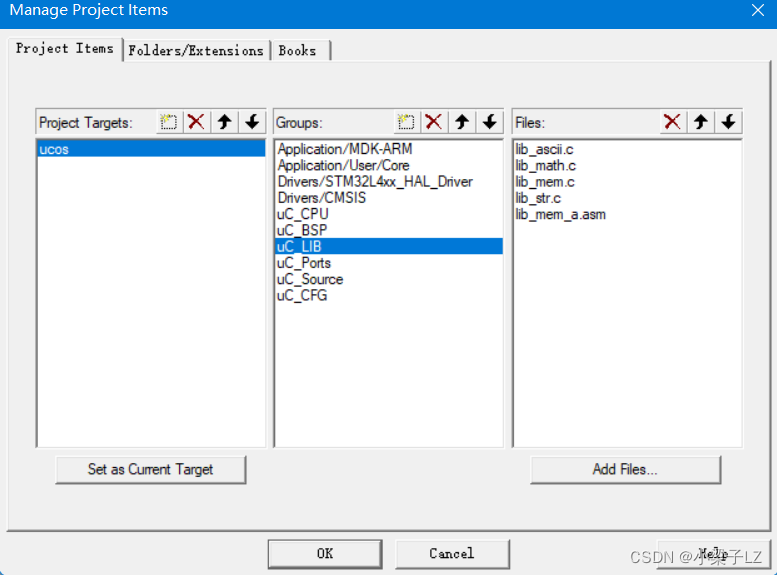

uC_LIB存放的内容如下,并把Ports->ARM-Cotex-M4下的GNU和IAR文件删除

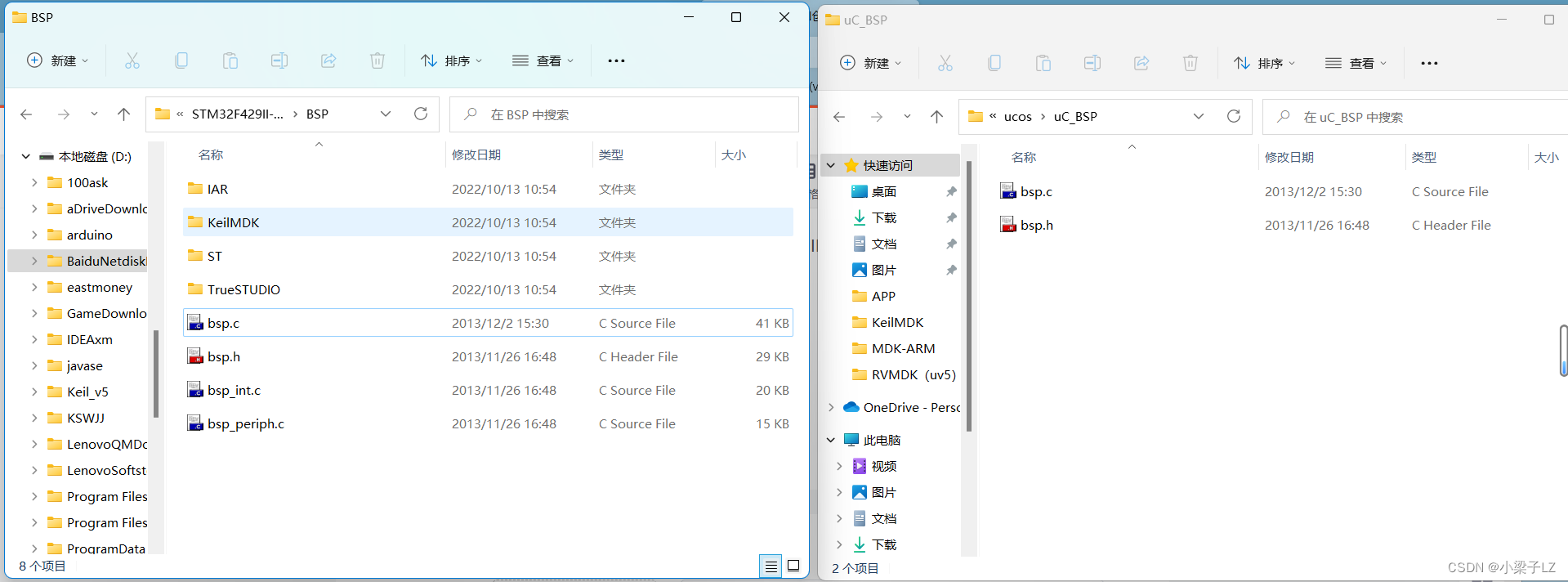

uC_BSP存放bsp.h和bsp.c,在官方源码的路径为UCOSIII3.04\Micrium\Software\EvalBoards\ST\

STM32F429II-SK\BSP下

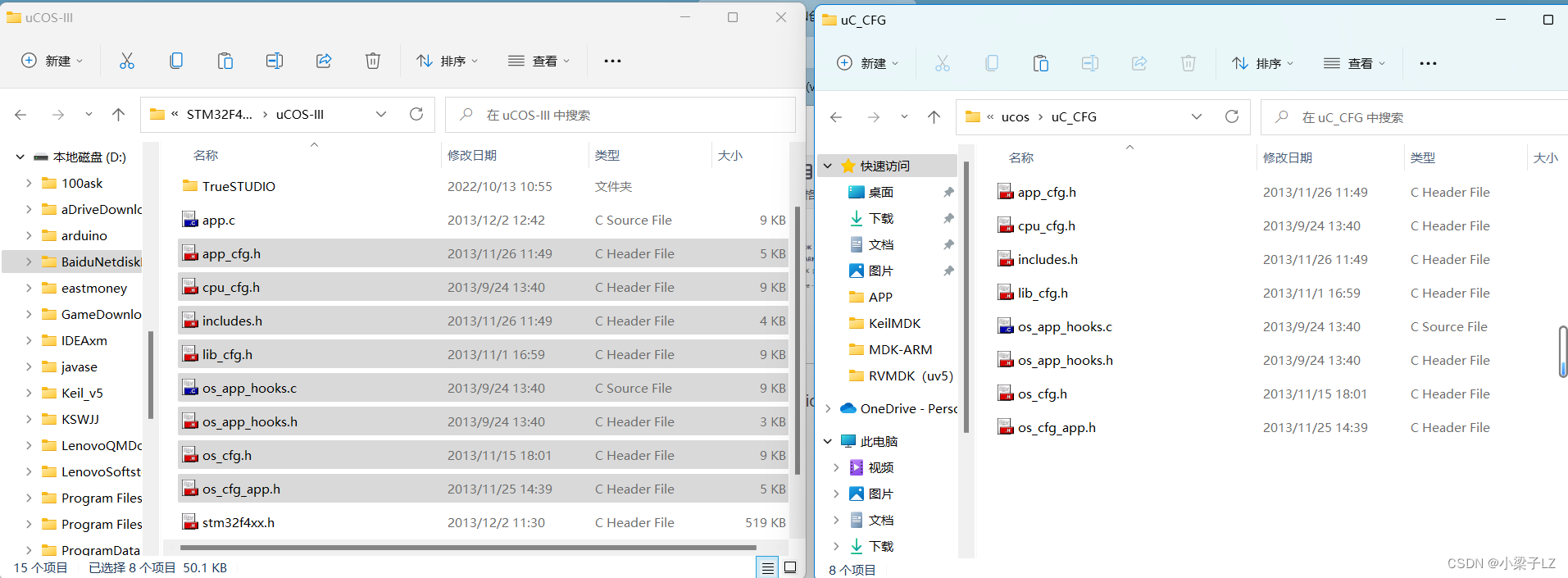

uC_CFG存放的文件在官方源码的路径为UCOSIII3.04\Micrium\Software\EvalBoards\ST\

STM32F429II-SK\uCOS-III下

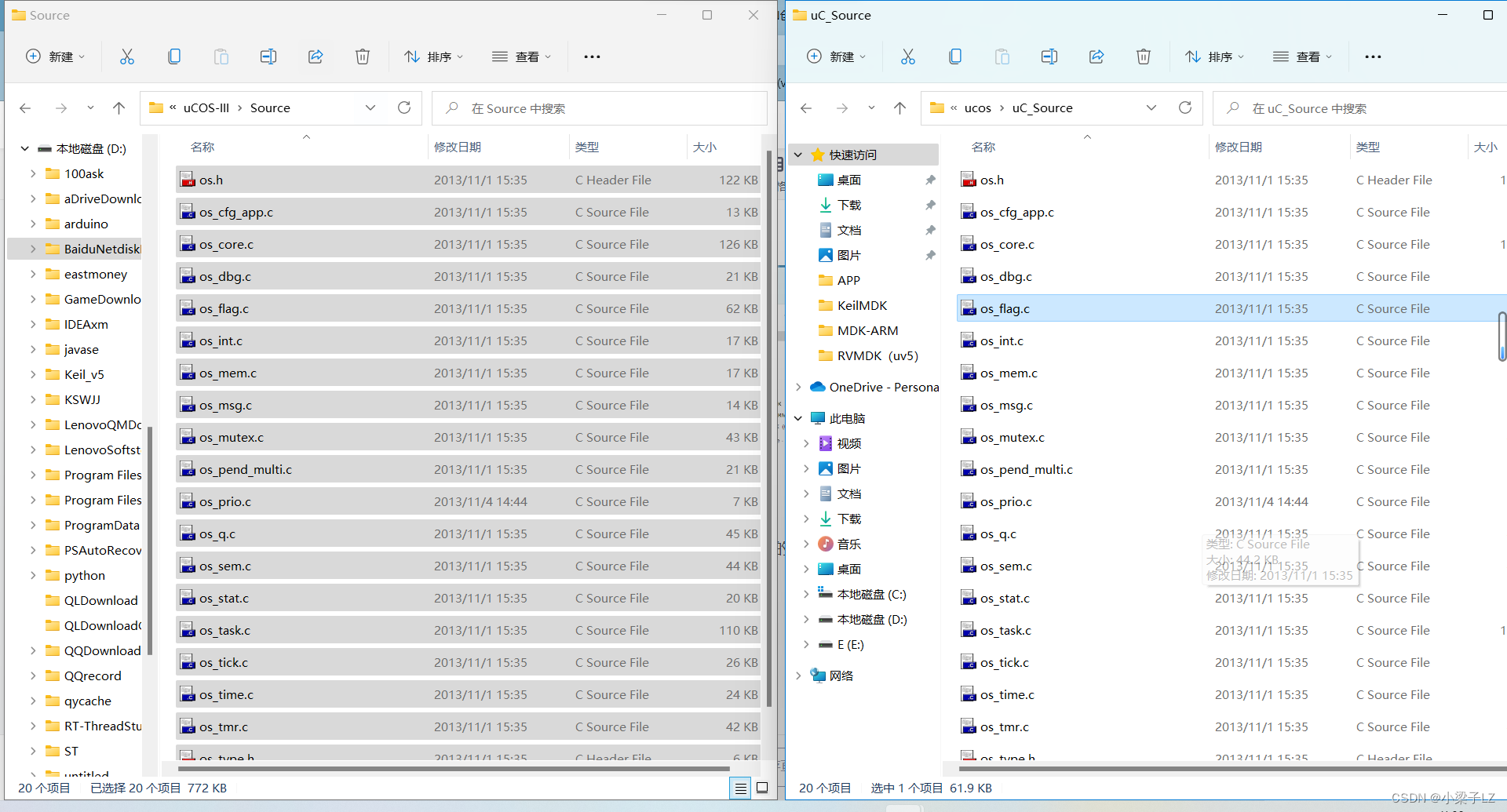

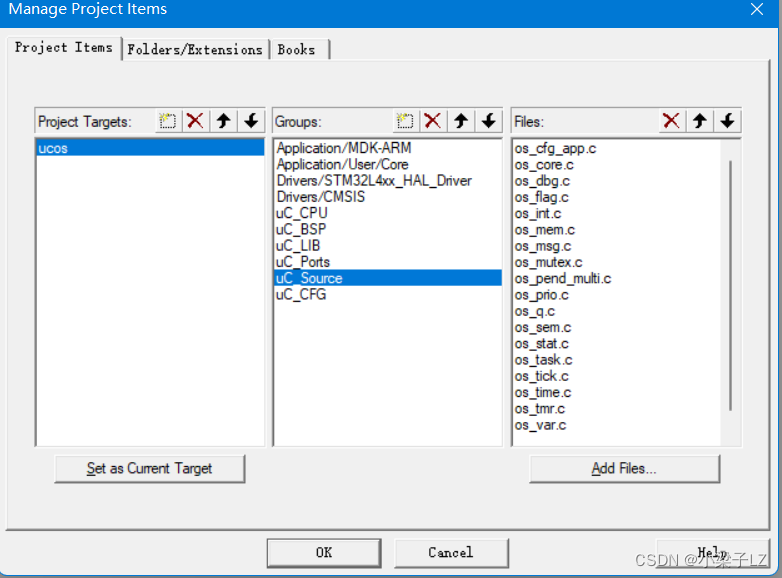

UCOSIII 3.04\Micrium\Software\uCOS-III\Source 文件下的内容复制到uC_Source

uC_Ports内只放三个文件,在官方源码的位置UCOSIII 3.04\Micrium\Software\uCOS-III\Ports\

ARM-Cortex-M4\Generic\RealView下

至此所有的文件都复制好了,文件夹可以关闭了

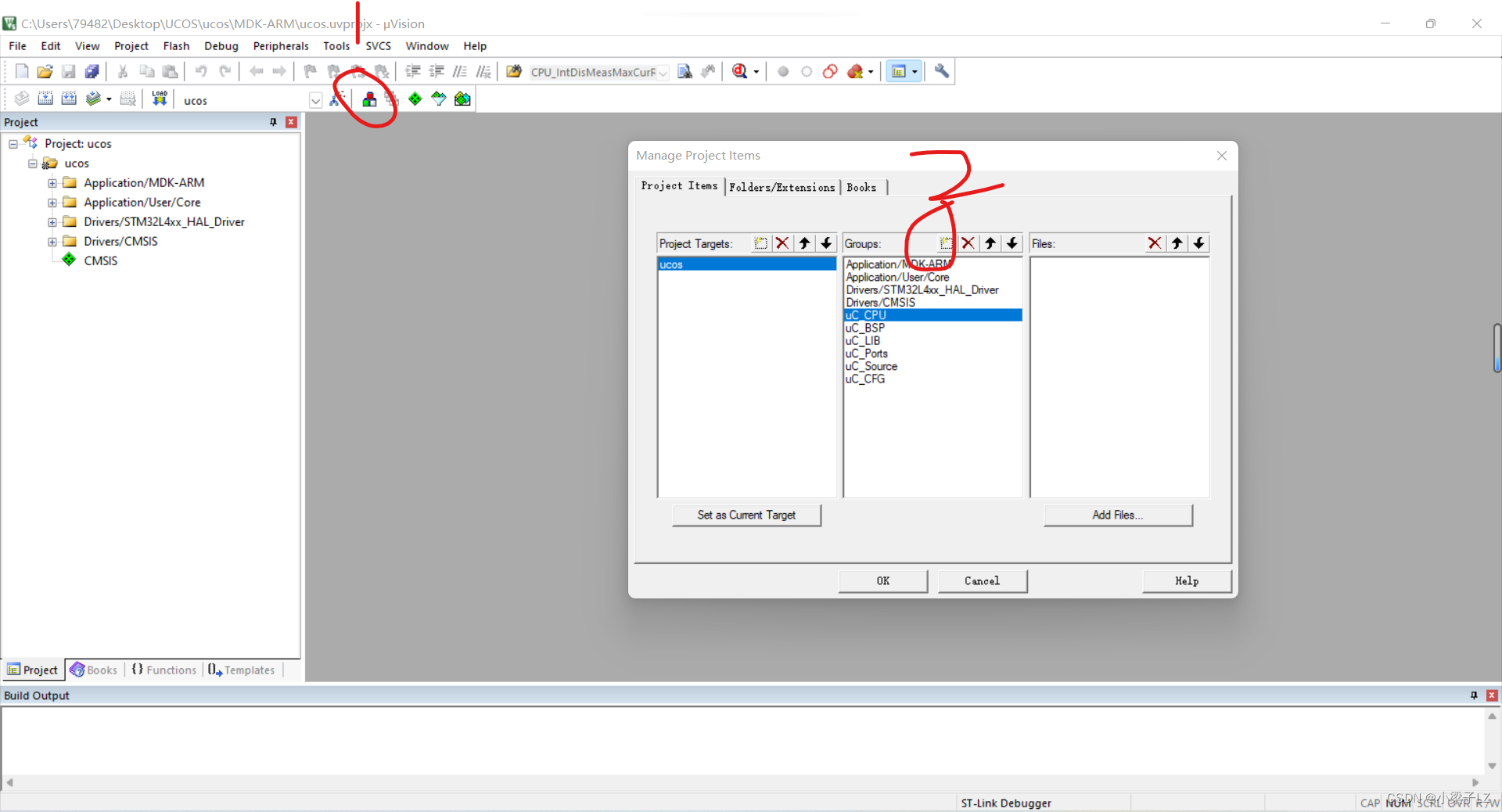

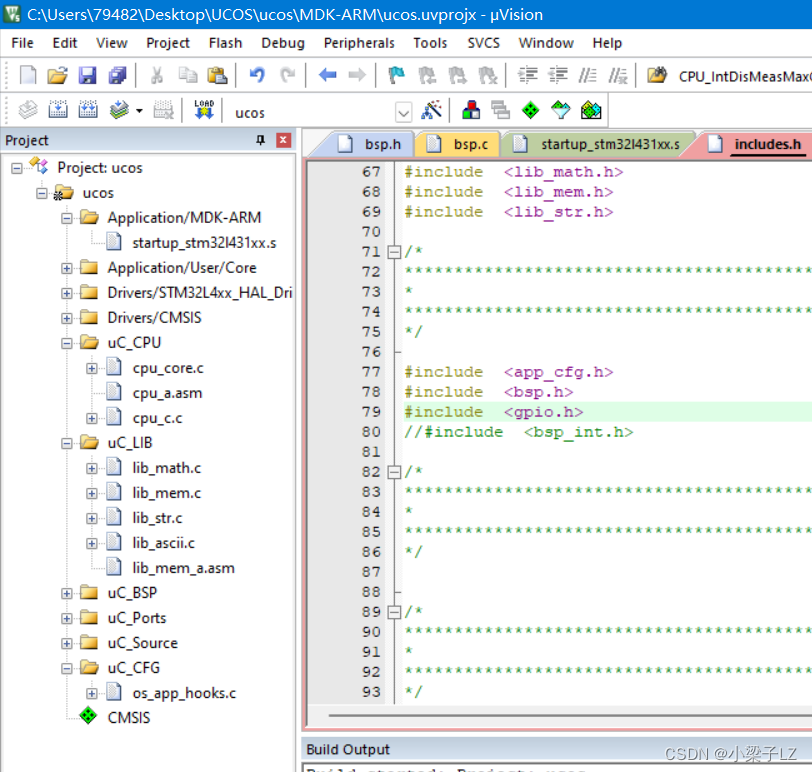

第三步修改Keil工程,打开Keil

虽然我们文件复制好了,但是目前Keil工程里还没有添加,下面就是添加到Keil工程里,兄弟们坚持住,革命已经进行一半了

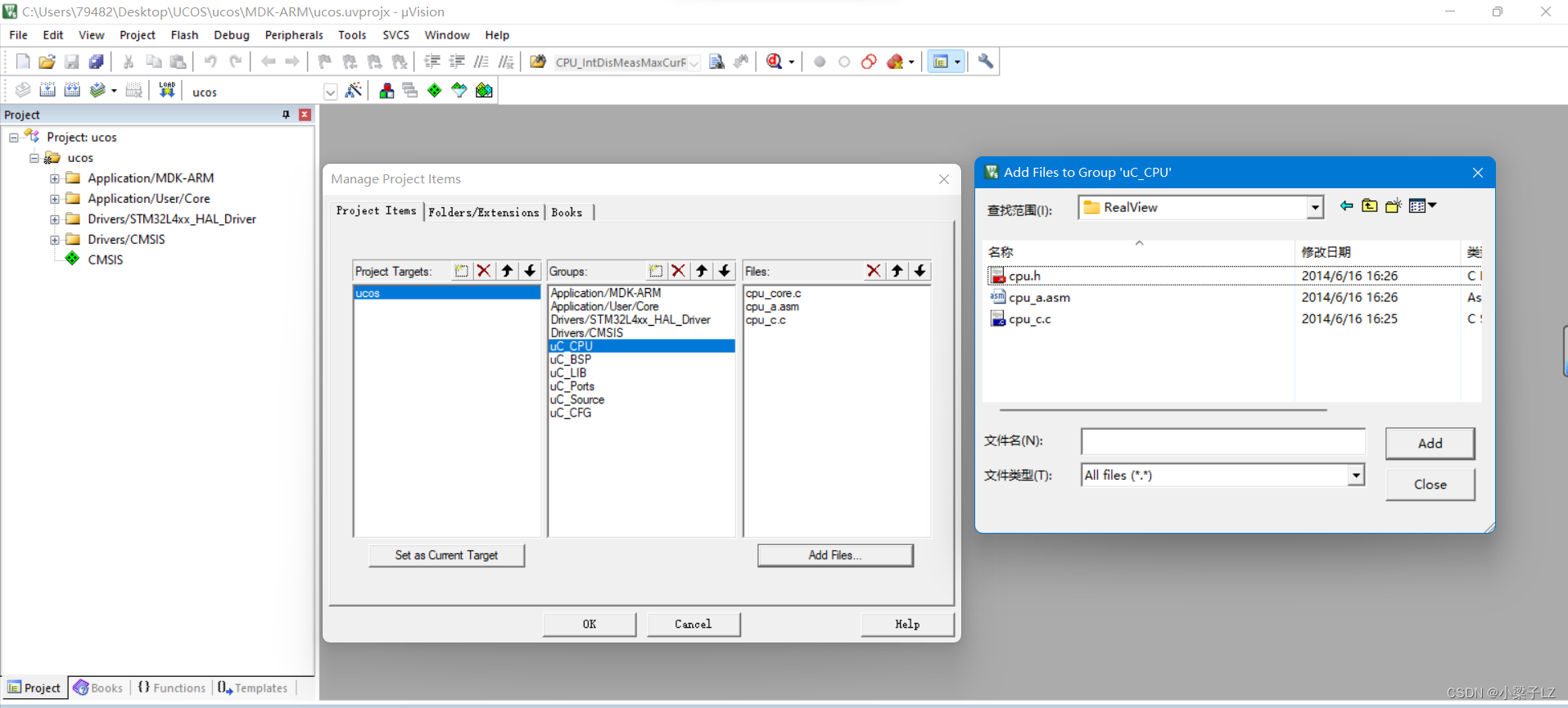

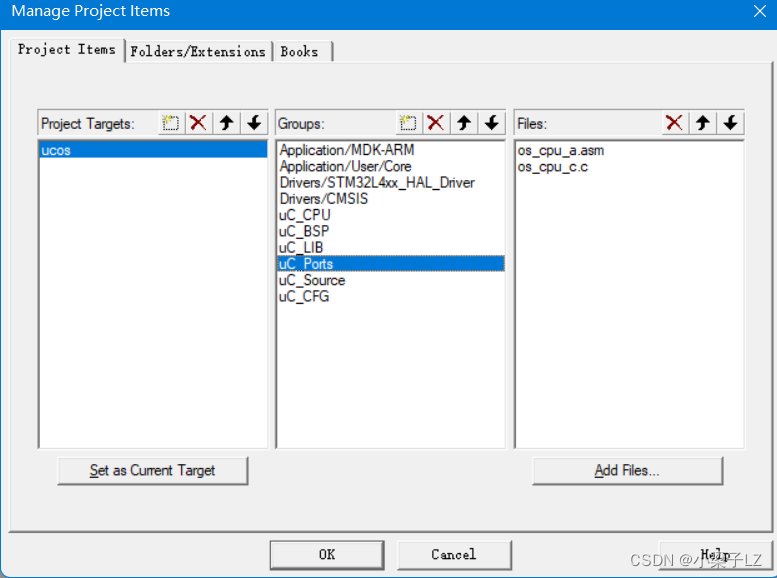

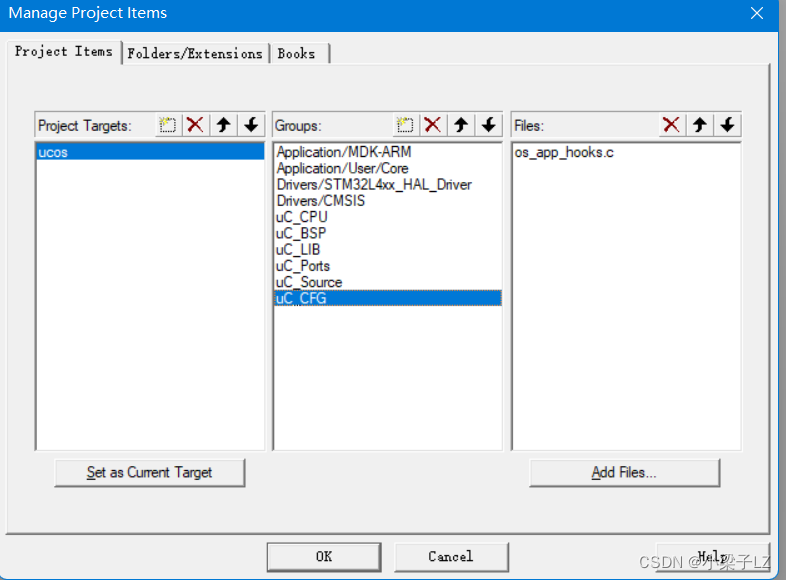

通过以下操作可以在keil里创建文件夹,选中文件夹点击Add files可以往相应的文件夹里添加文件,现在我们要做的就是把刚刚复制的文件都加进来,所以我们要先创建uC_CPU、uC_LIB、uC_BSP、uC_Ports、uC_Source、uC_CFG这几个文件夹

然后往里面添加对应文件夹里面的内容(不需要添加.h文件) ,注意这里面有汇编文件,要把文件类型改为All files *.*才能看到

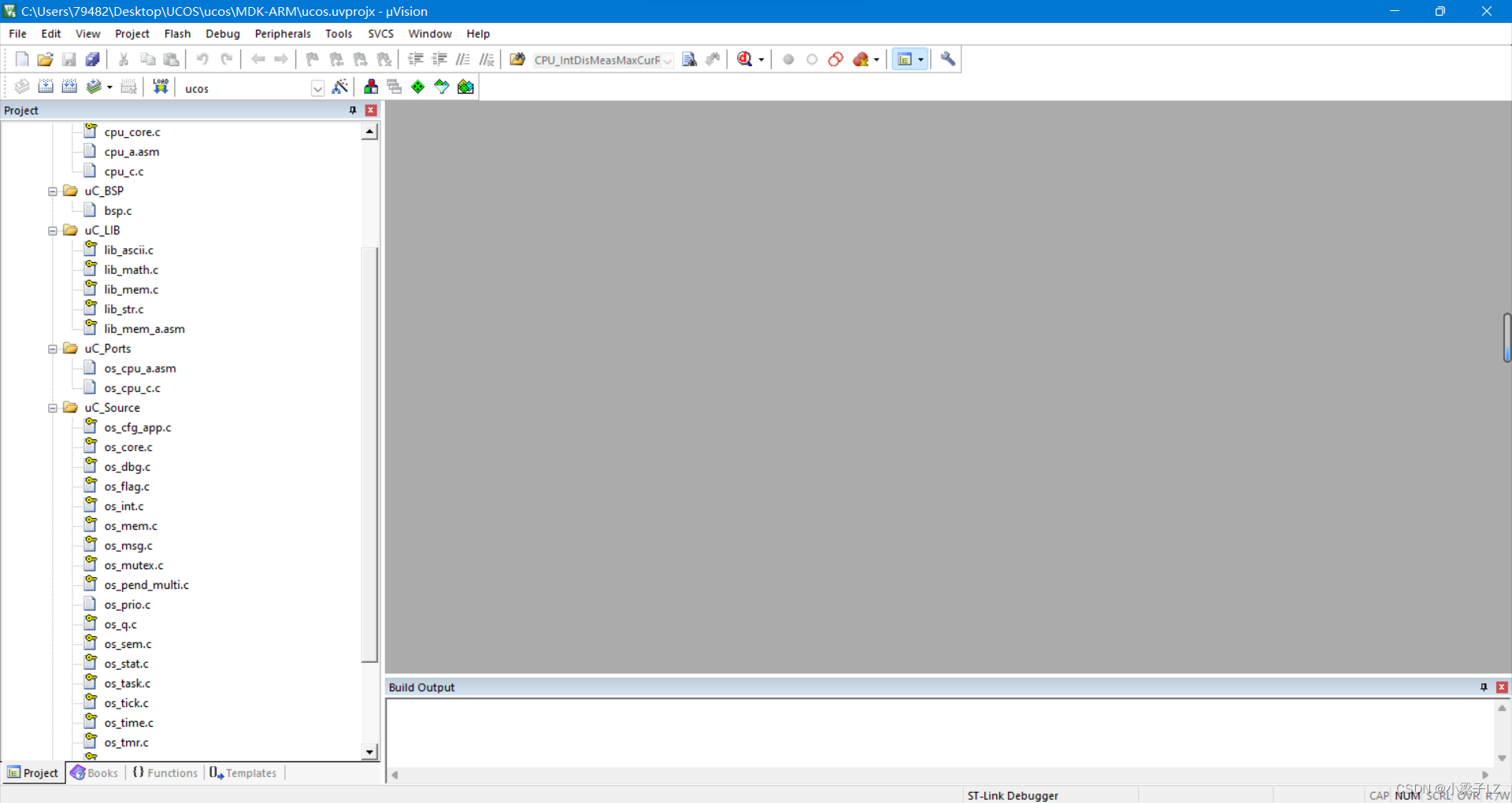

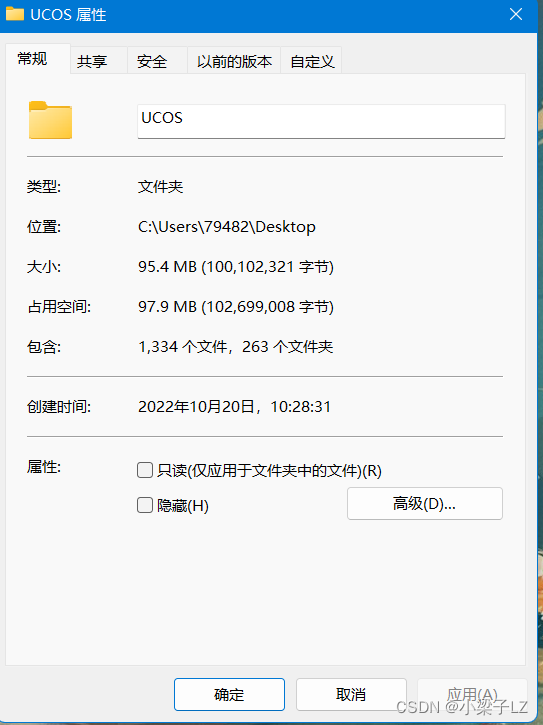

全部添加完毕点击OK,就可以看到我们的文件已经全部添加进来了,有个黄色的钥匙,意思是文件只读,我们先关闭Keil工程,再回到桌面找到我们创建的工程文件,右键---属性---把只读取消掉---应用,此时再打开Keil就没有黄色的钥匙了

第四步keil添加头文件

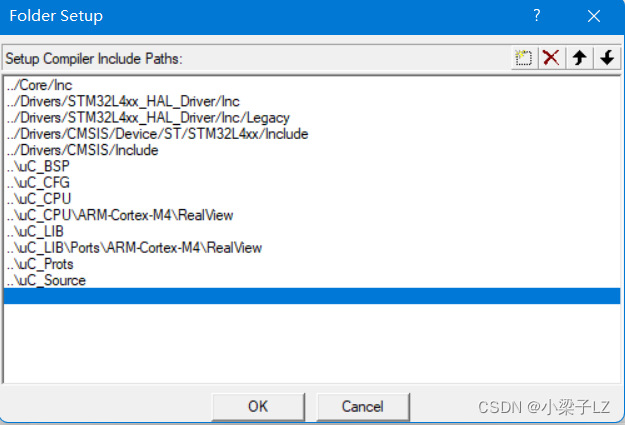

我们刚刚没有添加.h文件,现在要在编译器内添加头文件路径,按照下面步骤即可添加头文件路径

这是添加好的效果,不再一一截图了,太多了,添加完成后点击OK

第五步修改bsp.c、bsp.h

bsp.c修改为

#define BSP_MODULE

#include "includes.h"

#define BSP_REG_DEM_CR (*(CPU_REG32 *)0xE000EDFC)

#define BSP_REG_DWT_CR (*(CPU_REG32 *)0xE0001000)

#define BSP_REG_DWT_CYCCNT (*(CPU_REG32 *)0xE0001004)

#define BSP_REG_DBGMCU_CR (*(CPU_REG32 *)0xE0042004)

/* - RCC REGISTER DEFINES - */

#define BSP_REG_RCC_BASE_ADDR ((CPU_INT32U)(0x40023800))

#define BSP_REG32_RCC_CR (*(CPU_REG32 *)( BSP_REG_RCC_BASE_ADDR + 0x00u ))

#define BSP_REG32_RCC_PLLCFGR (*(CPU_REG32 *)( BSP_REG_RCC_BASE_ADDR + 0x04u ))

#define BSP_REG32_RCC_CFGR (*(CPU_REG32 *)( BSP_REG_RCC_BASE_ADDR + 0x08u ))

#define BSP_REG32_RCC_CIR (*(CPU_REG32 *)( BSP_REG_RCC_BASE_ADDR + 0x0Cu ))

#define BSP_REG32_RCC_AHB1RSTR (*(CPU_REG32 *)( BSP_REG_RCC_BASE_ADDR + 0x10u ))

#define BSP_REG32_RCC_AHB2RSTR (*(CPU_REG32 *)( BSP_REG_RCC_BASE_ADDR + 0x14u ))

#define BSP_REG32_RCC_AHB3RSTR (*(CPU_REG32 *)( BSP_REG_RCC_BASE_ADDR + 0x18u ))

#define BSP_REG32_RCC_APB1RSTR (*(CPU_REG32 *)( BSP_REG_RCC_BASE_ADDR + 0x20u ))

#define BSP_REG32_RCC_APB2RSTR (*(CPU_REG32 *)( BSP_REG_RCC_BASE_ADDR + 0x24u ))

#define BSP_REG32_RCC_AHB1ENR (*(CPU_REG32 *)( BSP_REG_RCC_BASE_ADDR + 0x30u ))

#define BSP_REG32_RCC_AHB2ENR (*(CPU_REG32 *)( BSP_REG_RCC_BASE_ADDR + 0x34u ))

#define BSP_REG32_RCC_AHB3ENR (*(CPU_REG32 *)( BSP_REG_RCC_BASE_ADDR + 0x38u ))

#define BSP_REG32_RCC_APB1ENR (*(CPU_REG32 *)( BSP_REG_RCC_BASE_ADDR + 0x40u ))

#define BSP_REG32_RCC_APB2ENR (*(CPU_REG32 *)( BSP_REG_RCC_BASE_ADDR + 0x44u ))

#define BSP_REG32_RCC_AHB1LPENR (*(CPU_REG32 *)( BSP_REG_RCC_BASE_ADDR + 0x50u ))

#define BSP_REG32_RCC_AHB2LPENR (*(CPU_REG32 *)( BSP_REG_RCC_BASE_ADDR + 0x54u ))

#define BSP_REG32_RCC_AHB3LPENR (*(CPU_REG32 *)( BSP_REG_RCC_BASE_ADDR + 0x58u ))

#define BSP_REG32_RCC_APB1LPENR (*(CPU_REG32 *)( BSP_REG_RCC_BASE_ADDR + 0x60u ))

#define BSP_REG32_RCC_APB2LPENR (*(CPU_REG32 *)( BSP_REG_RCC_BASE_ADDR + 0x64u ))

#define BSP_REG32_RCC_BDCR (*(CPU_REG32 *)( BSP_REG_RCC_BASE_ADDR + 0x70u ))

#define BSP_REG32_RCC_CSR (*(CPU_REG32 *)( BSP_REG_RCC_BASE_ADDR + 0x74u ))

#define BSP_REG32_RCC_SSCGR (*(CPU_REG32 *)( BSP_REG_RCC_BASE_ADDR + 0x80u ))

#define BSP_REG32_RCC_PLLI2SCFGR (*(CPU_REG32 *)( BSP_REG_RCC_BASE_ADDR + 0x84u ))

#define BSP_REG32_RCC_PLLSAICFGR (*(CPU_REG32 *)( BSP_REG_RCC_BASE_ADDR + 0x88u ))

#define BSP_REG32_RCC_DCKCFGR (*(CPU_REG32 *)( BSP_REG_RCC_BASE_ADDR + 0x8Cu ))

/* - FLASH REGISTER DEFINES - */

#define BSP_REG_FLASH_BASE_ADDR (( CPU_INT32U )(0x40023C00))

#define BSP_REG32_FLASH_ACR (*(CPU_REG32 *)( BSP_REG_FLASH_BASE_ADDR + 0x00u ))

#define BSP_REG32_FLASH_KEYR (*(CPU_REG32 *)( BSP_REG_FLASH_BASE_ADDR + 0x04u ))

#define BSP_REG32_FLASH_OPTKEYR (*(CPU_REG32 *)( BSP_REG_FLASH_BASE_ADDR + 0x08u ))

#define BSP_REG32_FLASH_SR (*(CPU_REG32 *)( BSP_REG_FLASH_BASE_ADDR + 0x0Cu ))

#define BSP_REG32_FLASH_CR (*(CPU_REG32 *)( BSP_REG_FLASH_BASE_ADDR + 0x10u ))

#define BSP_REG32_FLASH_OPTCR (*(CPU_REG32 *)( BSP_REG_FLASH_BASE_ADDR + 0x14u ))

#define BSP_REG32_FLASH_OPTCR1 (*(CPU_REG32 *)( BSP_REG_FLASH_BASE_ADDR + 0x18u ))

#define BSP_DBGMCU_CR_TRACE_IOEN_MASK 0x10u

#define BSP_DBGMCU_CR_TRACE_MODE_ASYNC 0x00u

#define BSP_DBGMCU_CR_TRACE_MODE_SYNC_01 0x40u

#define BSP_DBGMCU_CR_TRACE_MODE_SYNC_02 0x80u

#define BSP_DBGMCU_CR_TRACE_MODE_SYNC_04 0xC0u

#define BSP_DBGMCU_CR_TRACE_MODE_MASK 0xC0u

#define BSP_BIT_DEM_CR_TRCENA DEF_BIT_24

#define BSP_BIT_DWT_CR_CYCCNTENA DEF_BIT_00

/* - RCC BLOCK - */

#define HSE_TIMEOUT_VAL 0x0500u

#define BSP_MSK_HSECFG 0x00FF0000u

#define BSP_BIT_RCC_CR_HSION DEF_BIT_00

#define BSP_BIT_RCC_CR_HSEBYP DEF_BIT_18

#define BSP_BIT_RCC_CR_HSEON DEF_BIT_16

#define BSP_BIT_RCC_CR_HSERDY DEF_BIT_17

#define BSP_MSK_RCC_CFGR_HPRE 0x000000F0u

#define BSP_MSK_RCC_CFGR_SYSCLKDIV1 0x00000000u

#define BSP_MSK_RCC_CFGR_SYSCLKDIV2 0x00000080u

#define BSP_MSK_RCC_CFGR_SYSCLKDIV4 0x00000090u

#define BSP_MSK_RCC_CFGR_SYSCLKDIV8 0x000000A0u

#define BSP_MSK_RCC_CFGR_SYSCLKDIV16 0x000000B0u

#define BSP_MSK_RCC_CFGR_SYSCLKDIV64 0x000000C0u

#define BSP_MSK_RCC_CFGR_SYSCLKDIV128 0x000000D0u

#define BSP_MSK_RCC_CFGR_SYSCLKDIV256 0x000000E0u

#define BSP_MSK_RCC_CFGR_SYSCLKDIV512 0x000000F0u

#define BSP_MSK_RCC_CFGR_PPRE1 0x00001C00u

#define BSP_MSK_RCC_CFGR_PPRE2 0x0000E000u

#define BSP_MSK_RCC_CFGR_HCLK_DIV1 0x00000000u

#define BSP_MSK_RCC_CFGR_HCLK_DIV2 0x00001000u

#define BSP_MSK_RCC_CFGR_HCLK_DIV4 0x00001400u

#define BSP_MSK_RCC_CFGR_HCLK_DIV8 0x00001800u

#define BSP_MSK_RCC_CFGR_HCLK_DIV16 0x00001C00u

#define BSP_MSK_RCC_CFGR_SWS_HSI 0x00000000u

#define BSP_MSK_RCC_CFGR_SWS_HSE 0x00000004u

#define BSP_MSK_RCC_CFGR_SWS_PLL 0x00000008u

#define BSP_MSK_RCC_CFGR_SWS 0x0000000Cu

#define BSP_MSK_RCC_CFGR_SW_HSI 0x00000000u

#define BSP_MSK_RCC_CFGR_SW_HSE 0x00000001u

#define BSP_MSK_RCC_CFGR_SW_PLL 0x00000002u

#define BSP_MSK_RCC_CFGR_SW 0x00000003u

/* - PLL BLOCK - */

#define BSP_BIT_RCC_PLLCFGR_PLLM 8u

#define BSP_BIT_RCC_PLLCFGR_PLLN 336u

#define BSP_BIT_RCC_PLLCFGR_PLLP 2u

#define BSP_BIT_RCC_PLLCFGR_PLLQ 7u

#define BSP_BIT_RCC_CR_PLLON DEF_BIT_24

#define BSP_BIT_RCC_CR_PLLRDY DEF_BIT_25

#define BSP_MSK_RCC_PLLCFGR_PLLSRC_HSE 0x00400000u

#define BSP_MSK_RCC_PLLCFGR_RST 0x24003010u

#define BSP_MSK_SYSCLK_SRC_PLLCLK 0x00000002u

#define BSP_MSK_PLLCFGR_PLLSRC_HSE 0x00400000u

#define BSP_MSK_PLLCFGR_PLLSRC_HSI 0x00000000u

/* - FLASH BLOCK - */

#define BSP_BIT_FLASH_ACR_PRFTEN DEF_BIT_08

#define BSP_BIT_FLASH_ACR_ICEN DEF_BIT_09

#define BSP_BIT_FLASH_ACR_DCEN DEF_BIT_10

#define BSP_MSK_FLASHLATENCY_0WS 0x00000000u

#define BSP_MSK_FLASHLATENCY_1WS 0x00000001u

#define BSP_MSK_FLASHLATENCY_2WS 0x00000002u

#define BSP_MSK_FLASHLATENCY_3WS 0x00000003u

#define BSP_MSK_FLASHLATENCY_4WS 0x00000004u

#define BSP_MSK_FLASHLATENCY_5WS 0x00000005u

#define BSP_MSK_FLASHLATENCY_6WS 0x00000006u

#define BSP_MSK_FLASHLATENCY_7WS 0x00000007u

#define BSP_MSK_FLASHLATENCY_8WS 0x00000008u

#define BSP_MSK_FLASHLATENCY_9WS 0x00000009u

#define BSP_MSK_FLASHLATENCY_10WS 0x0000000Au

#define BSP_MSK_FLASHLATENCY_11WS 0x0000000Bu

#define BSP_MSK_FLASHLATENCY_12WS 0x0000000Cu

#define BSP_MSK_FLASHLATENCY_13WS 0x0000000Du

#define BSP_MSK_FLASHLATENCY_14WS 0x0000000Eu

#define BSP_MSK_FLASHLATENCY_15WS 0x0000000Fu

void BSP_Init (void)

{

BSP_Tick_Init ();

MX_GPIO_Init();

}

CPU_INT32U BSP_CPU_ClkFreq (void)

{

return (HAL_RCC_GetSysClockFreq());

}

void BSP_Tick_Init (void)

{

CPU_INT32U cpu_clk_freq;

CPU_INT32U cnts;

cpu_clk_freq = BSP_CPU_ClkFreq(); /* Determine SysTick reference freq. */

#if (OS_VERSION >= 30000u)

cnts = (cpu_clk_freq / (CPU_INT32U)OSCfg_TickRate_Hz); /* Determine nbr SysTick increments */

#else

cnts = (cpu_clk_freq / (CPU_INT32U)OS_TICKS_PER_SEC); /* Determine nbr SysTick increments. */

#endif

OS_CPU_SysTickInit(cnts); /* Init uC/OS periodic time src (SysTick). */

}

#if (CPU_CFG_TS_TMR_EN == DEF_ENABLED)

void CPU_TS_TmrInit (void)

{

CPU_INT32U fclk_freq;

fclk_freq = BSP_CPU_ClkFreq();

BSP_REG_DEM_CR |= (CPU_INT32U)BSP_BIT_DEM_CR_TRCENA; /* Enable Cortex-M4's DWT CYCCNT reg. */

BSP_REG_DWT_CYCCNT = (CPU_INT32U)0u;

BSP_REG_DWT_CR |= (CPU_INT32U)BSP_BIT_DWT_CR_CYCCNTENA;

CPU_TS_TmrFreqSet((CPU_TS_TMR_FREQ)fclk_freq);

}

#endif

#if (CPU_CFG_TS_TMR_EN == DEF_ENABLED)

CPU_TS_TMR CPU_TS_TmrRd (void)

{

CPU_TS_TMR ts_tmr_cnts;

ts_tmr_cnts = (CPU_TS_TMR)BSP_REG_DWT_CYCCNT;

return (ts_tmr_cnts);

}

#endif

#if (CPU_CFG_TS_32_EN == DEF_ENABLED)

CPU_INT64U CPU_TS32_to_uSec (CPU_TS32 ts_cnts)

{

CPU_INT64U ts_us;

CPU_INT64U fclk_freq;

fclk_freq = BSP_CPU_ClkFreq();

ts_us = ts_cnts / (fclk_freq / DEF_TIME_NBR_uS_PER_SEC);

return (ts_us);

}

#endif

#if (CPU_CFG_TS_64_EN == DEF_ENABLED)

CPU_INT64U CPU_TS64_to_uSec (CPU_TS64 ts_cnts)

{

CPU_INT64U ts_us;

CPU_INT64U fclk_freq;

fclk_freq = BSP_CPU_ClkFreq();

ts_us = ts_cnts / (fclk_freq / DEF_TIME_NBR_uS_PER_SEC);

return (ts_us);

}

#endifbsp.h修改为如下代码,注意头文件stm32l4xx.h这个是作者的芯片,兄弟们要改成自己的芯片

#ifndef BSP_PRESENT

#define BSP_PRESENT

#ifdef BSP_MODULE

#define BSP_EXT

#else

#define BSP_EXT extern

#endif

#include <stdio.h>

#include <stdarg.h>

#include <cpu.h>

#include <cpu_core.h>

#include <lib_def.h>

#include <lib_ascii.h>

#include "stm32l4xx.h"

void BSP_Init (void);

CPU_INT32U BSP_CPU_ClkFreq (void);

void BSP_Tick_Init (void);

#endif 第六步修改startup_stm32l431xx.s

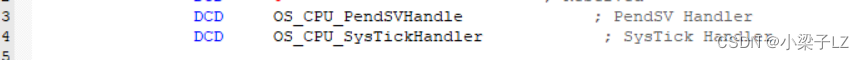

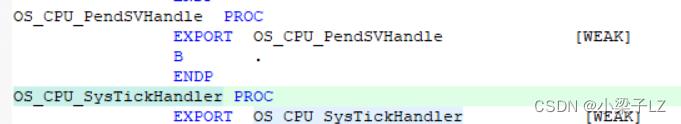

把PendSV_Handle和SysTick_Handler分别改为OS_CPU_PendSVHandler和OS_CPU_SysTickHandler

第七步在includes.h中添加#include <gpio.h>

至此我们已经移植完成,下边进行测试

第八步在app_cfg.h替換成如下代碼

/*

*********************************************************************************************************

* uC/OS-II

* The Real-Time Kernel

*

* (c) Copyright 2012; Micrium, Inc.; Weston, FL

*

* All rights reserved. Protected by international copyright laws.

*

* uC/OS-II is provided in source form for FREE evaluation, for educational

* use or peaceful research. If you plan on using uC/OS-II in a commercial

* product you need to contact Micrium to properly license its use in your

* product. We provide ALL the source code for your convenience and to

* help you experience uC/OS-II. The fact that the source code is provided

* does NOT mean that you can use it without paying a licensing fee.

*

* Knowledge of the source code may NOT be used to develop a similar product.

*

* Please help us continue to provide the Embedded community with the finest

* software available. Your honesty is greatly appreciated.

*********************************************************************************************************

*/

/*

*********************************************************************************************************

*

* APPLICATION CONFIGURATION

*

* IAR Development Kits

* on the

*

* STM32F429II-SK KICKSTART KIT

*

* Filename : app_cfg.h

* Version : V1.00

* Programmer(s) : FT

*********************************************************************************************************

*/

#ifndef APP_CFG_MODULE_PRESENT

#define APP_CFG_MODULE_PRESENT

/*

*********************************************************************************************************

* ADDITIONAL uC/MODULE ENABLES

*********************************************************************************************************

*/

/*

*********************************************************************************************************

* TASK PRIORITIES

*********************************************************************************************************

*/

#define APP_TASK_START_PRIO 2u

#define APP_TASK_LED1_PRIO 3

#define APP_TASK_LED2_PRIO 3

#define APP_TASK_LED3_PRIO 3

/*

*********************************************************************************************************

* TASK STACK SIZES

*********************************************************************************************************

*/

#define APP_TASK_START_STK_SIZE 1024u

#define APP_TASK_LED1_STK_SIZE 512

#define APP_TASK_LED2_STK_SIZE 512

#define APP_TASK_LED3_STK_SIZE 512

/*

*********************************************************************************************************

* TASK STACK SIZES LIMIT

*********************************************************************************************************

*/

#define BSP_CFG_SER_COMM_SEL BSP_SER_COMM_UART_02

#define BSP_CFG_TS_TMR_SEL 2

/*

*********************************************************************************************************

* TRACE / DEBUG CONFIGURATION

*********************************************************************************************************

*/

#ifndef TRACE_LEVEL_OFF

#define TRACE_LEVEL_OFF 0

#endif

#ifndef TRACE_LEVEL_INFO

#define TRACE_LEVEL_INFO 1

#endif

#ifndef TRACE_LEVEL_DBG

#define TRACE_LEVEL_DBG 2

#endif

#define APP_CFG_TRACE_LEVEL TRACE_LEVEL_OFF

#define APP_CFG_TRACE printf

#define BSP_CFG_TRACE_LEVEL TRACE_LEVEL_OFF

#define BSP_CFG_TRACE printf

#define APP_TRACE_INFO(x) ((APP_CFG_TRACE_LEVEL >= TRACE_LEVEL_INFO) ? (void)(APP_CFG_TRACE x) : (void)0)

#define APP_TRACE_DBG(x) ((APP_CFG_TRACE_LEVEL >= TRACE_LEVEL_DBG) ? (void)(APP_CFG_TRACE x) : (void)0)

#define BSP_TRACE_INFO(x) ((BSP_CFG_TRACE_LEVEL >= TRACE_LEVEL_INFO) ? (void)(BSP_CFG_TRACE x) : (void)0)

#define BSP_TRACE_DBG(x) ((BSP_CFG_TRACE_LEVEL >= TRACE_LEVEL_DBG) ? (void)(BSP_CFG_TRACE x) : (void)0)

#endif

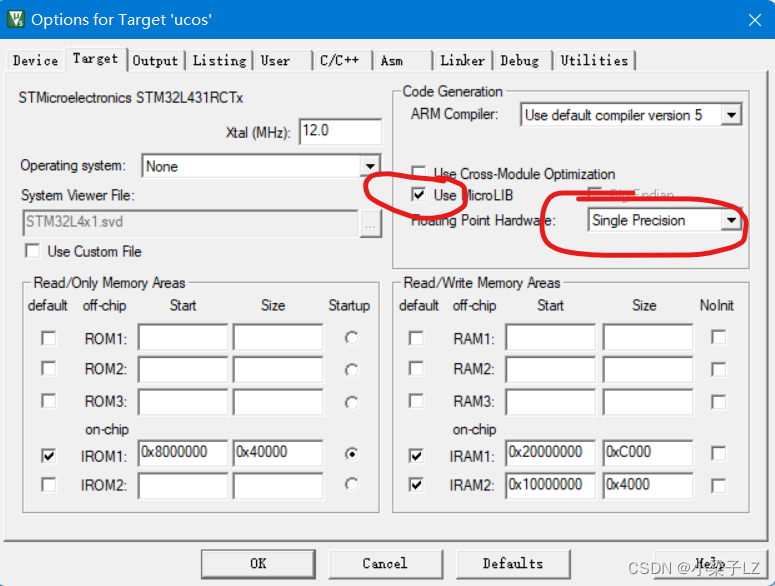

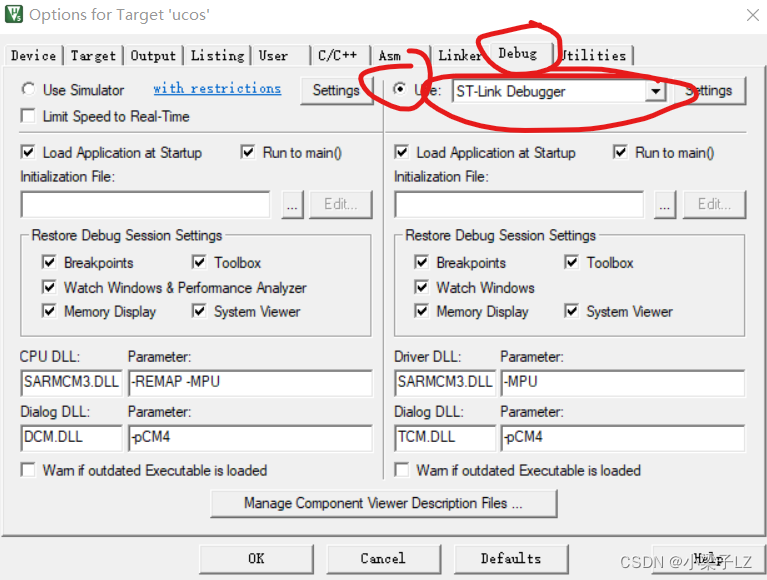

第九步在main.c创建任务,设置编译器,编译下载,现象为LED闪烁

/* USER CODE BEGIN Header */

/**

******************************************************************************

* @file : main.c

* @brief : Main program body

******************************************************************************

* @attention

*

* Copyright (c) 2022 STMicroelectronics.

* All rights reserved.

*

* This software is licensed under terms that can be found in the LICENSE file

* in the root directory of this software component.

* If no LICENSE file comes with this software, it is provided AS-IS.

*

******************************************************************************

*/

/* USER CODE END Header */

/* Includes ------------------------------------------------------------------*/

#include "main.h"

#include "gpio.h"

/* Private includes ----------------------------------------------------------*/

/* USER CODE BEGIN Includes */

#include "includes.h"

/* USER CODE END Includes */

/* Private typedef -----------------------------------------------------------*/

/* USER CODE BEGIN PTD */

/* USER CODE END PTD */

/* Private define ------------------------------------------------------------*/

/* USER CODE BEGIN PD */

static OS_TCB AppTaskStartTCB;

static CPU_STK AppTaskStartStk[APP_TASK_START_STK_SIZE];

/* USER CODE END PD */

/* Private macro -------------------------------------------------------------*/

/* USER CODE BEGIN PM */

/* USER CODE END PM */

/* Private variables ---------------------------------------------------------*/

/* USER CODE BEGIN PV */

/* ?????? */

void AppTaskStart (void *p_arg);

/* USER CODE END PV */

/* Private function prototypes -----------------------------------------------*/

void SystemClock_Config(void);

/* USER CODE BEGIN PFP */

/* USER CODE END PFP */

/* Private user code ---------------------------------------------------------*/

/* USER CODE BEGIN 0 */

/* USER CODE END 0 */

/**

* @brief The application entry point.

* @retval int

*/

int main(void)

{

/* USER CODE BEGIN 1 */

OS_ERR err;

OSInit(&err);

/* USER CODE END 1 */

/* MCU Configuration--------------------------------------------------------*/

/* Reset of all peripherals, Initializes the Flash interface and the Systick. */

HAL_Init();

/* USER CODE BEGIN Init */

/* USER CODE END Init */

/* Configure the system clock */

SystemClock_Config();

/* USER CODE BEGIN SysInit */

/* USER CODE END SysInit */

/* Initialize all configured peripherals */

MX_GPIO_Init();

/* USER CODE BEGIN 2 */

OSTaskCreate((OS_TCB *)&AppTaskStartTCB, /* Create the start task */

(CPU_CHAR *)"App Task Start",

(OS_TASK_PTR ) AppTaskStart,

(void *) 0,

(OS_PRIO ) APP_TASK_START_PRIO,

(CPU_STK *)&AppTaskStartStk[0],

(CPU_STK_SIZE) APP_TASK_START_STK_SIZE / 10,

(CPU_STK_SIZE) APP_TASK_START_STK_SIZE,

(OS_MSG_QTY ) 5u,

(OS_TICK ) 0u,

(void *) 0,

(OS_OPT )(OS_OPT_TASK_STK_CHK | OS_OPT_TASK_STK_CLR),

(OS_ERR *)&err);

OSStart(&err);

/* USER CODE END 2 */

/* Infinite loop */

/* USER CODE BEGIN WHILE */

while (1)

{

/* USER CODE END WHILE */

/* USER CODE BEGIN 3 */

}

/* USER CODE END 3 */

}

/**

* @brief System Clock Configuration

* @retval None

*/

void SystemClock_Config(void)

{

RCC_OscInitTypeDef RCC_OscInitStruct = {0};

RCC_ClkInitTypeDef RCC_ClkInitStruct = {0};

/** Configure the main internal regulator output voltage

*/

if (HAL_PWREx_ControlVoltageScaling(PWR_REGULATOR_VOLTAGE_SCALE1) != HAL_OK)

{

Error_Handler();

}

/** Initializes the RCC Oscillators according to the specified parameters

* in the RCC_OscInitTypeDef structure.

*/

RCC_OscInitStruct.OscillatorType = RCC_OSCILLATORTYPE_HSE;

RCC_OscInitStruct.HSEState = RCC_HSE_ON;

RCC_OscInitStruct.PLL.PLLState = RCC_PLL_ON;

RCC_OscInitStruct.PLL.PLLSource = RCC_PLLSOURCE_HSE;

RCC_OscInitStruct.PLL.PLLM = 1;

RCC_OscInitStruct.PLL.PLLN = 8;

RCC_OscInitStruct.PLL.PLLP = RCC_PLLP_DIV7;

RCC_OscInitStruct.PLL.PLLQ = RCC_PLLQ_DIV2;

RCC_OscInitStruct.PLL.PLLR = RCC_PLLR_DIV2;

if (HAL_RCC_OscConfig(&RCC_OscInitStruct) != HAL_OK)

{

Error_Handler();

}

/** Initializes the CPU, AHB and APB buses clocks

*/

RCC_ClkInitStruct.ClockType = RCC_CLOCKTYPE_HCLK|RCC_CLOCKTYPE_SYSCLK

|RCC_CLOCKTYPE_PCLK1|RCC_CLOCKTYPE_PCLK2;

RCC_ClkInitStruct.SYSCLKSource = RCC_SYSCLKSOURCE_PLLCLK;

RCC_ClkInitStruct.AHBCLKDivider = RCC_SYSCLK_DIV1;

RCC_ClkInitStruct.APB1CLKDivider = RCC_HCLK_DIV1;

RCC_ClkInitStruct.APB2CLKDivider = RCC_HCLK_DIV1;

if (HAL_RCC_ClockConfig(&RCC_ClkInitStruct, FLASH_LATENCY_2) != HAL_OK)

{

Error_Handler();

}

}

/* USER CODE BEGIN 4 */

static void AppTaskStart (void *p_arg)

{

CPU_INT32U cpu_clk_freq;

CPU_INT32U cnts;

OS_ERR err;

(void)p_arg;

CPU_Init();

BSP_Init(); /* Initialize BSP functions */

cpu_clk_freq = BSP_CPU_ClkFreq(); /* Determine SysTick reference freq. */

cnts = cpu_clk_freq / (CPU_INT32U)OSCfg_TickRate_Hz; /* Determine nbr SysTick increments */

OS_CPU_SysTickInit(cnts); /* Init uC/OS periodic time src (SysTick). */

Mem_Init(); /* Initialize Memory Management Module */

#if OS_CFG_STAT_TASK_EN > 0u

OSStatTaskCPUUsageInit(&err); /* Compute CPU capacity with no task running */

#endif

#ifdef CPU_CFG_INT_DIS_MEAS_EN

CPU_IntDisMeasMaxCurReset();

#endif

while (DEF_TRUE) { /* Task body, always written as an infinite loop. */

HAL_GPIO_TogglePin(GPIOA,GPIO_PIN_0);

OSTimeDly ( 1000, OS_OPT_TIME_DLY, & err );

}

}

/* USER CODE END 4 */

/**

* @brief This function is executed in case of error occurrence.

* @retval None

*/

void Error_Handler(void)

{

/* USER CODE BEGIN Error_Handler_Debug */

/* User can add his own implementation to report the HAL error return state */

__disable_irq();

while (1)

{

}

/* USER CODE END Error_Handler_Debug */

}

#ifdef USE_FULL_ASSERT

/**

* @brief Reports the name of the source file and the source line number

* where the assert_param error has occurred.

* @param file: pointer to the source file name

* @param line: assert_param error line source number

* @retval None

*/

void assert_failed(uint8_t *file, uint32_t line)

{

/* USER CODE BEGIN 6 */

/* User can add his own implementation to report the file name and line number,

ex: printf("Wrong parameters value: file %s on line %d\r\n", file, line) */

/* USER CODE END 6 */

}

#endif /* USE_FULL_ASSERT */

至此没有任何问题了,如果兄弟们有什么疑问,欢迎评论区留言,作者是个小白,太难的回答不了