ZYNQ(1)

名词

- 处理器系统部分Processor System(PS)

- 可编程逻辑部分Programmable Logic(PL)

- 软件开发套件 Software Development Kit ( SDK )

- IDE接口 Integrated Drive Electronics(IDE)

ATA接口(Advanced Technology Attachment)

这两个一样吧

丐版流程

基本文件生成

1.开发板型号选择

xc7z010clg400-1

50MHz

2.加源文件

Define Module。 加的 .v 文件

3.加管脚约束

加的 .xdc 文件

管脚分配:RTL Analysis -> Open Elaborated Design. Window -> I/O Ports.

//管脚约束

set_property PACKAGE_PIN " 引脚编号" [get_ports “端口名称”]

set_property PACKAGE_PIN K17 [get_ports {led[0]} ]

//电平信号约束

set_property IOSTANDARD " 电平标准" [get_ports “端口名称”]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

4.加时序约束

SYNTHESIS -> Run Synthesis 跑完以后别继续

SYNTHESIS -> Open Synthesized Design ->Constraints Wizard. 改sys_clk 50MHz然后就可以OK,Finish

改完以后 .xdc 文件更新了。Reload重新加载并保存。

5.编译

编译的过程可以细分为综合、布局布线、生成bit文件等。

Run Implementation布局布线。

可以直接点Generate Bitstream。

bit文件生成完成后,可以打开Project Summary页面的Table来查看板子上实际资源的使用情况。

LUT(查找表);F(Flip Flop寄存器); IO(管脚);BUFG(时钟Buffer)。

仿真验证

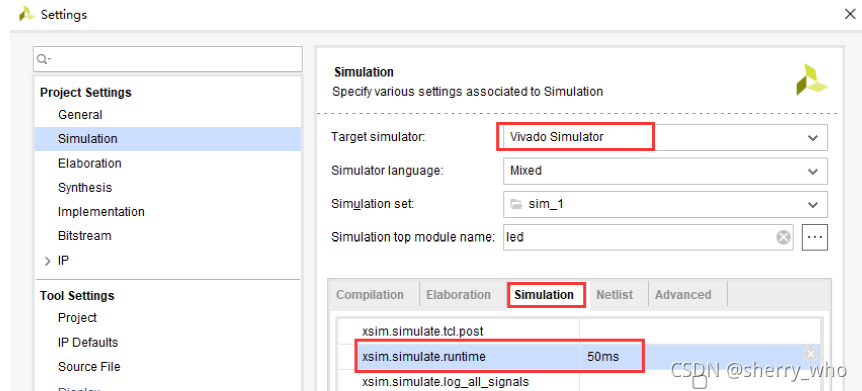

1.仿真设置

SIMULATION -> Simulation Settings

2.加激励文件

可以先不添加IO Ports

定义输入和输出信号。实例化模块。添加复位和时钟的激励。

在定义寄存器时:

寄存器在always块里使用:必须定义为reg类型

仅是用于连线或是直接赋值:需定义为wire类型

输入信号的类型不能定义为reg型.

3.仿真跑起来

SIMULATION -> Run Simulation -> Run Behavioral Simulation

要是想看的是中间的过渡信号,在Scope里面点一下,然后就可以出来一堆。

加到右边:Add Wave Window。

Restart按钮复位一下,再点击Run All按钮。

下载

简单看一看

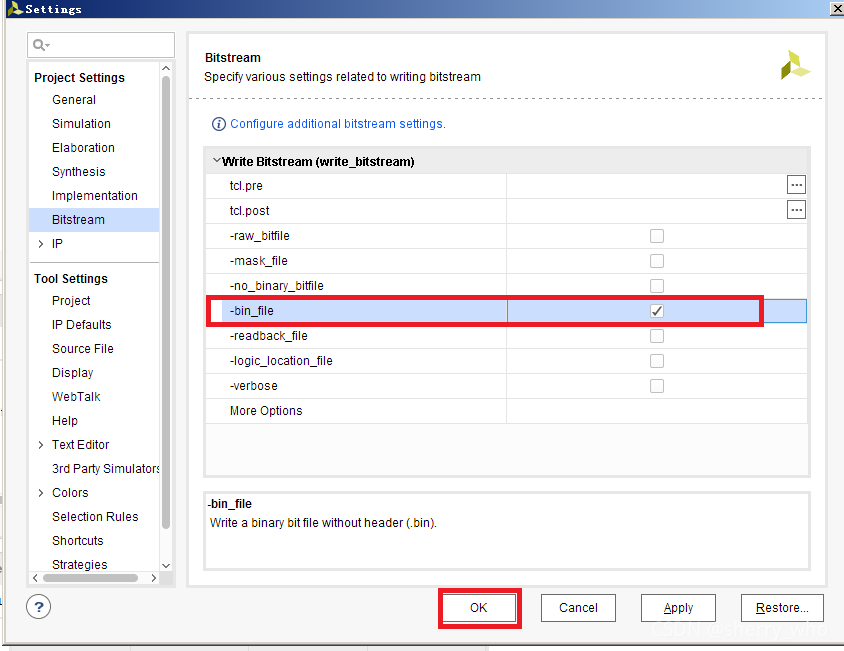

PROGRAM AND DEBUG -> Bitstream Settings

设置完成后单击Generate Bitstream生成bit和bin文件。

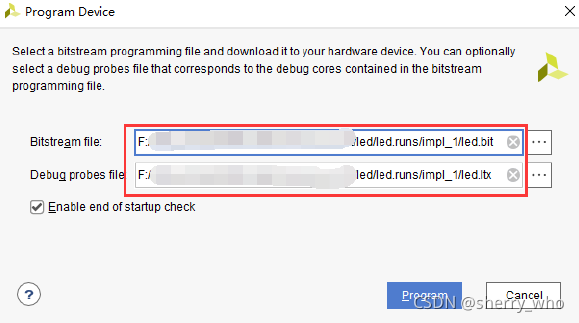

PROGRAM AND DEBUG -> Open target -> Auto Connect

连上以后Program Device,再点一点。Bit文件就下进去了,但是掉电不保存。

程序固化

ZYNQ程序固化与FPGA不同。得考虑PS部分。

在线调试—ILA IP

1.ILA IP在线调试

一. 添加

IP Catalog ->ila

二. 信息修改

- Component Name

- General Options

- Number of Probes 观察的信号数量 。

- Sample Data Depth采样深度—总共能存储数据的总量。

(Number of window) X (Window Data depth) = 总的存储数量

存储总量是1024,当(Window Data depth) =1024时,只能显示一个窗口的数据. - Probe_Ports

- Probe_Width 设置位宽。看一下采的数据是多少位的

三. 例化模块重新下程序

可以在 .veo 文件里找一下模板

源文件程序里面加进去,重新生成Bitstream文件。

重新下一下。bit 和 ltx 文件,点击 program。

四. 在线调试

- 点击运行看一看。

- 也可以触发采集,在Trigger Setup窗口点击 + 。

将Radix 改为 U ,也就是十进制,设置value值。再点运行。

2.MARK DEBUG

下面介绍在代码中添加综合属性,实现在线调试。

1. 将 ila 的例化部分注释掉。

2. 需要看的信号在定义前加 (* MARK_DEBUG=“true” *)

3. Run Synthesis

4. Setup Debug 。小小的设置一下Sample of data depth 然后可以完事了。

5. 保存以后在 .xdc 文件可以看见 ila 核约束

6. 重新生成Bitstream文件,下程序。

7. 其余同上。

参考文献

- CSDN Blog:Vivado下的集成逻辑分析仪ILA 入门

- cource_s1_ALINX_ZYNQ(AX7Z010_AX7Z020)开发平台基础教程V1.04