一、ARM指令流水线分析及伪指令

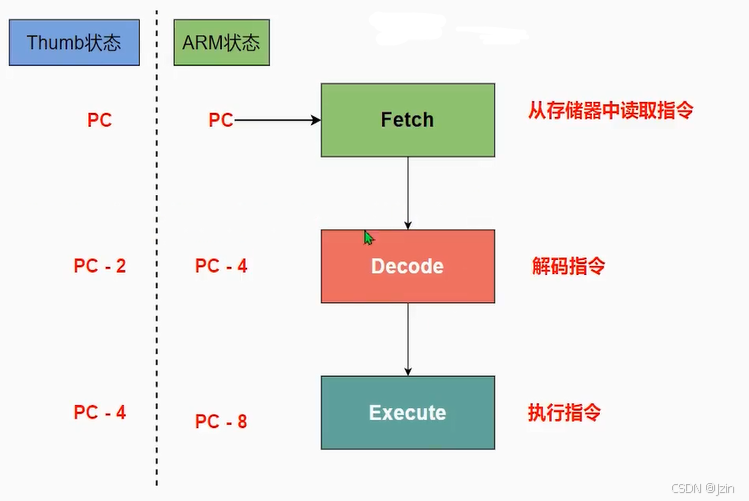

在ARM核中,为增加处理器指令流的速度,ARM7系列使用3级流水线。允许多个操作同时处理,而非顺序执行。不同的ARM核,流水线的级数是不一样的,ARM核版本越高,流水线级数越多。对于软件工程师编程而言,统一按照三级流水线来分析就可以了。

PC指向正被取指的指令,而非正在执行的指令

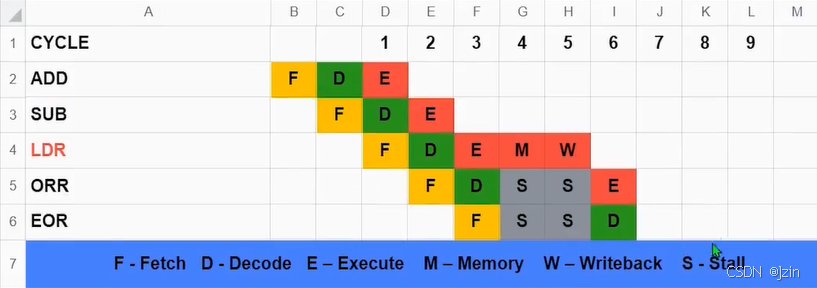

1. 最佳流水线

该例中用5个时钟周期执行了5条指令,所有的操作都在寄存器中(单周期执行)

指令周期数(CPI)=1

2. 内存访问指令流水线

该例中,用6周期执行了4条指令,指令周期数(CPI)=1.5

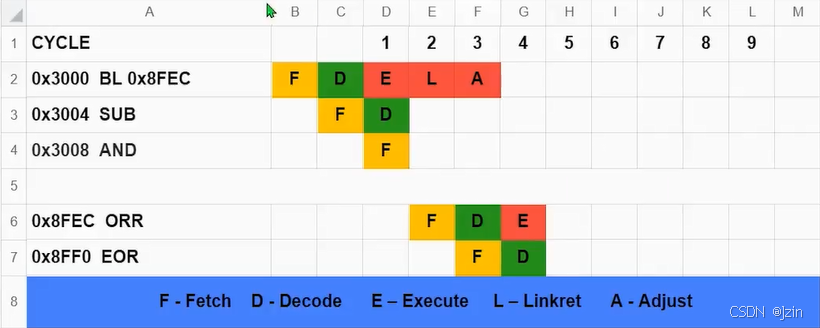

3. 分支流水线

4. ARM伪指令、汇编与C混合编程、Volatile关键字

伪指令定义:

为了方便程序员使用,编译器设计的指令,这个指令ARM核无法直接识别,需要编译器对他翻译成ARM核所能识别的指令。

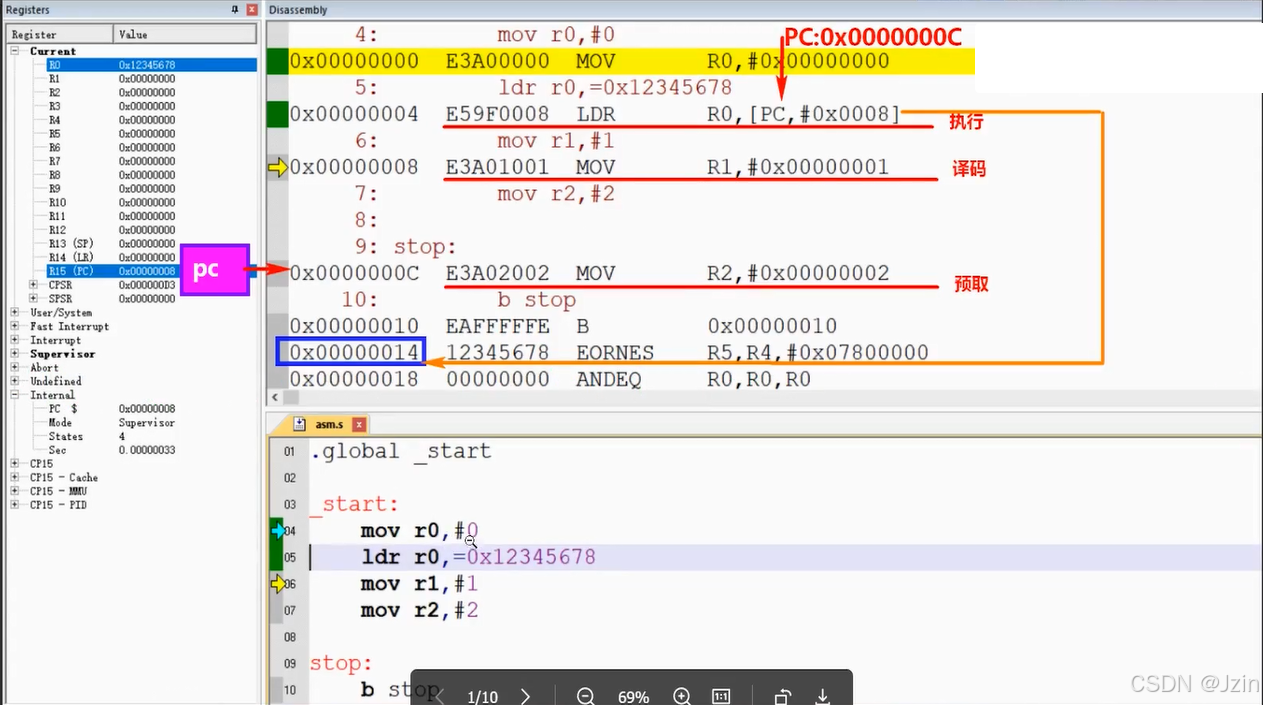

(1)LDR R0,=0x12345678分析

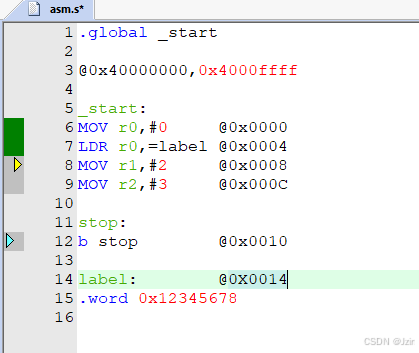

再次强调:PC指向正被取指的指令,而非正在执行的指令

如何看内存中的12345678

正在读取的LDR内存是0x0008 加上 PC所在的地址(因为LDR正在执行 所以pc等于0x0000000C预取的值)

也就是0x0008加上pc的值0x0000000C等于0x00000014

总结

编译器在编译的时候,将Idr r0,=0x12345678翻译成了ldr r0,[pc,#0x0008]这一条读内存的指令。根据PC的值加上偏移量算出0x12345678这个数据在内存的地址,然后使用Idr指令读取这个地址的数据。

(2)LDR R0,=Label 分析

1) 链接地址指定为0x0情况分析

0x00000018等于0x000C加上pc的值0x000C

注意 0x00000018的值是14 这是个值 是编译器算出来的一个值