vivado版本 2017.4(其它版本步骤基本相同)(官网步骤都有配图进入可查看)

(官网链接 https://wiki.analog.com/resources/fpga/docs/build)

1、下载no-os文件 2018_r1

https://github.com/analogdevicesinc/no-OS

2、下载hdl文件2018_r1

https://github.com/analogdevicesinc/hdl/releases

3、windows(linux查看官网)

安装Cygwin。因为HDL文件全是源文件,需要通过make工具生成vivado的工程文件和hdf文件。在Windows下安装cygwin。其它博客有很多相关安装教程。安装中选择git、make,不安装其他。

打开Cygwin窗口,输入路径。

export PATH=$PATH:/cygdrive/e/xilinx/Vivado/2016.4/bin

export PATH=$PATH:/cygdrive/e/xilinx/Vivado_HLS/2016.4/bin

export PATH=$PATH:/cygdrive/e/xilinx/SDK/2016.4/bin

export PATH=$PATH:/cygdrive/e/xilinx/SDK/2016.4/gnu/microblaze/nt/bin

export PATH=$PATH:/cygdrive/e/xilinx/SDK/2016.4/gnu/arm/nt/bin

export PATH=$PATH:/cygdrive/e/xilinx/SDK/2016.4/gnu/microblaze/linux_toolchain/nt64_be/bin

export PATH=$PATH:/cygdrive/e/xilinx/SDK/2016.4/gnu/microblaze/linux_toolchain/nt64_le/bin

export PATH=$PATH:/cygdrive/e/xilinx/SDk/2016.4/gnu/aarch32/nt/gcc-arm-none-eabi/bin

以上为模板。

我的:(直接复制)

export PATH=$PATH:/cygdrive/d/vivado17/Vivado/2017.4/bin

export PATH=$PATH:/cygdrive/d/vivado17/Vivado/2017.4/bin

export PATH=$PATH:/cygdrive/d/vivado17/SDK/2017.4/bin

export PATH=$PATH:/cygdrive/d/vivado17/SDK/2017.4/gnu/microblaze/nt/bin

export PATH=$PATH:/cygdrive/d/vivado17/SDK/2017.4/gnu/arm5/nt/gcc-arm-none-eabi/bin

export PATH=$PATH:/cygdrive/d/vivado17/SDK/2017.4/gnu/microblaze/linux_toolchain/nt_le/bin

export PATH=$PATH:/cygdrive/d/vivado17/SDK/2017.4/gnu/microblaze/linux_toolchain/nt64_le/bin

export PATH=$PATH:/cygdrive/d/vivado17/SDk/2017.4/gnu/aarch32/nt/gcc-arm-none-eabi/bin

(检验:

alias xmd=xmd.bat

alias xsct=xsct.bat

alias xsdb=xsdb.bat

which git

which make

which vivado

会返回正确路径)

以下为官网方式(选择文件。

cd cygdrive/e

克隆hdl文件库。(目录为adi)

mkdir adi

cd adi

git clone https://github.com/analogdevicesinc/hdl.git

选择自己分支。

cd hdl/

git status ## check for everything, including branch name

git checkout hdl_2016_r2 ## change to the hdl_2016_r2 branch

(结果显示:)

如果这是第一次克隆,那么您拥有所有最新的源文件。如果已经有一段时间了,您可以使用git pull或git rebase提取最新的源代码(如果有本地更改)。

git fetch

git rebase origin/hdl_2016_r2)

4、创建工程。Xilinx。(我下载好了文件,跳过上述步骤)

我的文件目录(HDL文件目录)

cd E:/daxia_ad9361/hdl-2018_r1/projects/fmcomms2

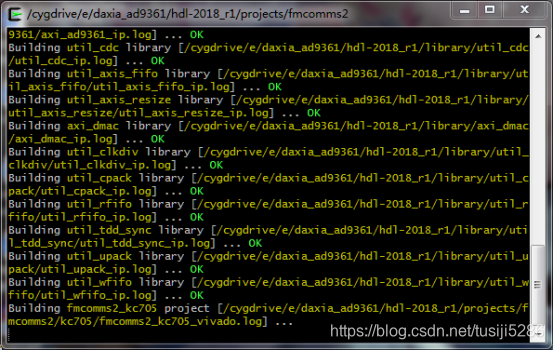

(直接make 创建的是kc705的工程 工程直接保存在hdl文件的原位置,或删除其他工程只留下zed)(此处我使用make -C zed)

make -C zed

我的:(失败就从头开始)大约一二十分钟。

*/无问题不看//以下为官网检查方法((make首先构建所有库,然后再构建项目。这假设已经正确地设置了工具和许可证。如果没有到达最后一行,则make无法构建一个或多个目标,它可能是库组件或项目本身。从’make’输出中无法收集到任何信息(除了哪个失败之外),实际的失败在日志文件中。因此,让我们看看如何分析构建日志文件和结果。

独立综合。

通过定义ADI_USE_OOC_SYNTHESIS系统变量,可以选择在构建过程中进行脱离上下文的合成。

export ADI_USE_OOC_SYNTHESIS=y

cd projects/daq2/zc706

make

这将分别从块设计中合成每个IP,并将其存储在一个公共缓存中以备将来重用。缓存位于ipcache文件夹中,并且对所有的项目都是通用的,这样可以加速相同项目的重新编译,或者加速基本设计中使用的公共块的编译时间。例如MicroBlaze为VCU118设计的基础设计,一旦编译,它将在其他项目上重用。使用IP缓存将加速OOC模式下每个项目的重新编译,因为缓存不会像正常编译流那样被清除。

检查库组件的构建和分析结果。

如果你仔细观察,你会看到它实际上在做什么。它进入一个库组件文件夹,然后以批处理模式调用“Vivado”。IP命令在源“Tcl”文件中,输出被重定向到日志文件。在下面的示例中,它是’axi_ad9144_ip。在’library/axi_ad9144’目录中记录’

*make[1]: Entering directory ‘/home/RKutty/gitadi/hdl/library/axi_ad9144’

rm -rf *.cache *.data *.xpr *.log component.xml *.jou xgui *.ip_user_files *.srcs *.hw .sim .Xil

vivado -mode batch -source axi_ad9144_ip.tcl >> axi_ad9144_ip.log 2>&1

如果您看到’make’返回一个错误(并停止),您必须首先检查这个日志文件的内容,然后再对我们疯狂。您还可以执行完整性检查,以查看生成的文件和日志文件内容。

ls -ltr library/axi_ad9144

tail library/axi_ad9144/axi_ad9144_ip.log

检查项目的构建和分析结果。

在上面的示例中,make做的最后一件事是构建项目。它与库组件完全相同。在本例中,日志文件名为‘daq2_zc706_vivado’。日志,位于’projects/daq2/zc706’目录中。

rm -rf *.cache *.data *.xpr *.log *.jou xgui *.runs *.srcs *.sdk *.hw *.sim .Xil .ip_user_files

vivado -mode batch -source system_project.tcl >> daq2_zc706_vivado.log 2>&1

make: Leaving directory ‘/home/RKutty/gitadi/hdl/projects/daq2/zc706’

快速(或详细)检查文件。

ls -ltr projects/daq2/zc706

tail projects/daq2/zc706/daq2_zc706_vivado.log))

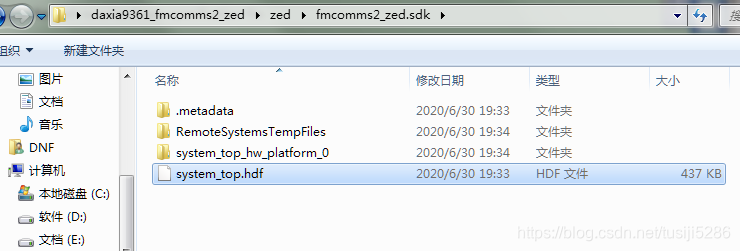

最后,如果项目构建成功,hdf文件应该在’sdk’文件夹中

现在你可以使用这个“hdf”文件作为你的no-OS和/或Linux版本的输入

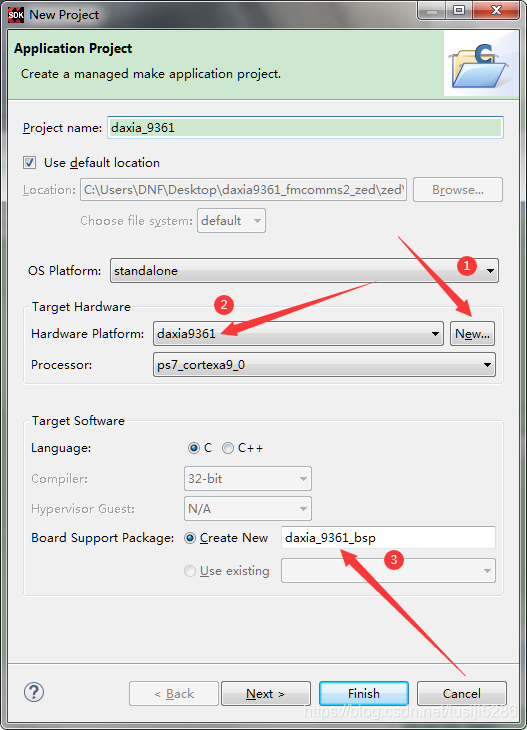

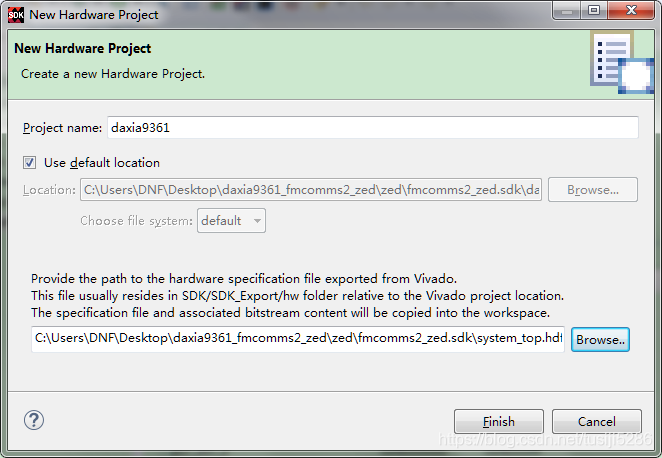

5、导入SDK

导入到SDK,启动SDK。

新建Application Project。

next 选择空白工程 finish。

(官 一些应用程序(例如FMCOMMSx),当使用Microblaze处理器时,需要增加堆大小来进行动态内存分配。确保堆大小至少是0x100000。)

将源代码文件(下载的no-os文件)复制到src目录中

从app_config.h(或config.h)头文件中取消注释所需的运营商供应商和CPU架构

如果在src中有多个文件夹,包括文件夹的所有路径:进入项目的设置,在C/ c++ Build—settings—Toolsettings—gcc compiler—Directories中添加所有文件夹的路径。(建议全部直接复制到src中)

SDK将自动生成项目,控制台窗口将显示生成的结果。如果生成未完成,则选择project–build automatically

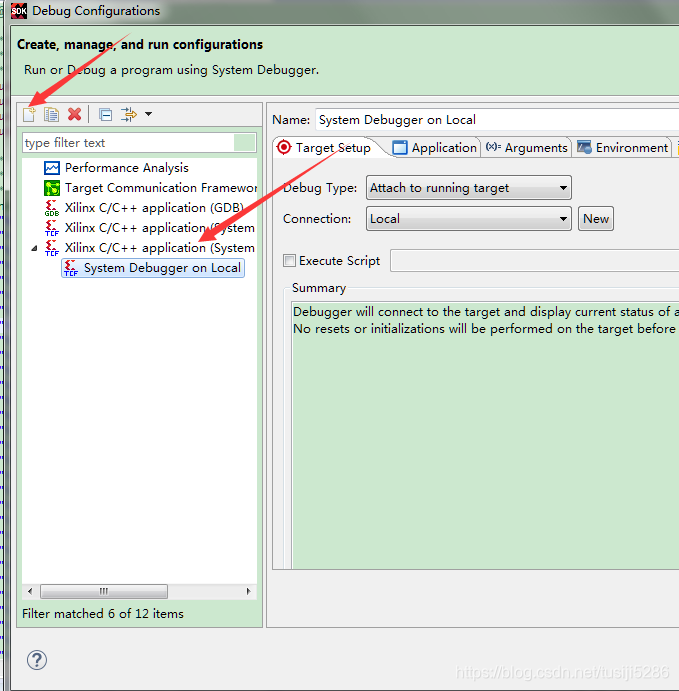

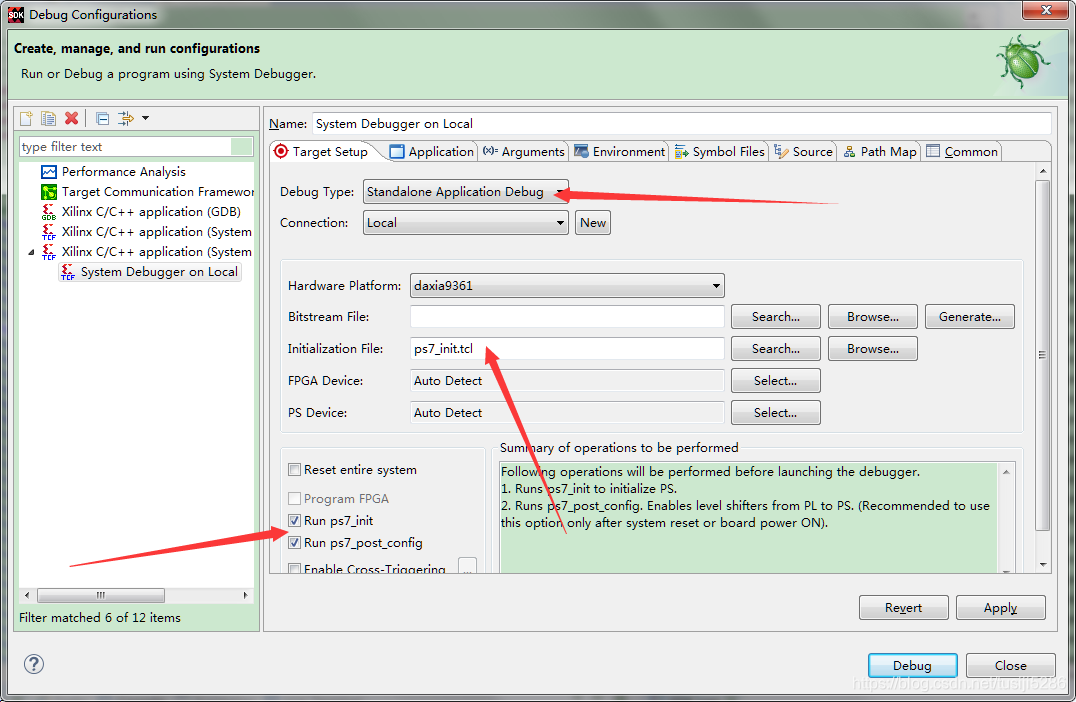

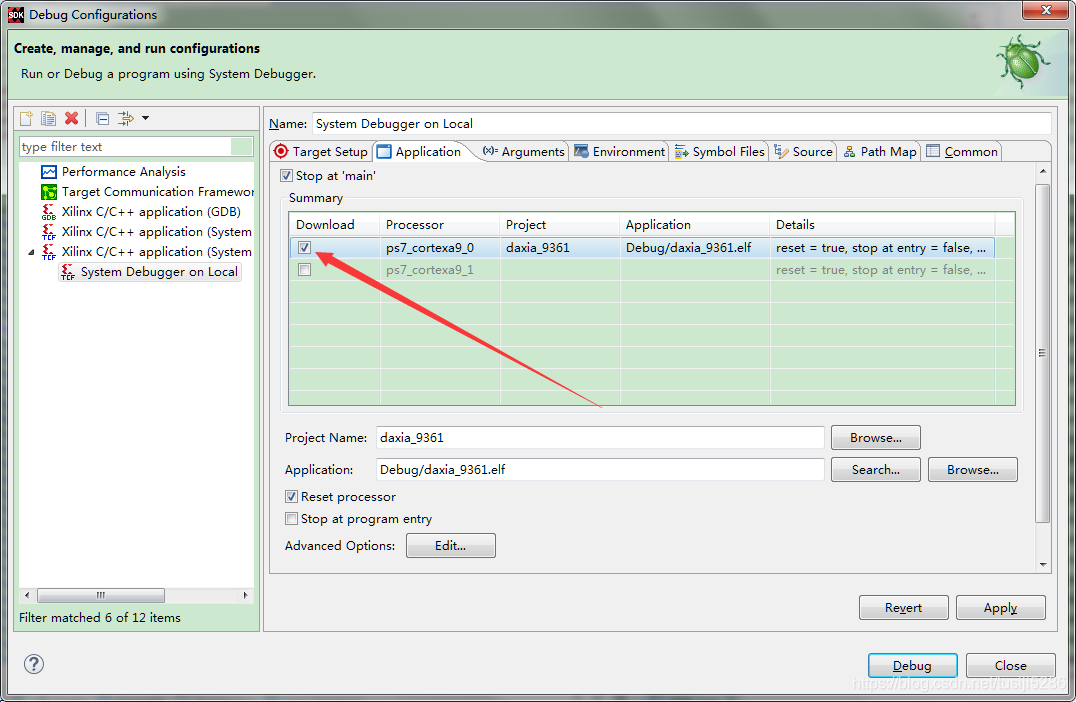

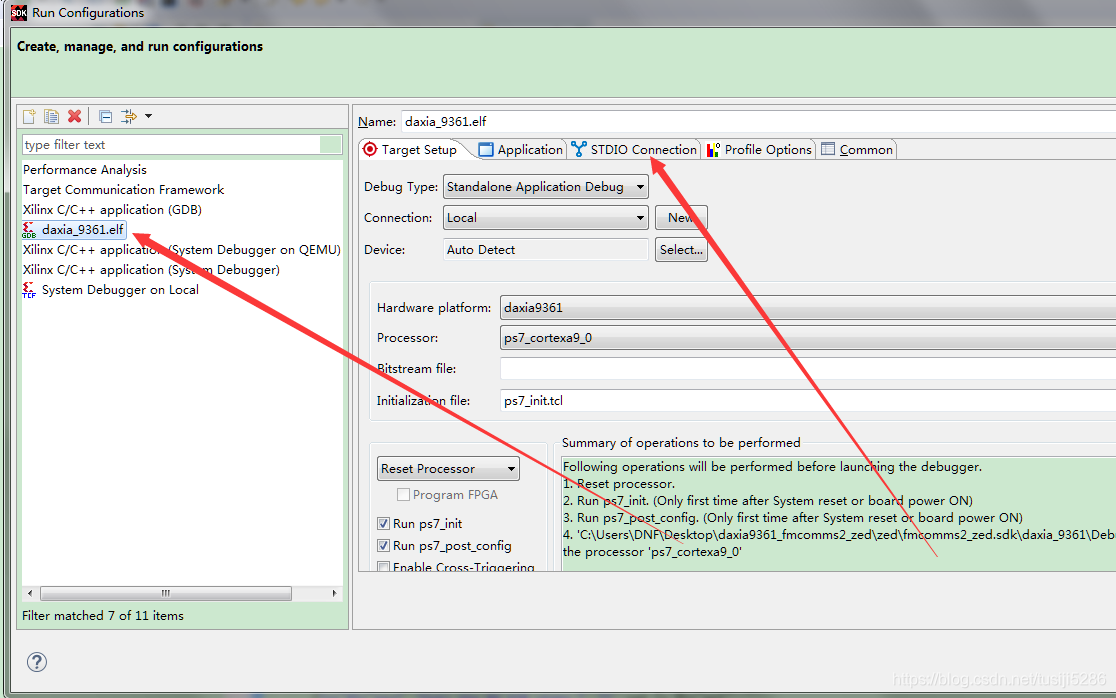

此时软件项目设置已经完成,可编程FPGA并将软件下载到系统中。点击Xilinx Tools→program FPGA。FPGA编程完成后,需要创建一个新的运行配置,选择Run→Run Configurations,在运行配置窗口中选择 Xilinx C/C++ application (System Debugger),点击左上角的new configuration按钮。

仅上图为ZNYQ必须的

然后就可以下载到板子上了,首次右键工程 run as选择GDB(使用串口 需要装好驱动并在run --run config中设置)

ad_iobuf

`timescale 1ns/100ps

module ad_iobuf (

dio_t,

dio_i,

dio_o,

dio_p);

parameter DATA_WIDTH = 1;

input [(DATA_WIDTH-1):0] dio_t;

input [(DATA_WIDTH-1):0] dio_i;

output [(DATA_WIDTH-1):0] dio_o;

inout [(DATA_WIDTH-1):0] dio_p;

genvar n;

generate

for (n = 0; n < DATA_WIDTH; n = n + 1) begin: g_iobuf

assign dio_o[n] = dio_p[n];

assign dio_p[n] = (dio_t[n] == 1'b1) ? 1'bz : dio_i[n];

end

endgenerate

endmodule

// ***************************************************************************

// ***************************************************************************