仿真工具:Vivado 2015.2

一、无符号数

1.高位溢出赋给一个位宽不够的数

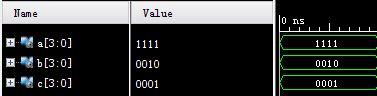

wire [3:0] a=4'b1111;//15

wire [3:0] b=4'b0010;//2

wire [3:0] c;

assign c = a + b;//17=10001wire [3:0] a=4'b1111;

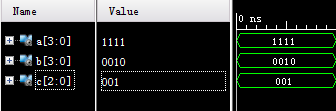

wire [3:0] b=4'b0010;

wire [2:0] c;

assign c = a + b;高位截断,保留低位

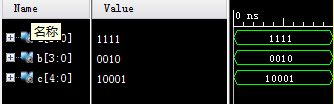

2.高位溢出赋给一个位宽足够的数

wire [3:0] a=4'b1111;

wire [3:0] b=4'b0010;

wire [4:0] c;

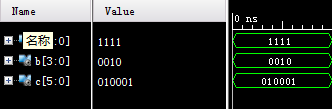

assign c = a + b;wire [3:0] a=4'b1111;

wire [3:0] b=4'b0010;

wire [5:0] c;

assign c = a + b;

结果正确。

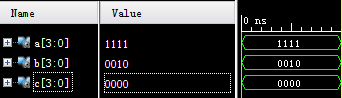

3.对中间结果移位

wire [3:0] a=4'b1111;

wire [3:0] b=4'b0010;

wire [3:0] c;

assign c =(( a + b) >> 1); //17=10001