💥💥💞💞欢迎来到本博客❤️❤️💥💥

🏆博主优势:🌞🌞🌞博客内容尽量做到思维缜密,逻辑清晰,为了方便读者。

⛳️座右铭:行百里者,半于九十。

📋📋📋本文目录如下:🎁🎁🎁

目录

基于正负序双dq旋转坐标系锁相环(DDSRF-PLL)模型研究

💥1 概述

参考:

DDSRF-PLL模型是一种锁相环(Phase-Locked Loop)模型,它基于正负序双dq旋转坐标系。DDSRF代表数字直接频率合成器(Direct Digital Synthesizer with Rotating Frame),PLL代表锁相环。

正负序双dq旋转坐标系是一种用于电力系统中三相电流和电压分析的坐标系。它将三相电流和电压转换为正序、负序和零序分量,使得分析和控制更加方便。

DDSRF-PLL模型结合了数字直接频率合成器和锁相环的特性。数字直接频率合成器用于产生需要的频率信号,而锁相环用于跟踪和锁定输入信号的相位和频率。

DDSRF-PLL模型在通信系统、无线电频率合成器和其他需要精确频率合成和相位锁定的应用中具有广泛的应用。它可以提供高精度的频率合成和相位锁定功能,使得系统能够更好地跟踪和同步输入信号。

锁相环是指通过硬件电路或软件计算模块动态检测电网电压输入信号相位信息,并实现输出信号与电网电压输入信号相位同步锁定的闭环控制系统"5]。锁相环有多种分类方式,按照控制结构划分,可以分为开环和闭环锁相环;按照应用场景划分,可以分为单相和三相锁相环;按照实现方式划分,可以分为硬件和软件锁相环;按照工作原理划分,可以分为过零鉴相和矢量变换锁相环。虽然锁相环可以根据不同分类方式划分成多种类别,但是任何锁相环系统都由三种基本功能模块构成:鉴相器(Phase Detector,PD)、环路滤波器(Loop Filter,LF)和压控振荡器(Voltage Control Oscillator,vCO)116]。

随着微处理器(单片机、ARM、DSP等)技术的不断发展,软件锁相环的处理速度及精度得到了很大的提高,同时因其具有拓展简便、移植灵活以及可编程等优点,得到了广泛应用18]。在软件锁相环技术中,SRF-PLL具有良好的动态性能,是电网电压同步信号检测方面主流的锁相环技术[19]。图1.3是 SRF-PLL的结构框图,在电网平衡条件下,SRF-PLL可以准确、迅速检测电网电压频率和相位。但是,在电网不平衡条件下,SRF-PLL的输出存在相位波动[2]。针对这一问题,研究人员从锁相环构成的角度出发,考虑电网电压不平衡条件下的电网负序及谐波电压影响等因素,对 SRF-PLL进行了改进。

基于正负序双dq旋转坐标系锁相环(DDSRF-PLL)模型研究

一、DDSRF-PLL的基本原理与结构

DDSRF-PLL(Decoupled Double Synchronous Reference Frame Phase-Locked Loop)是一种针对电网不平衡条件设计的改进型锁相环技术。其核心思想是通过双同步旋转坐标系(正序和负序)分离电网电压的正负序分量,并通过解耦网络消除两者间的耦合干扰,从而实现对电网频率和相位的精确跟踪。

-

基本结构

DDSRF-PLL由以下关键模块构成:- 双Park变换:将三相电压分别转换到正序(旋转角度为θ)和负序(旋转角度为-θ)的dq坐标系中。

- 低通滤波器(LPF) :用于提取正负序分量的直流项,并衰减2倍频(2ω)的交流耦合项。

- 解耦网络:通过逆Park变换和信号减法,进一步消除残留的振荡分量,实现正负序分量的完全解耦。

- SRF-PLL核心:基于传统同步参考帧锁相环,利用解耦后的正序q轴分量(Vq+)进行相位锁定。

-

动态响应优化

低通滤波器的截止频率(ωf)直接影响动态性能。研究表明,当ωf = ω0/2(ω0为电网基频,如50 Hz或400 Hz)时,系统在响应速度与过冲之间达到最优平衡。例如,在400 Hz电网中,ωf设为200 Hz,可有效兼顾跟踪速度和稳定性。

二、正负序双dq旋转坐标系的数学表达

-

正负序分量分解

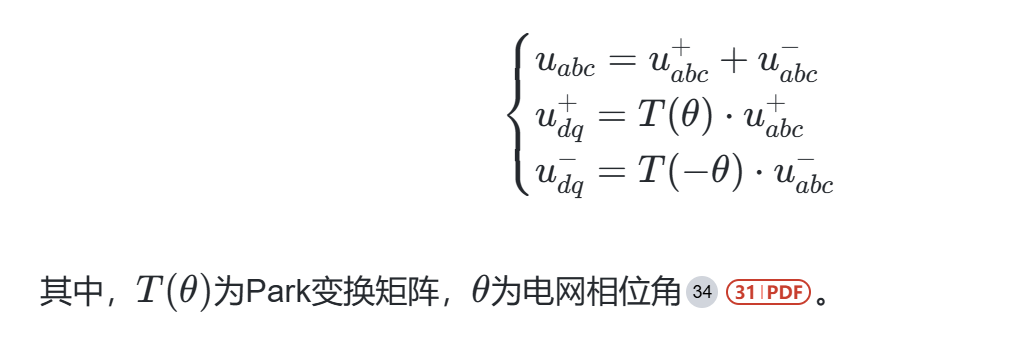

三相不平衡电压可分解为正序、负序和零序分量。对于无中线系统,零序分量可忽略,仅需处理正负序分量: -

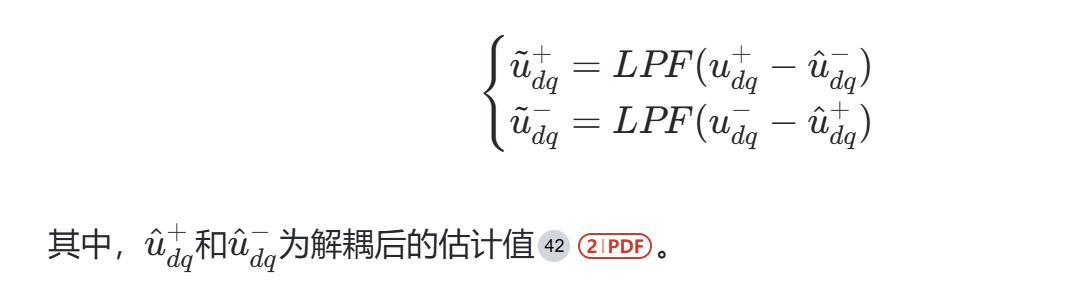

解耦过程

在正序dq坐标系中,负序分量表现为2倍频交流项,反之亦然。通过低通滤波和逆变换,可分离出纯直流分量:

三、DDSRF-PLL在电力系统中的应用场景

-

电网故障检测与同步

- 在电压跌落、短路等不平衡条件下,DDSRF-PLL可快速分离正负序分量,为电流控制器提供准确的参考信号,确保功率流的稳定性。

- 例如,在相间短路故障中,DDSRF-PLL能精确计算vd+vd+、vq+vq+、vd−vd−、vq−vq−的实际值,支持故障定位与保护。

-

新能源并网控制

- 在分布式发电(DG)系统中,DDSRF-PLL用于跟踪电网相位,适应电压不平衡、谐波干扰等复杂工况,提升并网逆变器的鲁棒性。

- 仿真表明,在频率突变(如50 Hz→60 Hz)时,DDSRF-PLL仍能准确跟踪系统频率,动态响应时间优于传统SRF-PLL。

-

谐波抑制与动态补偿

- 通过解耦网络,DDSRF-PLL可抑制低次谐波(如3次、5次)对相位检测的影响,但在高次谐波或直流偏置下需结合附加滤波器(如陷波器)。

四、DDSRF-PLL的设计方法

-

关键参数设计

- PI控制器参数:例如,某设计中采用kp=−1.61 V−1kp=−1.61V−1、ki=−545 Wb−1ki=−545Wb−1,实现80 Hz带宽,平衡动态响应与抗噪能力。

- 滤波器优化:采用二阶广义积分器(SOGI)或滑动平均滤波器(MAF)增强谐波抑制能力。

-

改进型拓扑

- 在鉴相环节引入静止坐标系锁相环(如αβ-PLL),通过Park逆变换将旋转坐标系信号转换为静止坐标系信号,进一步降低高次谐波干扰。

五、仿真验证案例

-

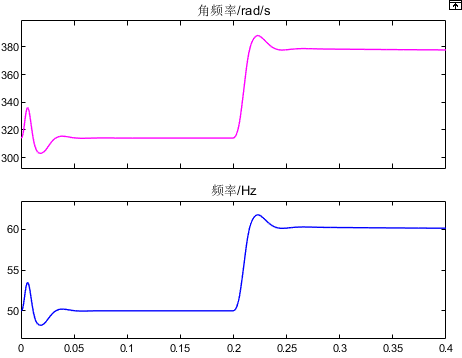

频率突变测试

- 在0.2秒时将系统频率从50 Hz切换至60 Hz,仿真显示DDSRF-PLL能快速跟踪频率变化,稳态误差小于0.1 Hz。

-

短路故障仿真

- 模拟A-B相短路故障,DDSRF-PLL输出的正序分量(vq+vq+)保持稳定,而传统SRF-PLL因耦合项存在明显振荡。

-

谐波环境测试

- 在含5% 5次谐波的电网中,DDSRF-PLL的相位检测误差较SRF-PLL降低70%,验证其抗谐波能力。

六、总结与展望

DDSRF-PLL通过双坐标系解耦技术,显著提升了电网不平衡条件下的相位检测精度,广泛应用于故障保护、新能源并网等领域。未来研究方向包括:

- 高次谐波适应性:结合自适应滤波算法或深度学习优化参数。

- 多目标协同控制:在解耦网络中集成频率自适应机制,应对电网频率波动。

📚2 运行结果

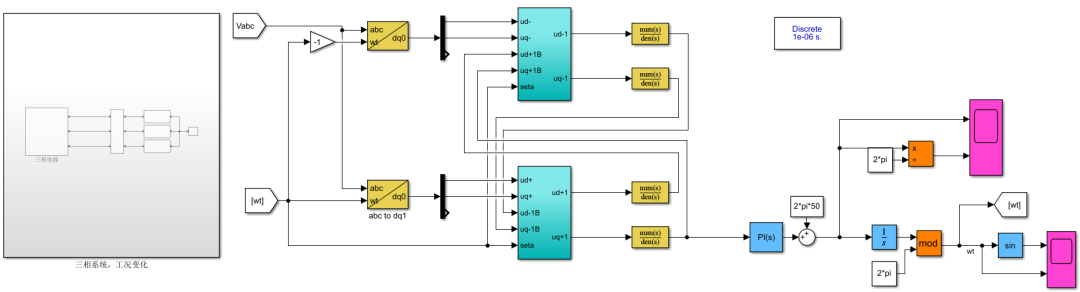

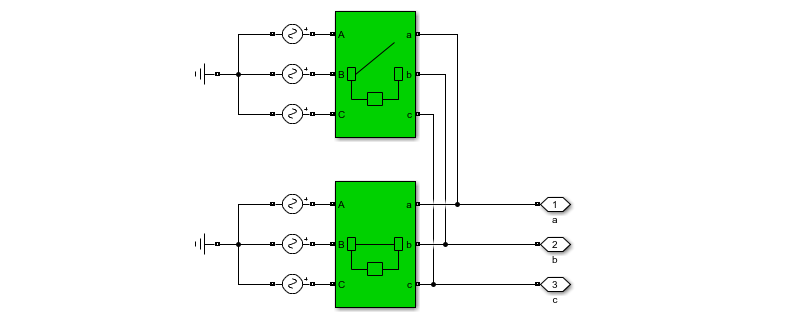

2.1 仿真模型搭建

在0.2秒时改变系统频率由50Hz变为60Hz.

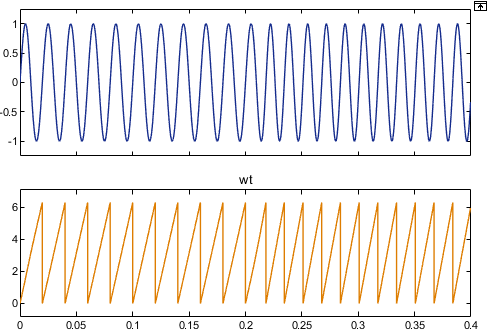

2.2 仿真波形

由图可知,当系统频率发生改变时,DDSRF-PLL能够准确跟踪系统频率。

🎉3 参考文献

文章中一些内容引自网络,会注明出处或引用为参考文献,难免有未尽之处,如有不妥,请随时联系删除。

[1]冯海江. 电网不平衡下锁相环技术的研究[D].大连海事大学,2017.