hls浮点协处理:在应用中如果出现需要进行大量浮点或其它类型数据运算的情况,此时占用大量CPU时间,如果将这类算法放到FPGA,CPU只需要发起请求和读取结果,将缩短时间。这里的hls ip模块由CPU指定float类型数据存放地址和数据长度,求求它们的平均值。计算完成后通过中断方式通知CPU。

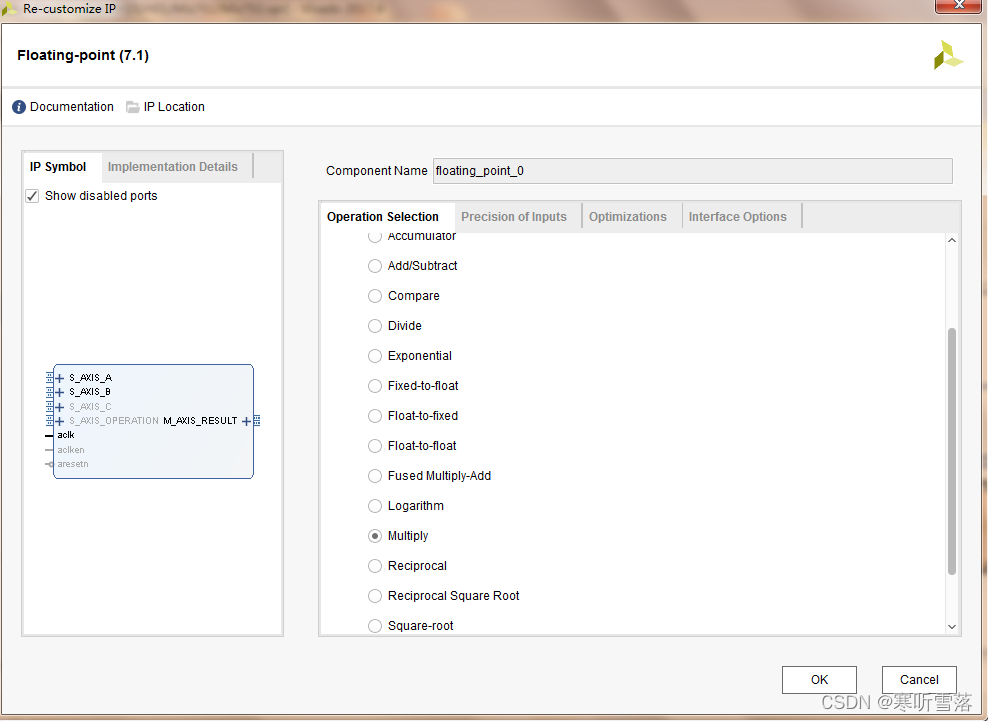

FPGA开发遇到碰到浮点数处理,使用浮点数运算IP(Floating-point),这个IP为AXI接口,输入和输出都是IEEE 754格式,就是计算机表示浮点数的格式。配置如图所示:

32位十进制转成浮点数:

floating_fix32_to_float fix_to_float_time_vx

(

.aclk(clk_out1),

// input wire aclk

.s_axis_