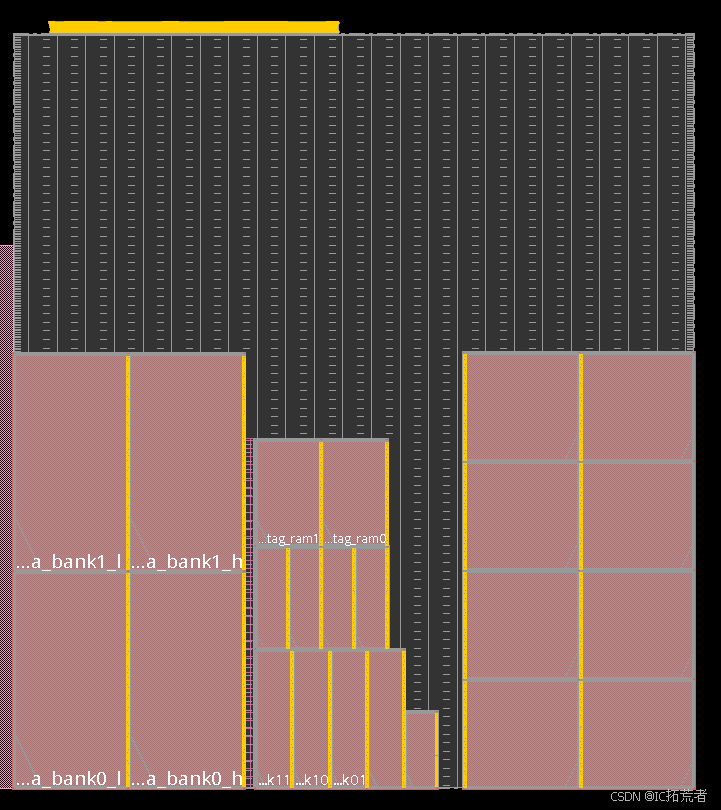

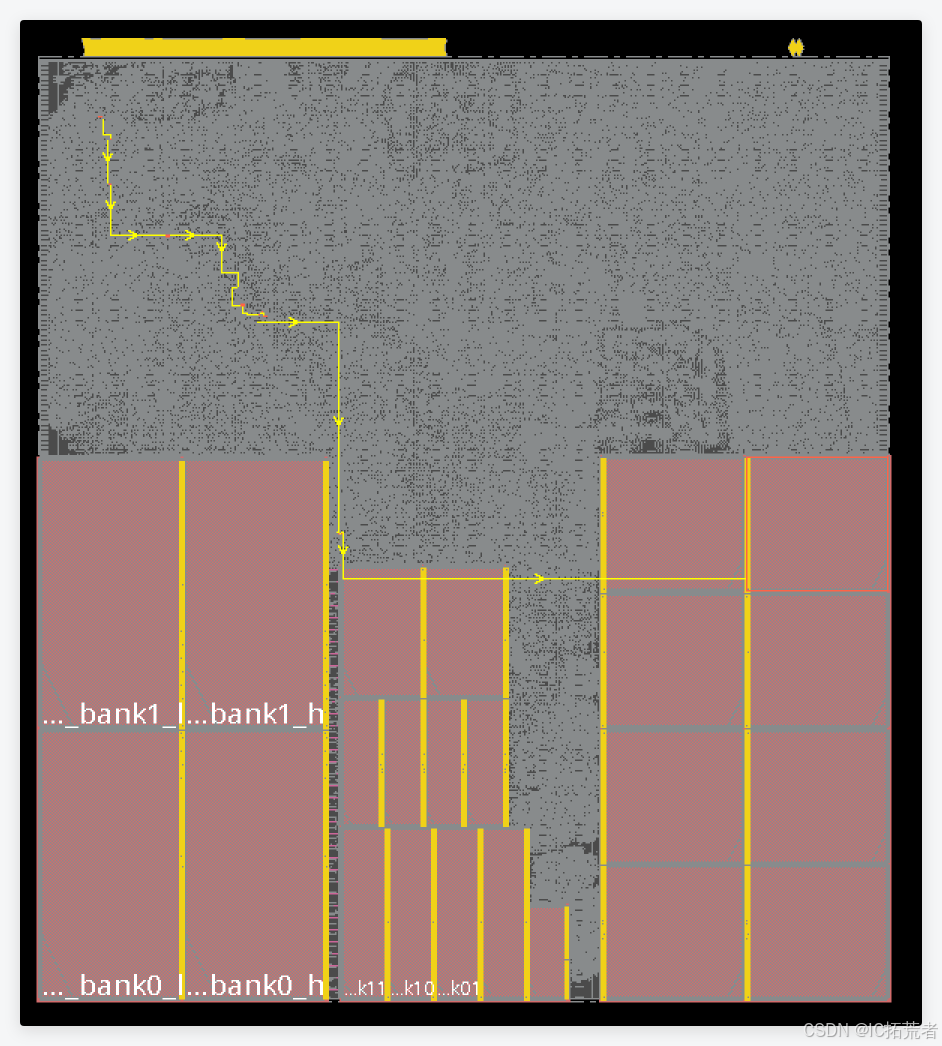

下图所示为咱们社区a7core后端训练营学员的floorplan。

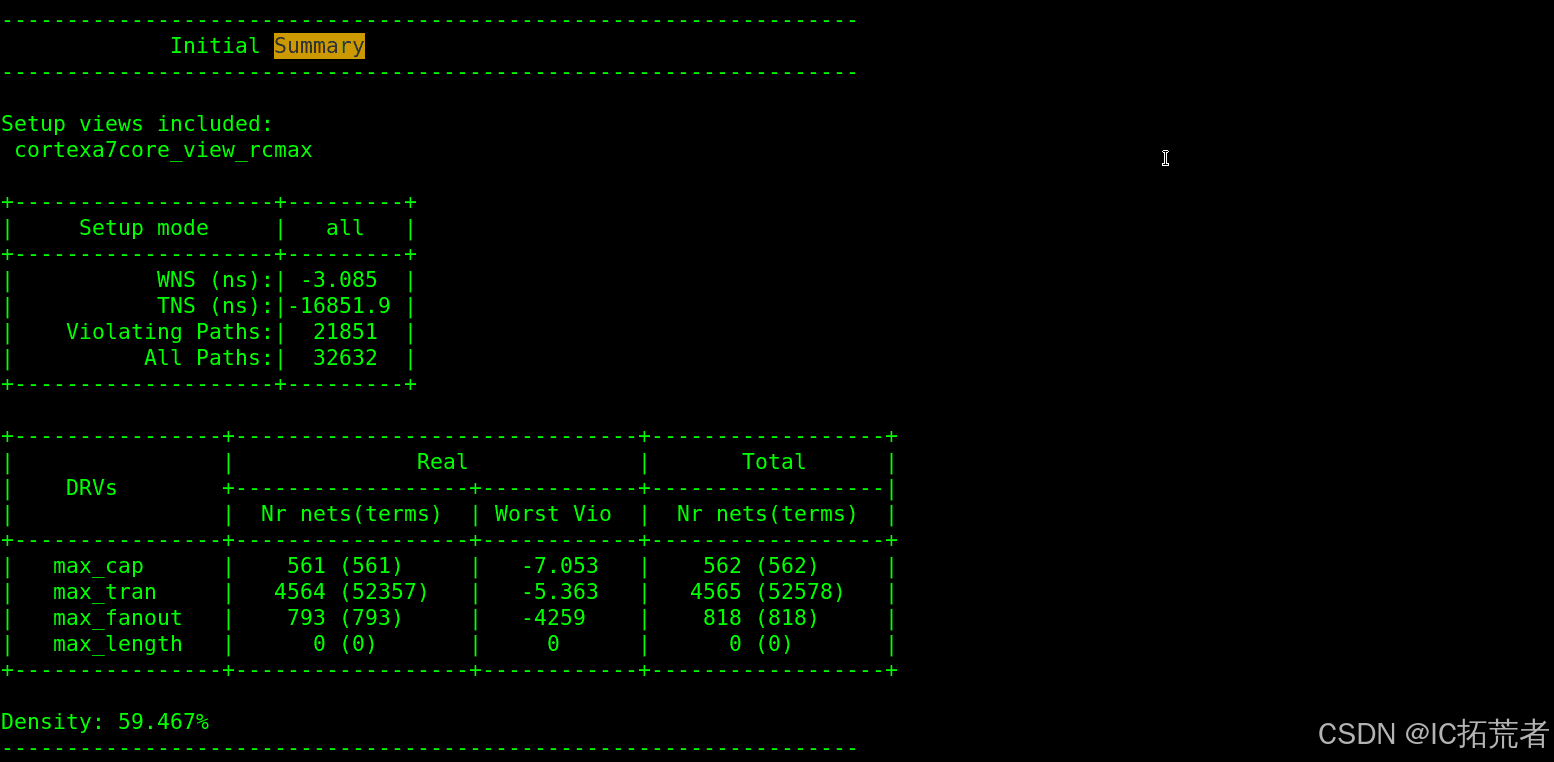

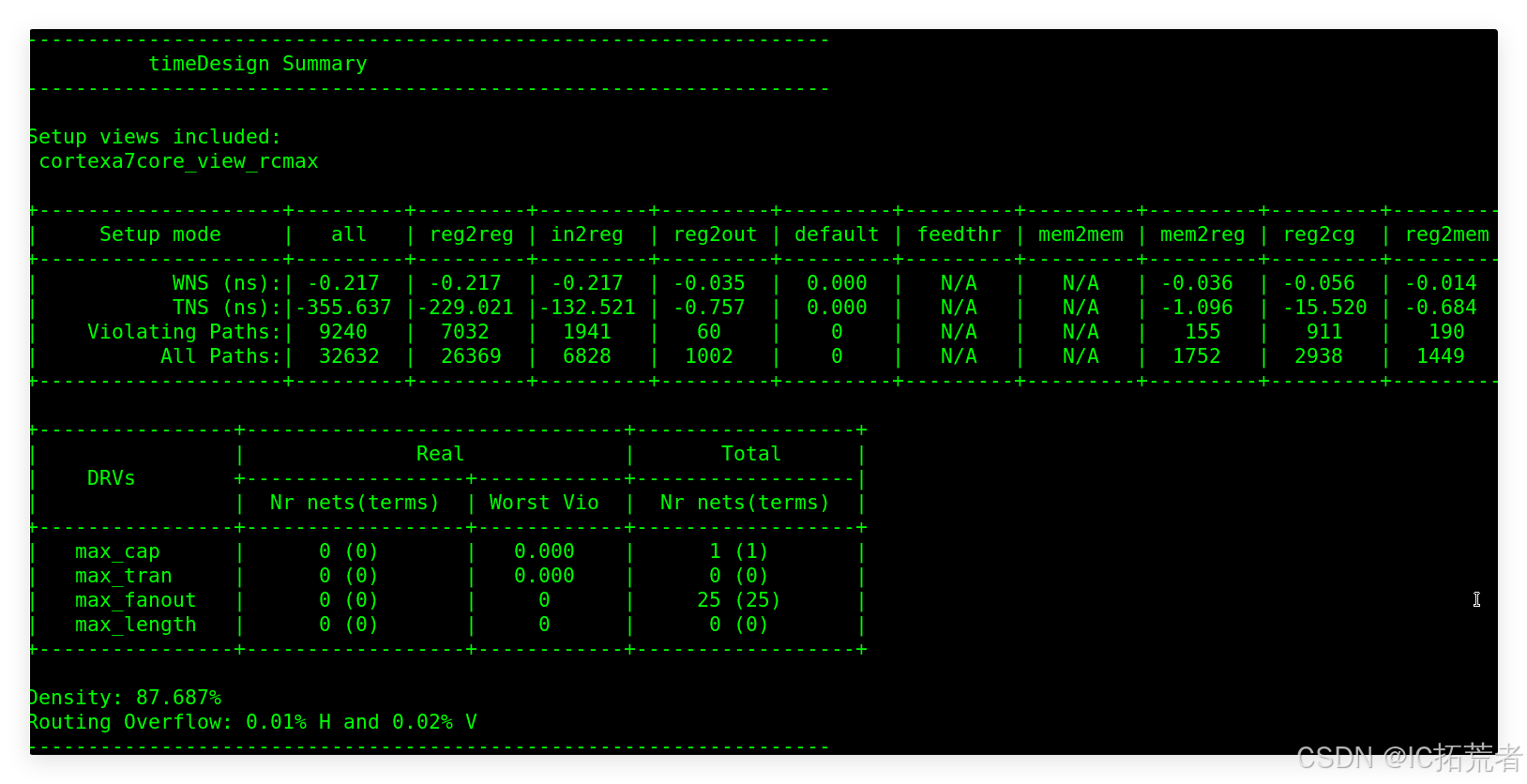

该学员跑placement前density是59.467%,但跑完place后density飙升到87.68%。

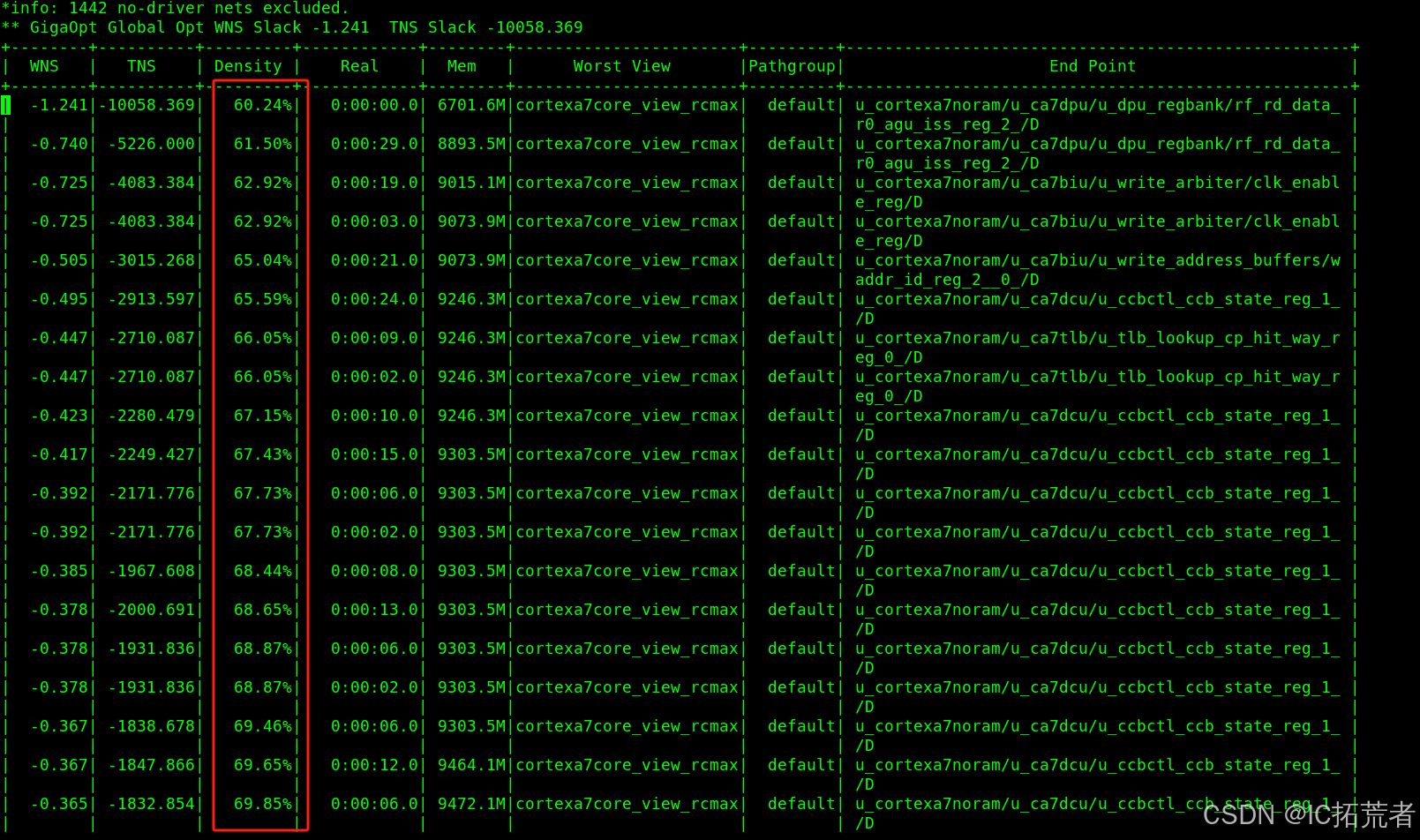

仔细查看place过程中的log就可以发现Density一路飙升!

数字IC后端物理验证PV | TSMC 12nm Calibre Base Layer DRC案例解析

另外附上reg2mem的一条timing path。

【数字IC后端问题讨论】

1)欢迎大家谈谈自己遇到这种case,你会从哪些方面分析?

2)当前floorplan需要改进的地方有哪几个?

3)基于当前floorplan实现的结果容易有哪些问题?