一、 Cadence Allegro PCB SI 简介 ....................................................................................... 3

(一) 高速 PCB 设计流程 .......................................................................................................................................... 3

二、 Allegro PCB SI 的后仿真 .................................................................................................. 4

(一) 准备仿真模型和其他需求 .............................................................................................................................. 4

1 . 获取所使用元器件的仿真模型 ..................................................................................................................... 5

( 1 ) 通过官网,供应商等渠道获取 IBIS 模型 ............................................................................................ 5

( 2 ) IBIS 模型转化为 DML 模型 .................................................................................................................... 5

( 3 ) 通过 Allegro 建立简单 DML 模型以及模型分配 ................................................................................. 7

( 4 ) 通过 Allegro 建立复杂 DML 模型以及模型分配 ............................................................................... 11

2 . 了解 PCB 的布线规则以及原理图部分逻辑 ................................................................................................ 15

(二) 仿真配置 ....................................................................................................................................................... 15

1 . 使用 SI Design Setup 配置 ................................................................................................................... 17

2 . 选择需要配置的信号线 ............................................................................................................................... 17

3 . 设置仿真库 ................................................................................................................................................... 20

4 . 设置电源和地网络 ....................................................................................................................................... 22

5 . 设置叠层 ....................................................................................................................................................... 27

6 . 设置元器件类别 ........................................................................................................................................... 30

7 . 为元器件分配和创建模型 ........................................................................................................................... 31

8 . 设置差分对 ................................................................................................................................................... 35

9 . 设置仿真参数 ............................................................................................................................................... 35

10 . SI Design Audit 相关 ........................................................................................................................ 44

11 . 提取拓扑 .................................................................................................................................................... 46

(三) 后仿真报告结果验证 ................................................................................................................................... 50

1 . 信号波形 ....................................................................................................................................................... 50

2. 反射报告,延时报告以及同步噪声报告...................................................................................................52

一、Cadence Allegro PCB SI简介

Allegro PCB SI是Cadence SPB系列EDA工具之一,针对电路板级的信号完整性和电源完整性提供了一整

套完善、成熟而强大的分析和仿真方案,并且和Cadence SPB的其他工具一起,实现了从后端到后端、约束驱

动的高速PCB设计流程。

信号完整性和电源完整性的仿真按照在这个设计流程中所处的阶段可以分为后仿真和后仿真,本文会介绍

Allegro PCB SI在后仿真阶段基本的设计流程和操作步骤,并重点介绍其中的配置和仿真项目操作环节。

后仿真是在PCB布线完成以后,对已经完成的关键网络进行仿真验证的过程。可以检查实际的物理执行过

程(布局布线)是否违背设计意图;过程。可以检查实际的物理执行过程(布局布线)是否违背设计意图;或

是已知的改动,通过仿真来验证这种改动给高速设计带来的影响。

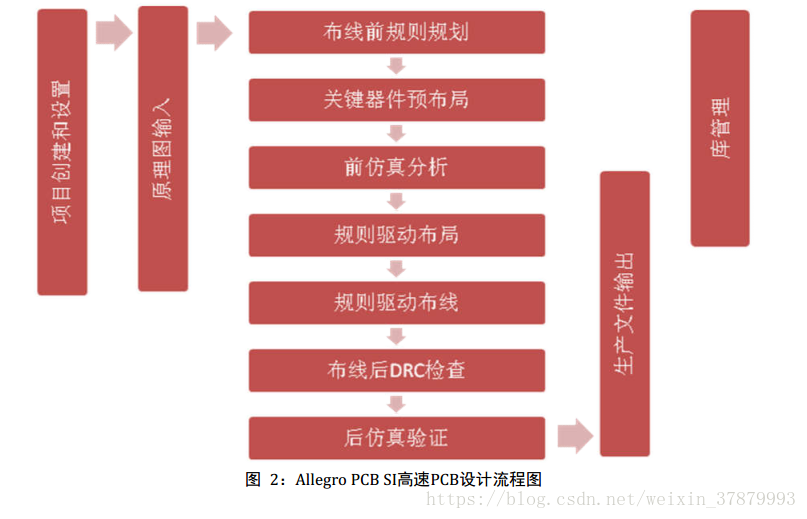

(一)高速PCB设计流程

传统的PCB设计流程如下图所示:

而引入的Allegro PCB SI仿真工具后的设计流程改进为:

二、Allegro PCB SI的后仿真

后仿真,顾名思义,后仿真是在PCB布线完成以后,对已经完成的关键网络进行仿真验证的过程。可以检

查实际的物理执行过程(布局布线)是否违背设计意图;过程。可以检查实际的物理执行过程(布局布线)是

否违背设计意图;或是已知的改动,通过仿真来验证这种改动给高速设计带来的影响。

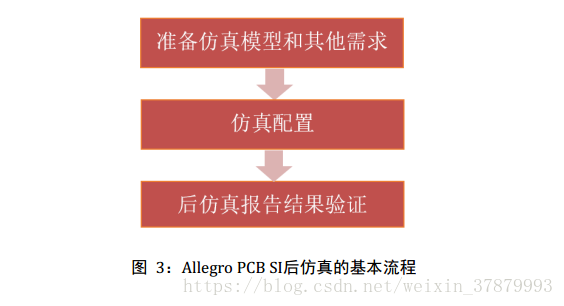

使用Allegro PCB SI进行后仿真的基本流程如下:

(一)准备仿真模型和其他需求

在本阶段,我们需要为使用Allegro PCB SI进行后仿真做如下准备工作:

下面,我们会以一个实际的电路板为例,介绍后仿真在Allegro PCB SI 16.6中的具体执行过程。

案例电路板:TX2P_P0_20171225,对其HDMI的差分信号进行延时以及反射分析。

1. 获取所使用元器件的仿真模型

(1)通过官网,供应商等渠道获取IBIS模型

https://www.maximintegrated.com/cn/design/tools/modeling-simulation/ibis/index.cfm

http://www.analog.com/cn/design-center/simulation-models/ibis-models.html

(2)IBIS模型转化为DML模型

信号完整性仿真大多针对由芯片IO、传输线以及可能存在的接插件和分立元件所构成的信号网络系统,为

了实现精确的仿真,仿真模型的精确性是首先需要保证的。一般情况下,Allegro PCB SI会执行传输线和分立

元件的建模,而芯片IO和连接器的模型通常会由原厂提供。

当后业内常见的芯片IO模型有两种格式,IBIS模型和HSPICE模型;常见的连接器模型也是两种,SPICE

(HSPICE)模型和S参数模型。Allegro PCB SI支持包括上述四种模型在内业界流行的仿真模型,但一般都需要

转化为Cadence自己的DML(Device Modeling Library)后才能使用。

Allegro PCB SI在仿真时需要将仿真模型都转变成DML模型格式这一做法,区别于大多数EDA软件,这种

做法可以说是有利有弊。弊,很明显,就是多一个额外的步骤,虽然这一步骤非常简便;利,则是有利于仿真

库的管理,做到仿真库和原始模型文件的隔离,并且在文件格式转换的同时也执行了模型的校验。在大多数情

况下,外部模型格式到Cadence DML模型格式的转换还是非常方便的,只需要用Cadence SPB系列工具包中

的Model Integrity软件打开模型文件,然后点击转换到DML即可。

可以有两种方法处理:

其一,在Model Integrity界面下或Allegro PCB SI界面下将IBIS模型转换成DML格式,供之后的仿真调用;

其二,从Cadence SPB 16.5版本开始,Allegro PCB SI名义上也直接支持IBIS模型,所以可以保留现有的

两个IBIS文件不做转换,然后在之后的仿真中直接调用。之所以说是“名义上”,因为事实上Allegro PCB SI

还是执行了转换,只是这个转换的过程在分配模型的同时一起执行了,没有摆在明面上。

我们先来看看如何使用Model Integrity转换IBIS模型。

1. 在开始菜单找到 Model Integrity快捷方式,或者在目录%CDSROOT%\tools\pcb\bin(其

中,%CDSROOT%是Cadence SPB的安装目录,例如D:\Cadence\SPB_16.6)下找到

modelintegrity.exe执行文件,点击即打开Model Integrity窗口。

2. 点击File->Open打开寄存器的IBIS模型文件EA32882_1p6.ibs;

3. 右键点击浏览栏中的EA32882_1p6,选择IBIS to DML;

(3)通过Allegro建立简单DML模型以及模型分配

如图7所示,单击