XDMA调试记录

1 XDMA硬件设计

1.1 XDMA IP核简介

Xilinx 提供的DMA Subsystem for PCI Express IP(简称XDMA)是一个高性能,可配置的、适用于PCIE2.0,PCIE3.0 的SG 模式 DMA,提供用户可选择的 AXI4 接口或者 AXI4-Stream接口。具体的可参考官方文档PG055,一般情况下配置成 AXI4 接口可以加入到系统总线互联,适用于大数据量异步传输,通常情况都会使用到 DDR,AXI4-Stream 接口适用于低延迟数据流传输。

XDMA 是SGDMA,并非Block DMA,SG 模式下,主机会把要传输的数据组成链表的形式,然后将链表首地址通过BAR 传送给XDMA,XDMA 会根据链表结构首地址依次完成链表所指定的传输业务。

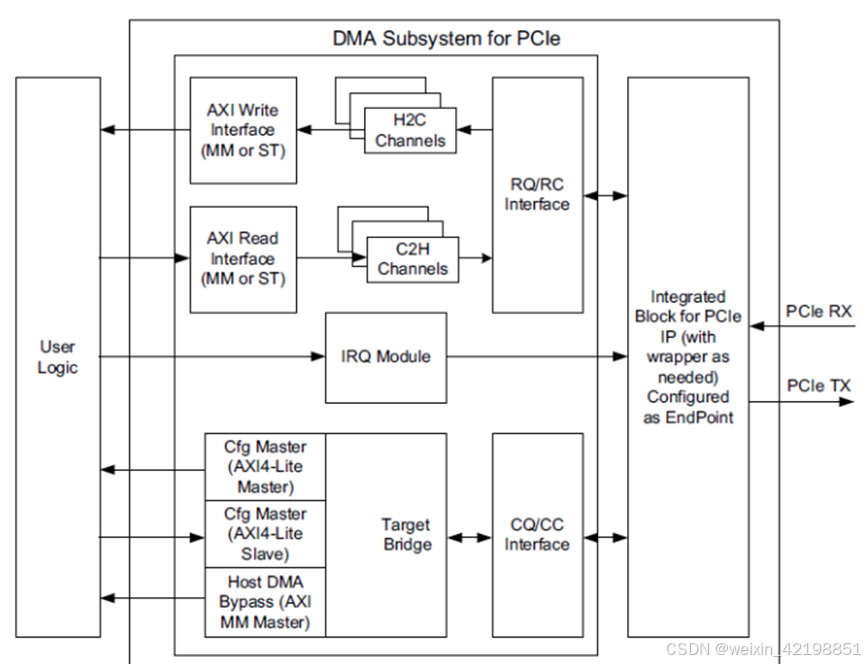

如上图所示,XDMA 提供如下接口:

- AXI4/AXI4-Stream:必须选择其中一个,用来数据传输。

- AXI4-Lite Master:可选,用来实现PCIE BAR 地址到 AXI4-Lite 寄存器地址的映射,可用来读写用户逻辑寄存器。

- AXI4-Lite Slave:可选,用来将XDMA 内部寄存器开放给用户逻辑,用户逻辑可以通过此接口访问 XDMA内部寄存器,不会映射到BAR。

- AXI4 Bypass接口:可选,用来实现PCIE 直通用户逻辑访问,可用于低延迟数据传输

1.2 XDMA硬件设计

1.2.1设计目的

将 PCIe NVMe SSD连接到ZYNQMP的PL端,同时,PS端能够直接访问NVMe盘。

1.2.2 开发环境 - Vivado 2018.3

- zcu106开发板

- FMC子卡

- NVMe SSD盘

1.2.3 XDMA设计概述

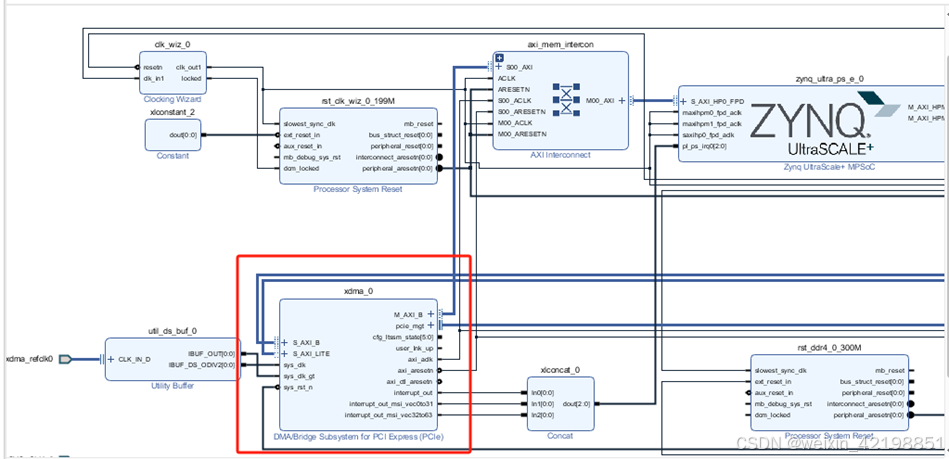

下图是整体的模块设计,接下来会详细描述XDMA的参数设置。

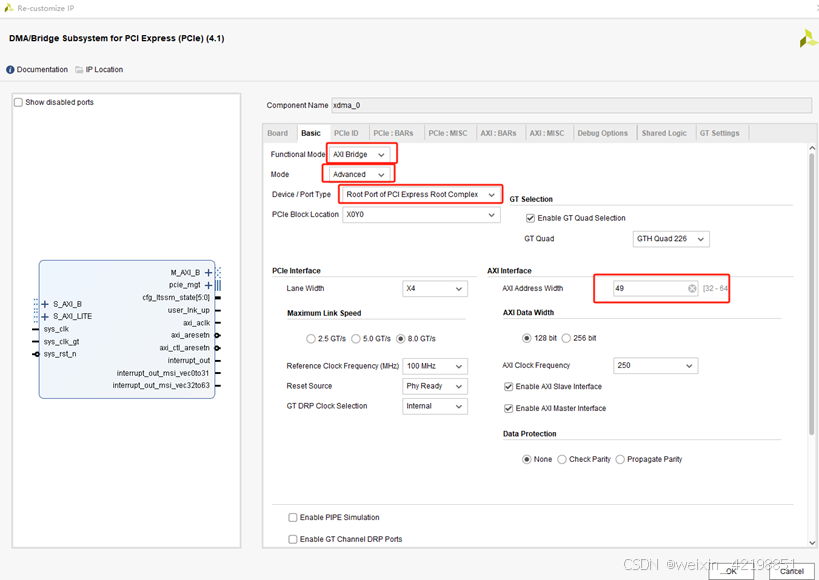

XDMA BASIC参数配置。Functional Mode选择 AXI Bridge,Mode选择Advanced,AXI Address Width选择49,其余参数保持默认即可,其余具体的参数设置如下图:

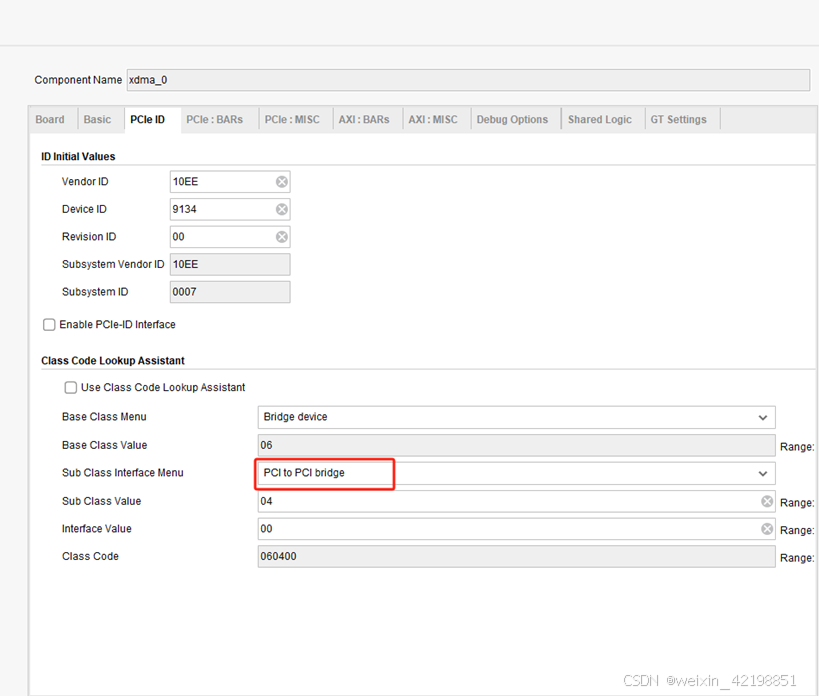

PCIe ID参数配置。Sub class Interface Menu配置为PCI to PCI bridge。

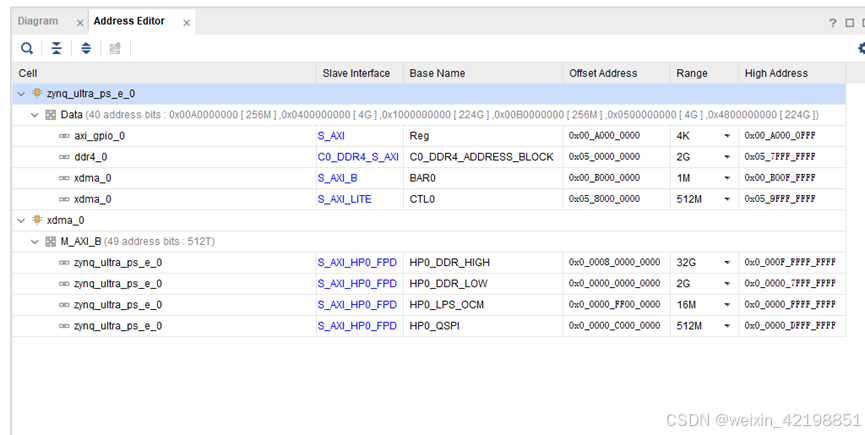

地址分配如下图

XDMA其他的参数配置无需更改,默认即可。

2 嵌入式设计

2.1 Linux内核配置

- 由于PCIE设备为NVME SSD盘,同时,SSD盘挂载到PL端,linux配置界面进行如下修改,如下图所示:

a) 选择如下

Bus support --->

PCI host controller drivers --->

[*] NWL PCIe Core

[*] Xilinx XDMA PL PCIe host bridge support

[*] Enable PCI resource re-allocation detection

Device Drivers --->

<*> NVM Express block device

- 保存配置文件并重新生成Image镜像文件,进入系统后复制到EMMC重启。

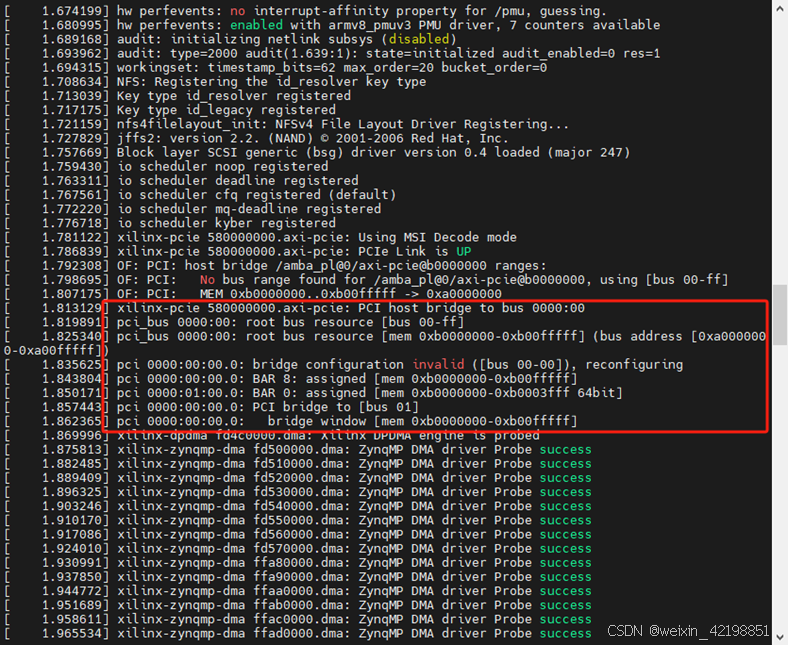

- 启动板卡,终端打印如下

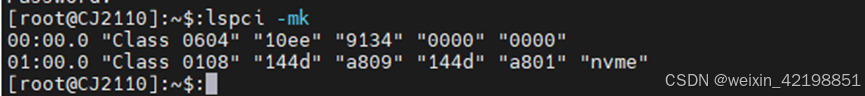

4、系统起来后,输入lspci -mk可查看PCIE接口信息

2.2 fio测试SSD速度

1、 在buildroot下编译fio工具:

a) menuconfig选择如下

Target packages --->

Debugging, profiling and benchmark --->

[*] fio

2、fio参数

fio的参数较多,具体的解释如下图所示,测试时,可将以下的参数搭配使用。如:

fio -filename=/dev/nvme0n1 -direct=1 -iodepth 4 -thread=1 -rw=read -ioengine=sync -bs=1M -size=20G -numjobs=1 -runtime=30 -group_reporting -name=my