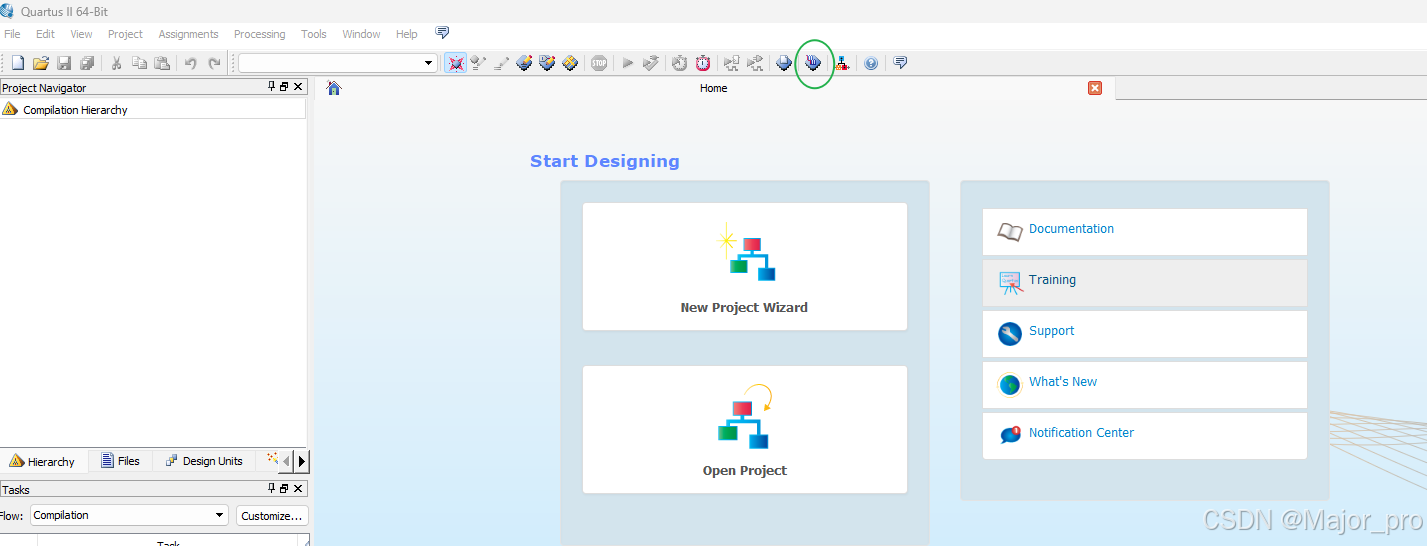

Quartus是Altera(现已被Intel收购)推出的一款针对其FPGA产品的综合性开发环境,用于设计、仿真和调试数字电路。以下是使用Quartus的一些总结和技巧(Tips),帮助更高效地进行FPGA项目开发:

使用总结

-

工程创建与管理:在开始新项目时,正确设置工程选项非常重要,包括选择正确的器件型号和配置文件路径。确保你的设计符合目标芯片的资源限制。

-

设计输入:支持多种设计输入方式,包括原理图输入、VHDL、Verilog HDL等。对于大型复杂的设计,推荐使用硬件描述语言(HDL)进行设计输入。

-

综合(Synthesis):这是将你的HDL代码转换为门级网表的过程。选择合适的综合选项可以优化性能、降低功耗或节省面积。

-

布局布线(Fitlering & Place & Route):这个过程决定了逻辑单元如何映射到具体的物理位置以及它们之间的连接方式。良好的布局布线可以显著影响最终设计的性能。

-

时序分析(Timing Analysis):通过检查设计是否满足时间约束来保证信号能够及时到达目的地。合理设置时序约束对获得高性能的设计至关重要。

-

仿真(Simulation):在下载到实际硬件之前,使用仿真工具验证设计的功能正确性。这可以帮助提前发现并修复潜在问题。

TIPS

-

增量编译(Incremental Compilation):利用增量编译可以减少后续修改后的编译时间,特别是对于大型项目来说效果尤为明显。

-

状态机编码(State Machine Coding):采用明确的状态编码方式可以简化状态机的设计,并有助于提高综合效率。

-

IP核的使用:充分利用Quartus提供的IP核库,可以快速实现一些常见的功能模块,如FIFO、RAM等,节省开发时间。

-

约束文件(UCF/SDF):正确编写约束文件以指导综合和布局布线工具按照设计者的意图工作。注意时序约束的重要性。

-

版本控制:对于复杂的FPGA设计项目,建议使用版本控制系统(如Git)来管理和追踪设计变更。

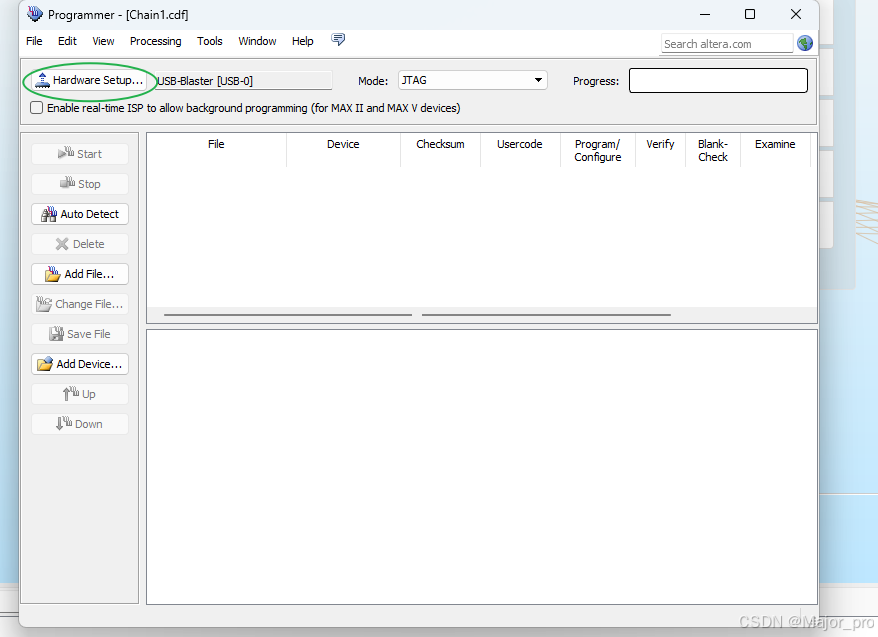

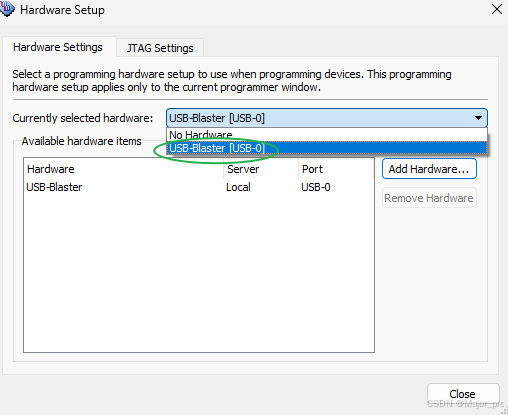

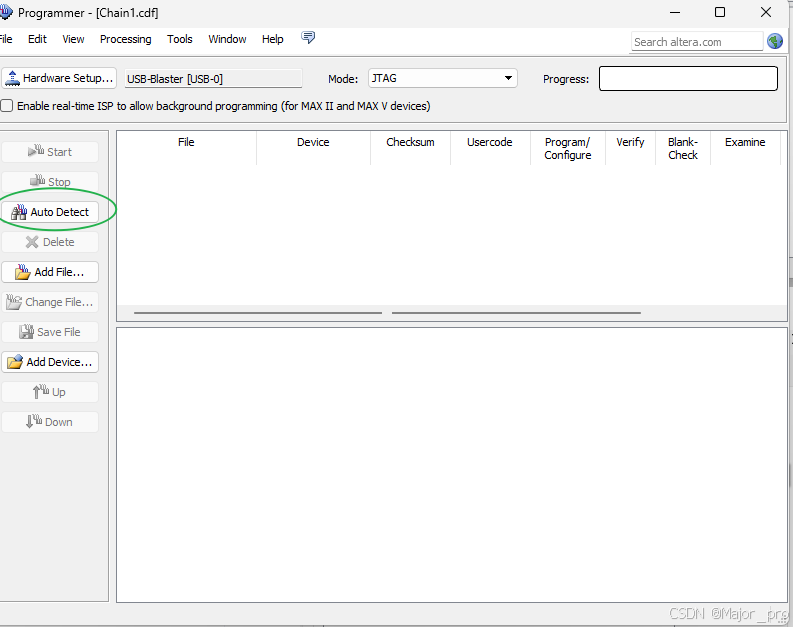

烧录说明