注意

- 芯片型号:TMS320F28335

- 参考资料:《TMS320F28335 DSP原理、开发及应用》

- 对应PPT第二章

- 本章内容较多而且较为重要,请结合PPT一起复习

- 为了考试复习的同学请谨慎参考,本笔记的大部分都没考到

1 F28335内核

- 对用PPT15页

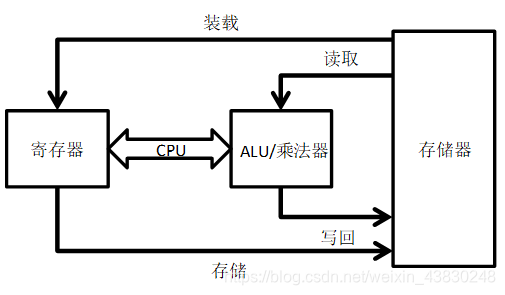

1.1 CPU

- 分为32位定点CPU和32位浮点CPU

- 使用原子指令,汇编编程更简便、尺寸更小、速度更快、不可被中断的指令、更高效的编译

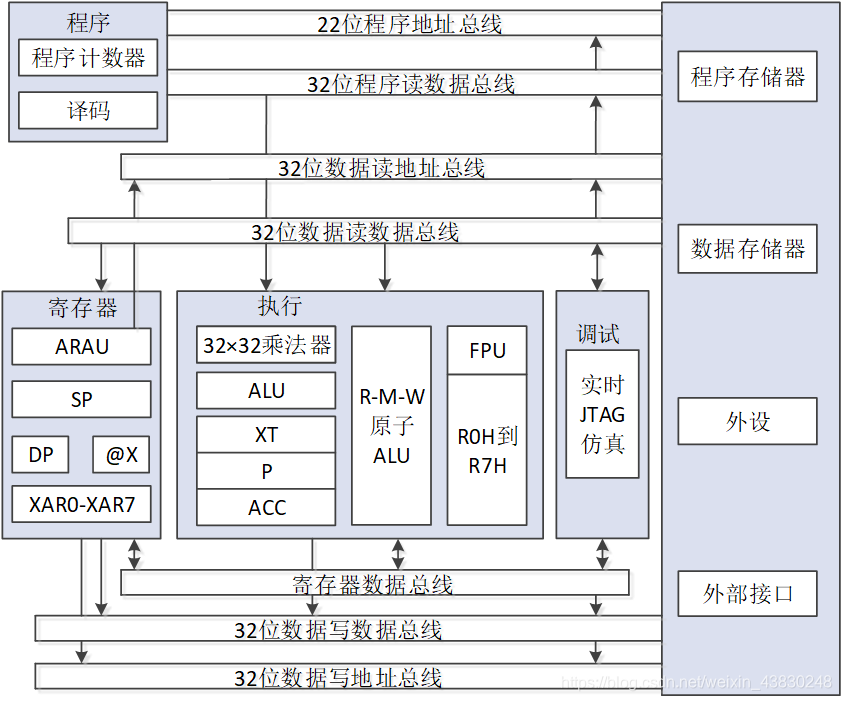

1.2 总线结构

- 程序读总线:

22位地址,32位数据; - 数据读总线:

32位地址,32位数据; - 数据写总线:

32位地址,32位数据;

- 采用哈佛总线结构

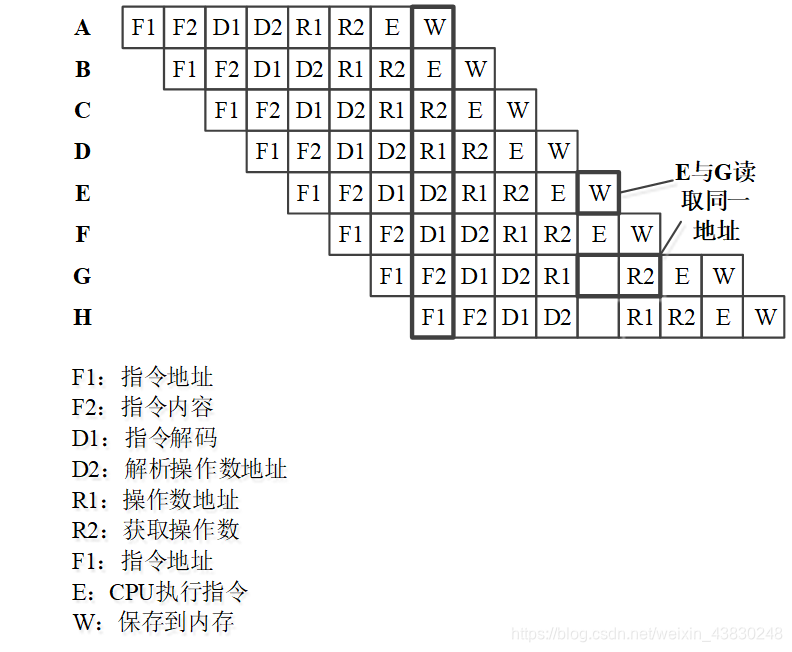

1.3 流水线机制

- 这一机制在上一章有讲到

- 流水技术是将各指令的各个步骤重叠起来执行,即使得若干条指令的不同执行阶段可以处于同一时刻并行处理,这样每一个阶段称作一个流水。

1.4 FPU流水线

- 暂不清楚这是个什么东西

2 F28335的存储单元

2.1 F28335存储介质:

1)Flash存储器;

2)单周期访问RAM;

3)OTP;

4)片外存储器;

5)Boot ROM。

2.2 代码保护模块CSM

- 防止逆向工程,并保护知识产权(IP)

- Flash中的一段长度为128bit的存储空间

- 2128 = 3.4 x 1038 种可能的密码

- 在150MHz的时钟频率下,每8个时钟周期试验一组密码,则最多需要5.8 x 1023年

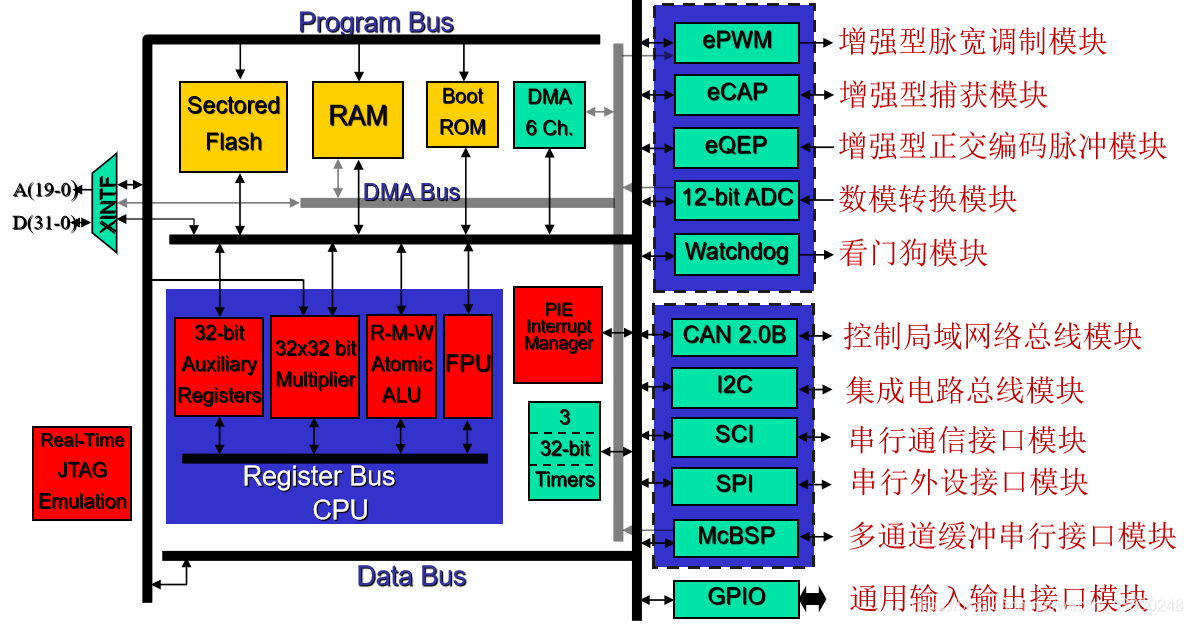

3 片上外设

- 增强型脉宽调制模块

- 增强型捕获模块

- 增强型正交编码脉冲模块

- 数模转换模块

- 看门狗模块

- 控制局域网络总线模块

- 集成电路总线模块

- 串行通信接口模块

- 串行外设接口模块

- 多通道缓冲串行接口模块

- 通用输入输出接口模块

- 这里仅仅是将片内外设列举一遍,后边的笔记里会有具体的讲解。

4 F28335特点

- PPT:24

4.1 高性能静态 CMOS 技术

- 主频最高达 150MHz

- 1.9V/1.8V内核,3.3V I/O设计

4.2 高性能 32 位 CPU

- IEEE-754 单精度浮点单元

- 16 x 16 和 32 x 32 介质访问控制 (MAC) 运算

- 16 x 16 双 MAC

- 哈佛 (Harvard) 总线架构

- 快速中断响应和处理

- 统一存储器编程模型和高效代码

4.3 6 通道 DMA 处理器

4.4 16 位或 32 位外部接口XINTF

4.5 片内存储器

- 256K Flash,34K×16 SARAM

- 1K×16 OTP ROM

4.6 引导ROM

- 8K×16

- 支持软件引导模式(通过 SCI,SPI,CAN,I2C,McBSP,XINTF 和并行 I/O)

4.7 时钟和系统控制

- 支持动态锁相环 (PLL) 比率变化,片载振荡器,安全装置定时器模块

4.8 GPIO

- GPIO0 到 GPIO63 引脚可以连接到八个外部内核中断其中的一个

4.9 PIE

- 可支持全部58个外设中断的外设中断扩展 (PIE) 块

4.10 128 位安全密钥/锁

- 保护闪存 / OTP/RAM 模块,防止固件逆向工程

- 上文提到过

4.11 增强型控制外设

- ePWM,eCAP,eQEP

4.12 3个32位定时器

4.13 串行端口外设

- CAN,SCI,McBSP,SPI,I2C

4.14 12位模数转换器

- 80ns转换速度,2×8通道输入复用

- 两个采样保持,单一/同步转换

- 内部或外部电压基准

4.15 低功耗模式和省电模式

- 支持IDLE(空闲)、STANDBY(待机)、HALT(暂停)模式

- 可禁用独立外设时钟