定义

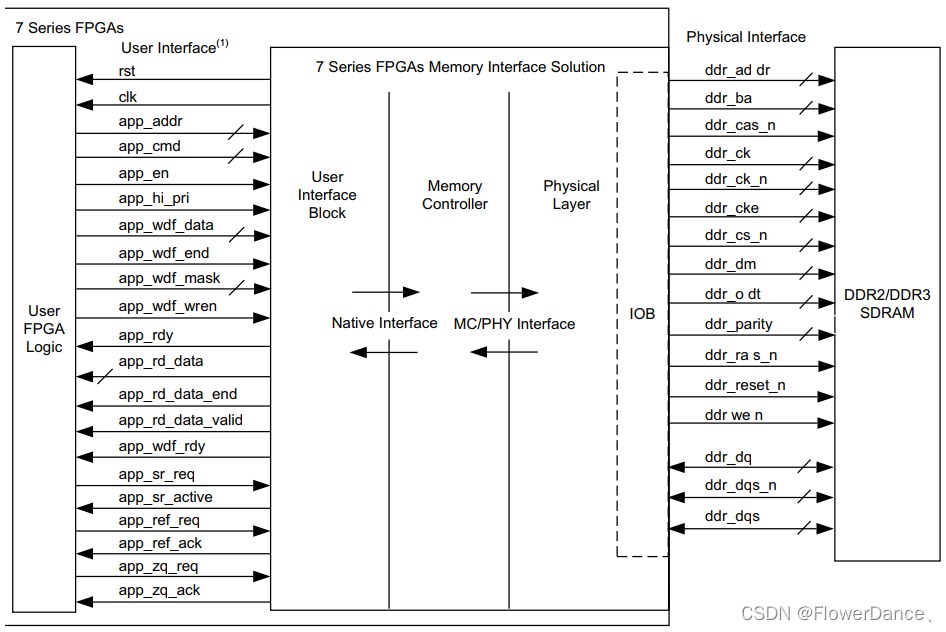

MIG IP 核是 Xilinx 公司针对 DDR 存储器开发的 IP,里面集成存储器控制模块,实现 DDR 读写操作的控制流程,下图是 7 系列的 MIG IP 核结构框图。 MIG IP 核对外分出了两组接口。左侧是用户接口,就是用户( FPGA)同 MIG 交互的接口,用户只有充分掌握了这些接口才能操作 MIG。右侧为 DDR 物理芯片接口,负责产生具体的操作时序,并直接操作芯片管脚。这一侧用户只负责分配正确的管脚,其他不用关心。表中标明的信号的方向是以 MIG IP 核作为参照的。

用户接口

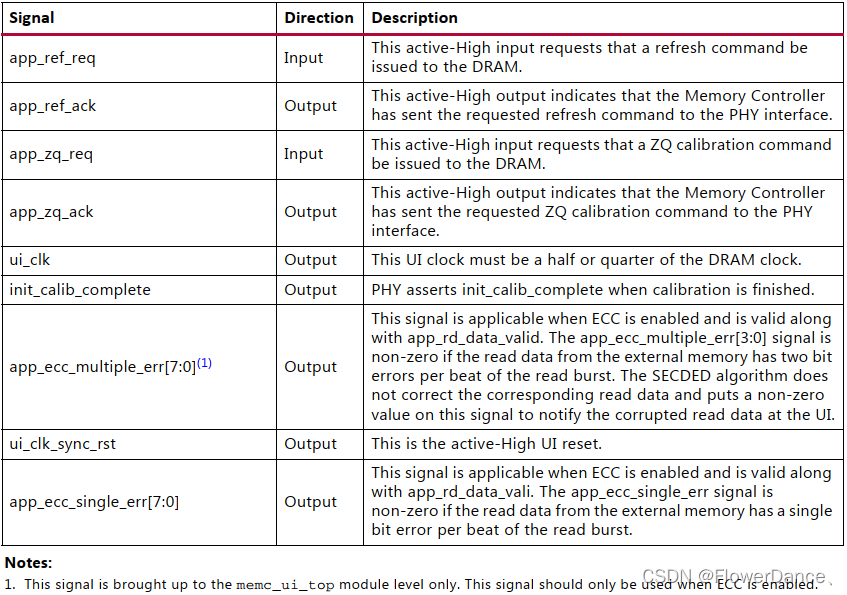

| 信号名 | 方向 | 端口说明 |

|---|---|---|

| ui_clk | output | 用户时钟,由MIG IP核输出,必须是DRAM时钟的四分之一 |

| ui_clk_sync_rst | output | 复位,由MIG IP核提供,高电平有效 |

| app_addr[ADDR_WIDTH–1:0] | input | 用户地址输入,这是MIG IP核根据具体的物理芯片,整合给用户使用的地址空间,这个地址和芯片的地址是对应的,地址的位宽ADDR_WIDTH等于BANK位宽+ ROW位宽 + COL位宽 |

| app_cmd[2:0] | input | 读写控制命令。读: 001;写: 000。其他值保留 |

| app_en | input | MIG IP核命令写入使能,高有效。写命令时需要拉高该信号 |

| app_rdy | output | 表示UI已经准备好接收命令,高电平有效。如果当app_en使能时,该信号未拉高,那么当前的app_amd和app_addr信号必须保持直到app_rdy拉高 |

| app_hi_pri | input | 表明当前请求具有高优先级 |

| app_rd_data[APP_DATA_WIDTH–1:0] | output | 该信号用于用户读取IP核发来的数据,位宽同样设置为128。 |

| app_rd_data_end | output | 高电平有效,表明当前时钟周期是app_rd_data输出数据的最后一个周期。只有当app_rd_data拉高时该信号才有效 |

| app_rd_data_valid | output | 读数据有效信号,高电平有效。 |

| app_wdf_data[APP_DATA_WIDTH-1:0] | input | 该信号为用户写数据输入 |

| app_wdf_end | input | 当前时钟是突发写过程的最后一个时钟,高电平有效。 |

| app_wdf_mask[APP_MASK_WIDTH-1:0] | input | 为app_wdf_data提供掩码 |

| app_wdf_rdy | output | MIG IP核数据接收准备完成,高电平有效。写数据只有当app_wdf_rdy和app_wdf_wren同时拉高时才会被接收 |

| app_wdf_wren | input | MIG IP核数据写使能,高电平有效。写数据时需要拉高该信号。 |

| init_calib_complete | output | 高电平有效,表明校准完成 |

| app_sz | input | 此输入是保留的,应绑定到0。 |

| app_correct_en_i | input | 当拉高时,该有效的高信号校正单比特数据错误。只有当在GUI中启用ECC时,此输入才有效。在示例设计中,该信号总是与1绑定。 |

| app_sr_req | input | 该信号被保留并且应绑定到0 |