本文主要介绍AXI-FULL的相关基础内容,AXI-Lite请移步:

【FPGA开发】AXI-Lite总线协议解读、Verilog逻辑开发与仿真、Alex Forencich代码解读

相比于Lite接口,Full接口的变化,一个体现在端口数量变多,增加了很多定义和概念,另一个方面,也是个人理解最主要的变化是:突发。Full多了突发传输特性之后,又会引出很多其他概念,这是Lite无法比拟的,因此,丝滑的从Lite学习到Full是难以做到的,一个协议那么多内容,千人千面,量力而行,慢慢学即可,不必大包大揽的一次性全读懂。

协议解读

接口介绍

AW—写地址通道

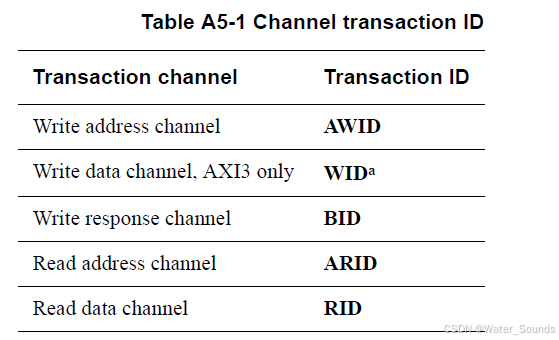

AWID:写地址ID,这个信号是写地址组的标识标签。实际上,每个传输通道都有一个自己的ID。

AWADDR:写地址,该地址给出了写突发事务中第一次传输的地址。

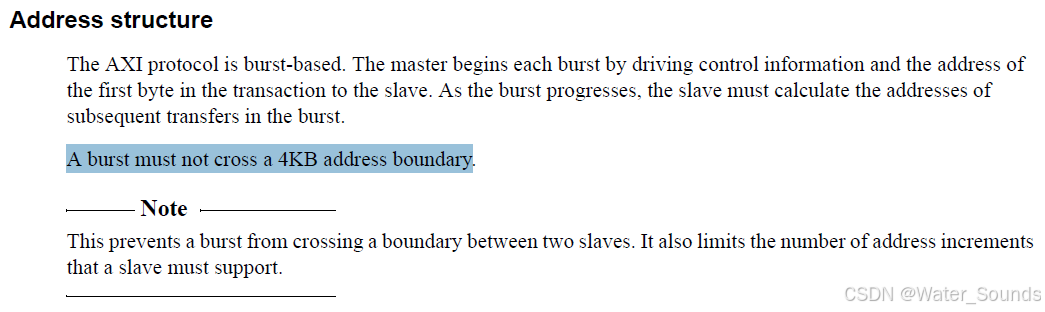

AXI协议是基于突发的,主机驱动控制信息和事务中第一个字节的地址传输到从机,从而开始突发。

随着突发的进行,从机必须计算突发中后续传输的地址。

突发不能跨越4KB的地址边界。

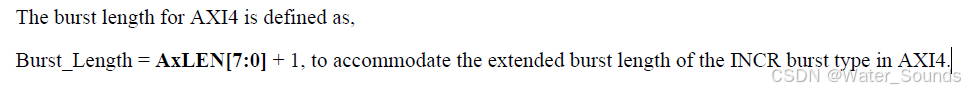

AWLEN:突发长度,给出了突发中传输的确切数量。

AXI4对INCR突发模式支持1-256次传输,对所有其他突发模式支持1-16次传输,这里所说的突发模式,在下面展开。

AxLEN与突发长度之间的计算公式,如下图所示:

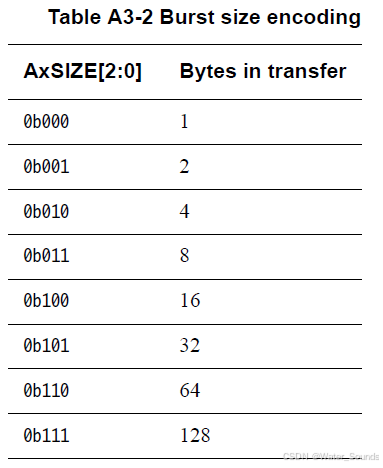

AWSIZE:表示每次突发中传输的大小。

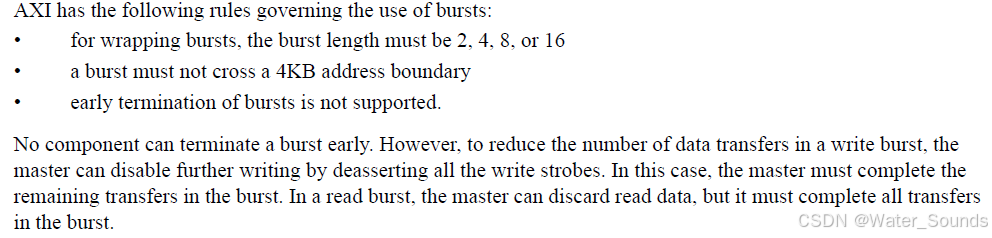

AWBURST:突发类型,突发类型和大小信息决定了如何计算突发内每个传输的地址。

FIXED模式:每次突发传输的地址都相同。

INCR模式:每次突发的地址,会根据突发大小递增。

WRAP模式:和INCR类似,不同之处在于,如果达到了地址上限,地址就会换行回低地址。

AWLOCK:锁类型,提供有关传输的原子特性的其他信息。

AXI4不支持锁定事务。

AWCACHE:内存类型,该信号指示事务如何在系统中进行。

AWPORT:保护类型,该信号指示事务的特权和安全级别,以及该事务是数据访问还是指令访

问。

AWQOS:Quality of Service,服务质量,为每个写事务发送的QoS标识符。

AWREGION:区域标识符,允许从服务器上的单个物理接口用于多个逻辑接口。

AWUSER:用户信号,可选写地址通道中的用户自定义信号。

AWVALID:写地址有效,该信号表明通道正在发送有效的写地址和控制信息。

AWREADY:写地址准备信号,这个信号表明从机已经准备好接收一个地址和控制信号了。

W—写数据通道

WID:写ID标签

WDATA:写数据

WSTRB:该信号指示哪些字节通道保存有效数据。写数据总线的每8位对应一位WSTRB

WLAST:在一次写事务中,标志着最后一个传输。

WUSER:用户信号,可选写数据通道中的用户自定义信号。

WVALID:写有效信号。这个信号表明有效的写数据和strb可用。

WREADY:写准备信号,表示从机可以接收写数据了。

B—写响应通道

BID:写响应ID标签。

BRESP:写响应。

BUSER:用户信号。

BVALID:写响应有效信号。

BREADY:写响应准备信号。

AR—读地址通道

同写地址通道类似。

R—读数据通道

RID:读ID标签。

RDATA:读数据

RRESP:读响应

RLAST:对齐最后一个数据的last信号

RUSER:用户信号。

RVALID:读有效信号。

RREADY:读准备信号。

以上关于接口的相关内容,可在《IHI0022E_amba_axi》的手册中查阅到

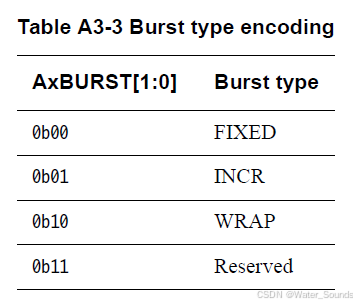

FPGA搭建仿真平台

如下图所示,两个模块均为Vivado自己生成封装的IP核,这里快速搭建仿真平台以观察波形。

(Block Design搭建过程详见Lite的文章)

给入时钟、复位和tx触发信号后,就能跑起来AXI-Full的波形

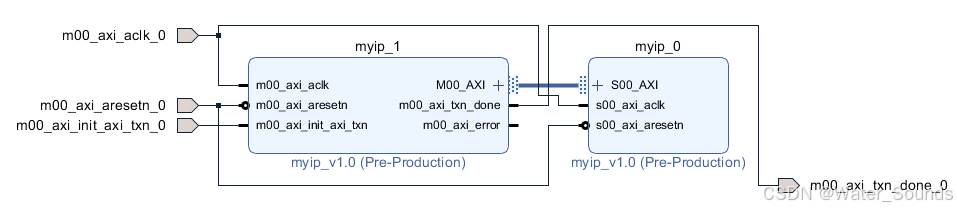

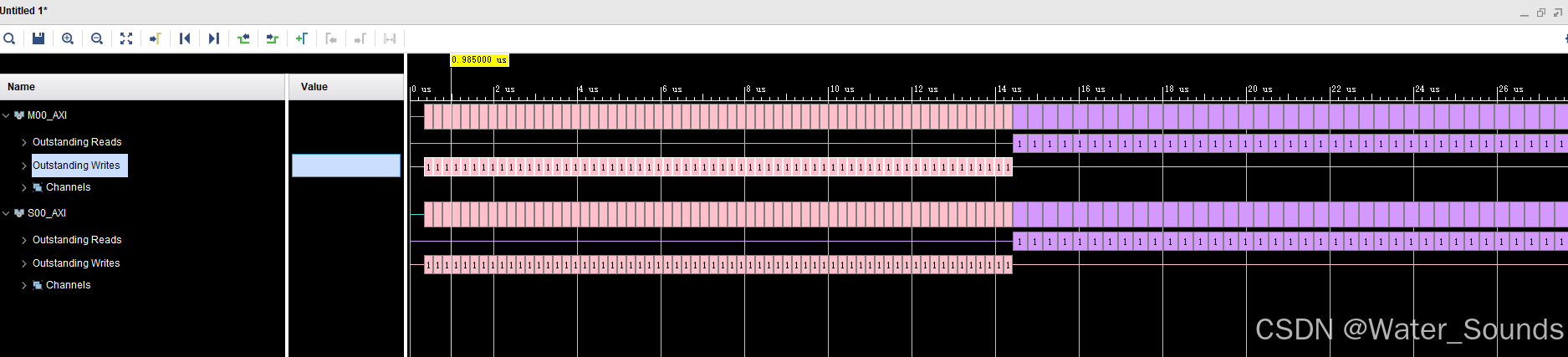

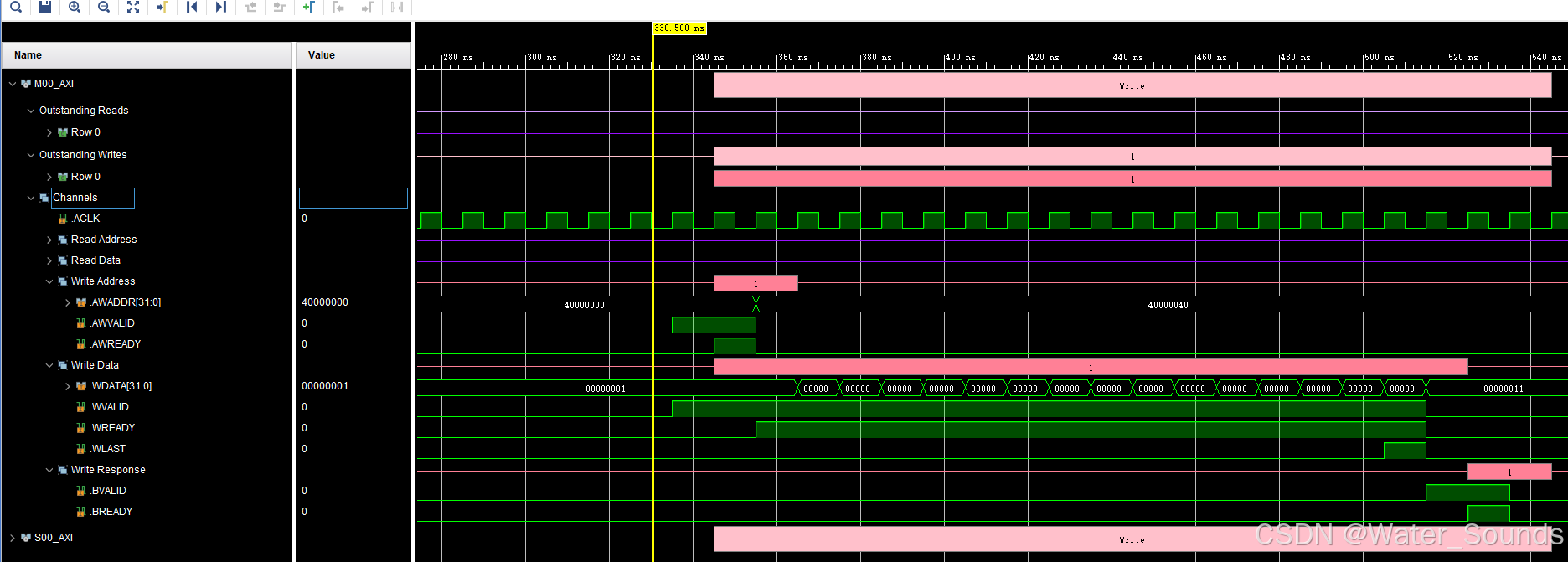

看一次突发写的波形:

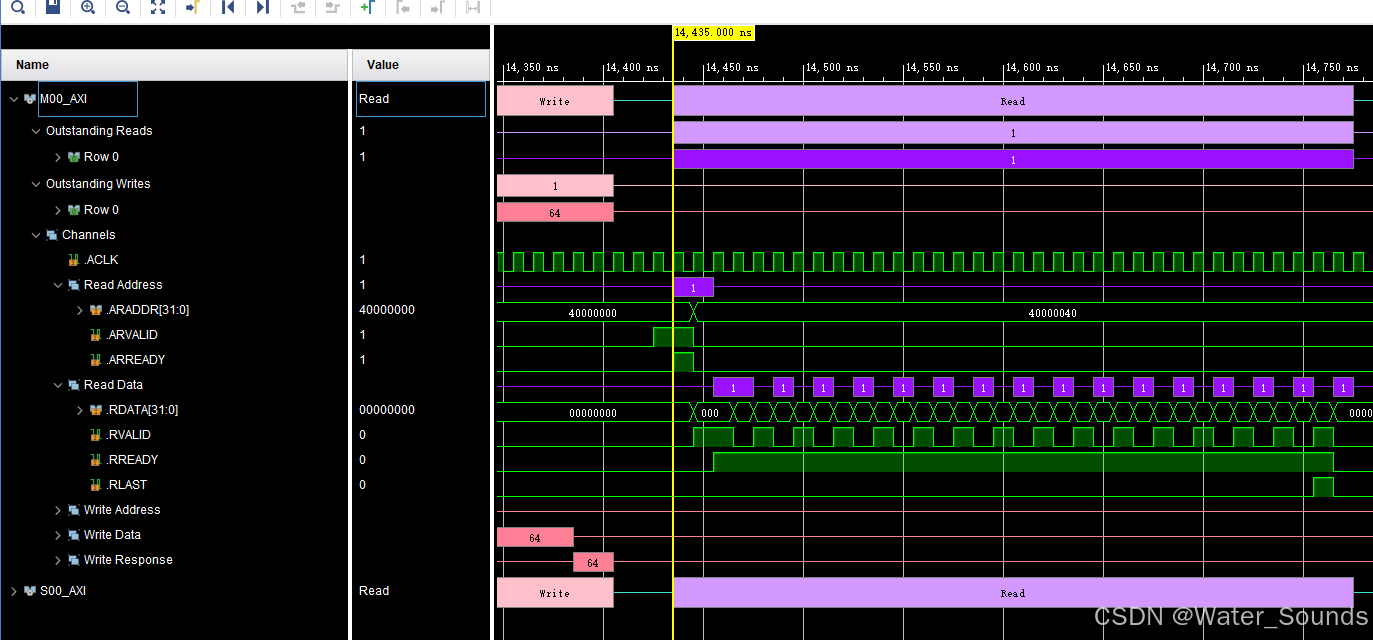

看一次突发读的波形: