摘要

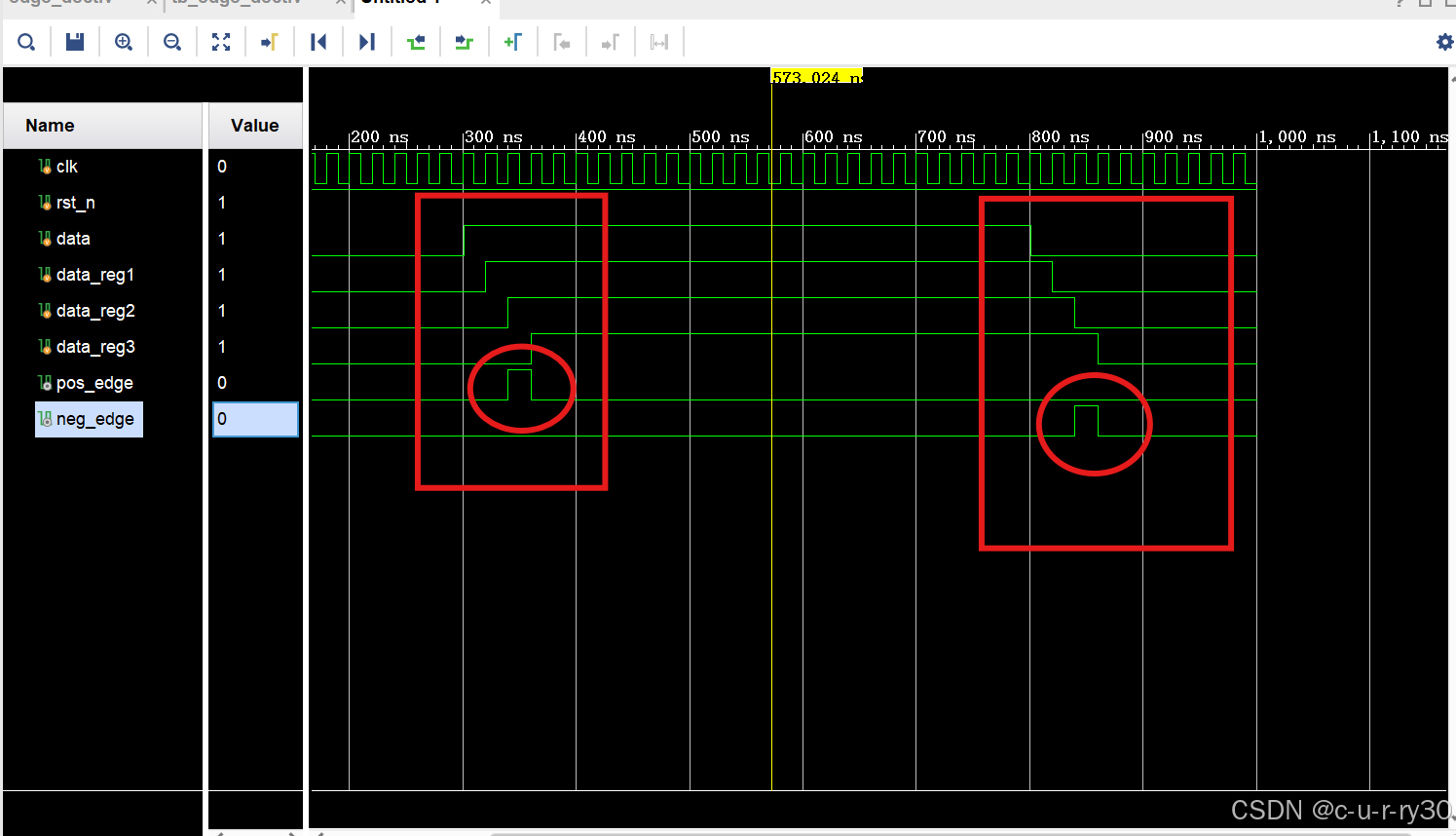

文章为学习记录。采用时序逻辑和组合逻辑实现边沿检测的核心逻辑。组合逻辑实现的上升沿和下降沿的脉冲比时序逻辑实现的上升沿和下降沿的脉冲提前一拍。

一、边沿检测

边沿检测主要作用是能够准确的识别出单比特信号的上升沿或下降沿。

边沿检测原理:利用寄存器对信号前一状态和后一状态进行寄存,若前后两个状态不同,则检测到了边沿。

二、时序逻辑实现

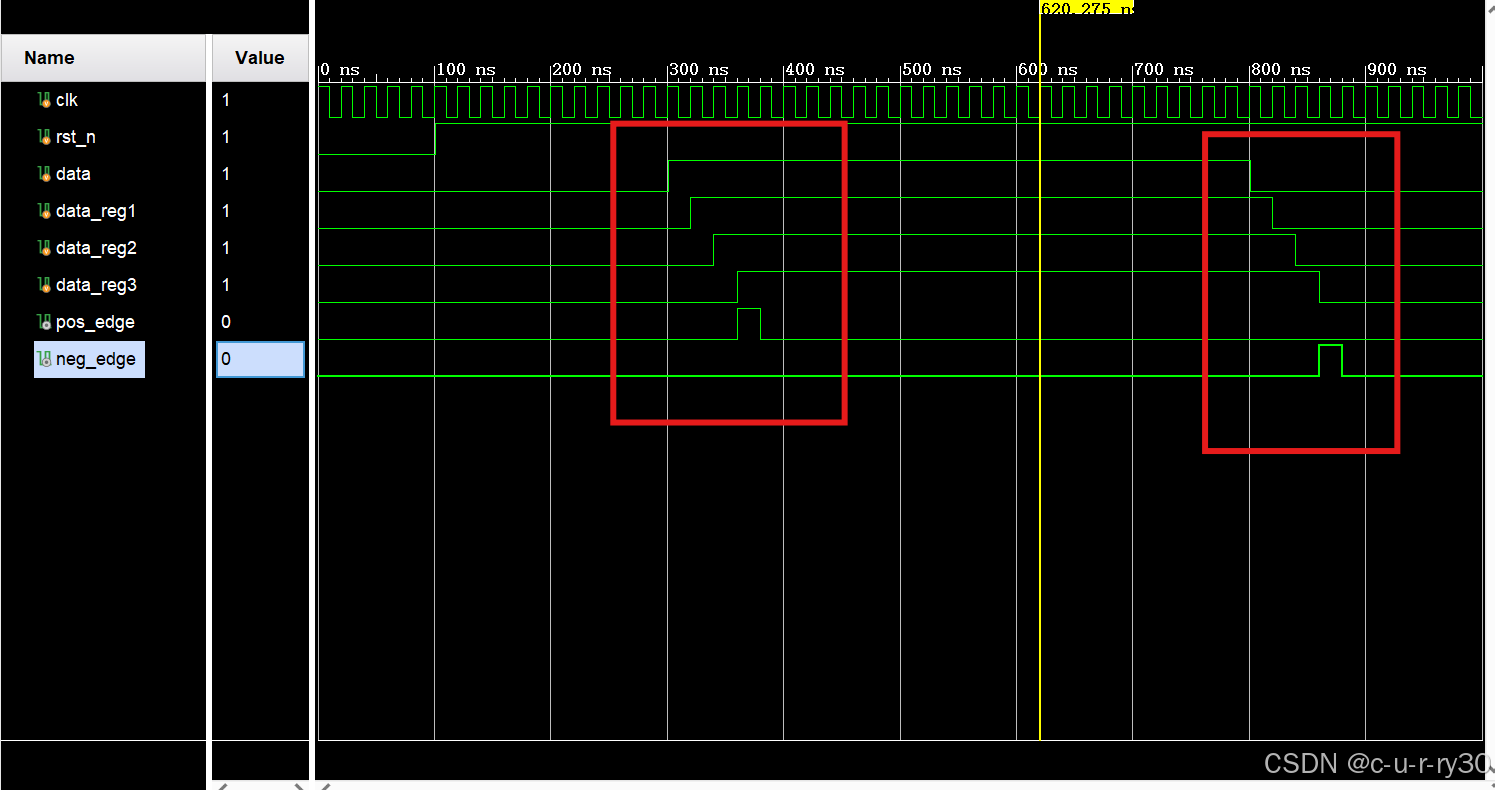

仿真波形如下图所示。

2.1 rtl

module edge_dect(

input wire clk,

input wire rst_n,

input wire data,

output reg pos_edge,

output reg neg_edge

);

reg data_reg1;

reg data_reg2;

reg data_reg3;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

data_reg1 <= 0;

data_reg2 <= 0;

data_reg3 <= 0;

end

else

begin

data_reg1 <= data;

data_reg2 <= data_reg1;

data_reg3 <= data_reg2;

end

end

always @(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

pos_edge <= 1'b0;

else if(data_reg2 && (~data_reg3))

pos_edge <= 1'b1;

else

pos_edge <= 1'b0;

end

always @(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

neg_edge <= 1'b0;

else if((~data_reg2) && data_reg3)

neg_edge <= 1'b1;

else

neg_edge <= 1'b0;

end

endmodule

2.2 tb

module tb_edge_dect();

reg clk;

reg rst_n;

reg data;

wire pos_edge;

wire neg_edge;

initial

begin

rst_n = 0;

data = 0;

#101;

rst_n = 1;

#200;

data = 1;

#500;

data = 0;

#200;

$stop;

end

initial

begin

clk = 1;

end

always #10 clk = ~clk;

edge_dect edge_dect_inst1

(

. clk(clk),

. rst_n(rst_n),

. data(data),

. pos_edge(pos_edge),

. neg_edge(neg_edge)

);

endmodule

三、组合逻辑实现

仿真波形如下图所示。

3.1 rtl

module edge_dect(

input wire clk,

input wire rst_n,

input wire data,

output wire pos_edge,

output wire neg_edge

);

reg data_reg1;

reg data_reg2;

reg data_reg3;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

data_reg1 <= 0;

data_reg2 <= 0;

data_reg3 <= 0;

end

else

begin

data_reg1 <= data;

data_reg2 <= data_reg1;

data_reg3 <= data_reg2;

end

end

assign pos_edge = data_reg2 && (~data_reg3);

assign neg_edge = ~data_reg2 && data_reg3;

//always @(posedge clk or negedge rst_n)

//begin

// if(rst_n == 1'b0)

// pos_edge <= 1'b0;

// else if(data_reg2 && (~data_reg3))

// pos_edge <= 1'b1;

// else

// pos_edge <= 1'b0;

//end

//always @(posedge clk or negedge rst_n)

//begin

// if(rst_n == 1'b0)

// neg_edge <= 1'b0;

// else if((~data_reg2) && data_reg3)

// neg_edge <= 1'b1;

// else

// neg_edge <= 1'b0;

//end

endmodule

3.2 tb

tb文件与时序逻辑实现的tb文件一样。