实验目的

学习用触发器构成移位寄存器的原理,了解累加器工作原理。

实验原理

数据的存储和移动是对数字信号的一种常见操作,能实现这种操作的器件有数据寄存器和移位寄存器,它们同计数器一样是数字电路中不可缺少的时序逻辑器件。

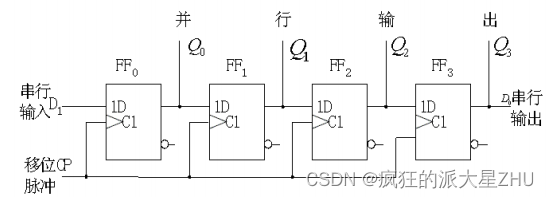

触发器具有存储信息的功能,利用这一特点,将四D

触发器

7417链型连接,构成一个四位的串行移位寄存器。一个时钟脉冲可以将数据向右或者向左移动一位,经过四个时钟脉冲,就可以将一个四位二进制数存储在74175构成的寄存器中,

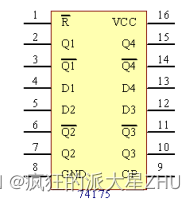

74175

管脚图如图

1

所示,构成的移位寄存器逻辑图如图2

所示。

图

1

四

D

触发器

74175管脚图 图

2 74175

构成四位移位寄存器

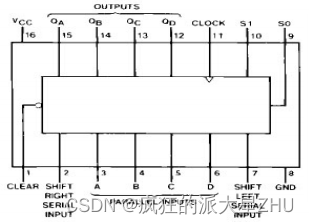

74194

是一个双向移位寄存器,并且可以并行输入,其管脚图如图3所示。其中

A~D

为并行输入端,

QA~QD

为并行输出端,

CLOCK

为时钟输入端,CLEAR

为异步清零端,

SHIFT RIGHT SERIAL INPUT

为串行右移输入端,SHIFT LEFT SERIAL INPUT

为串行左移输入端,S0、

S1

为工作模式控制端,通过设置

S0

和

S1

,可以使其工作在保持(S0=0

,

S1=0

)、串行左移(

S0=0

,

S1=1

)、串行右移(

S0=1

,S1=0)或并行(

S0=1

,

S1=1

)输入输出状态。

图

3 74194

管脚图

图

3 74194

管脚图

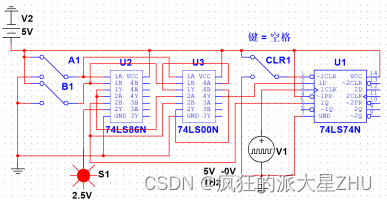

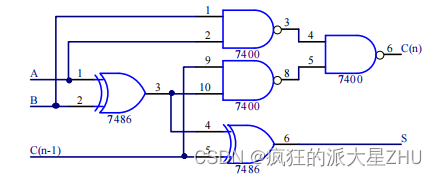

串行累加电路结构简单,运算由低位开始,两个最低位相加产生和与进位,当次低位相加时要考虑最低位的进位,所以用D

触发器7474来存放进位,全加器电路如图

5

所示。

利用

74175

构成的移位寄存器和

74194

作两个四位的移位寄存器,经过全加器将两个寄存器连接起来构成一个系统,数据先进入低四位寄存器,然后经全加器和高四位(为0

)相加后进入高四位,这时候低四位存储了新的四位二进制数,再经过四个时钟脉冲后,和高四位的四位二进制数相加,并将结果存储在高四位寄存器中。

图5

全加器逻辑图

图5

全加器逻辑图

实验内容

1

、将四

D

触发器

74175

连接成串行移位寄存器,并调试其正常工作。

2

、熟悉双向移位寄存器

74194

的功能,并调试使其正常工作。

3

、搭建全加器电路,并将进位寄存器

7474

添加进来,调试电路使其可以正常工作。

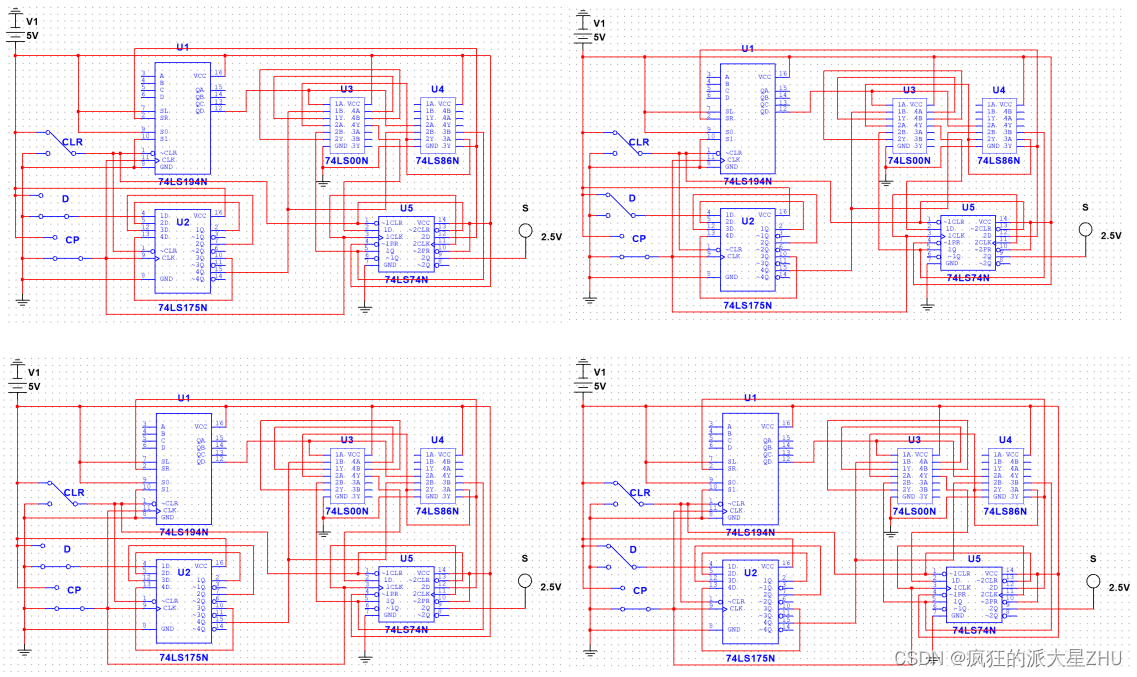

4

、将移位寄存器和全加器连接起来构成一个移位寄存和串行累加系统,调试电路使其可以正常工作。

5

、完成

1010+0011=1101

的加法运算。

仿真分析

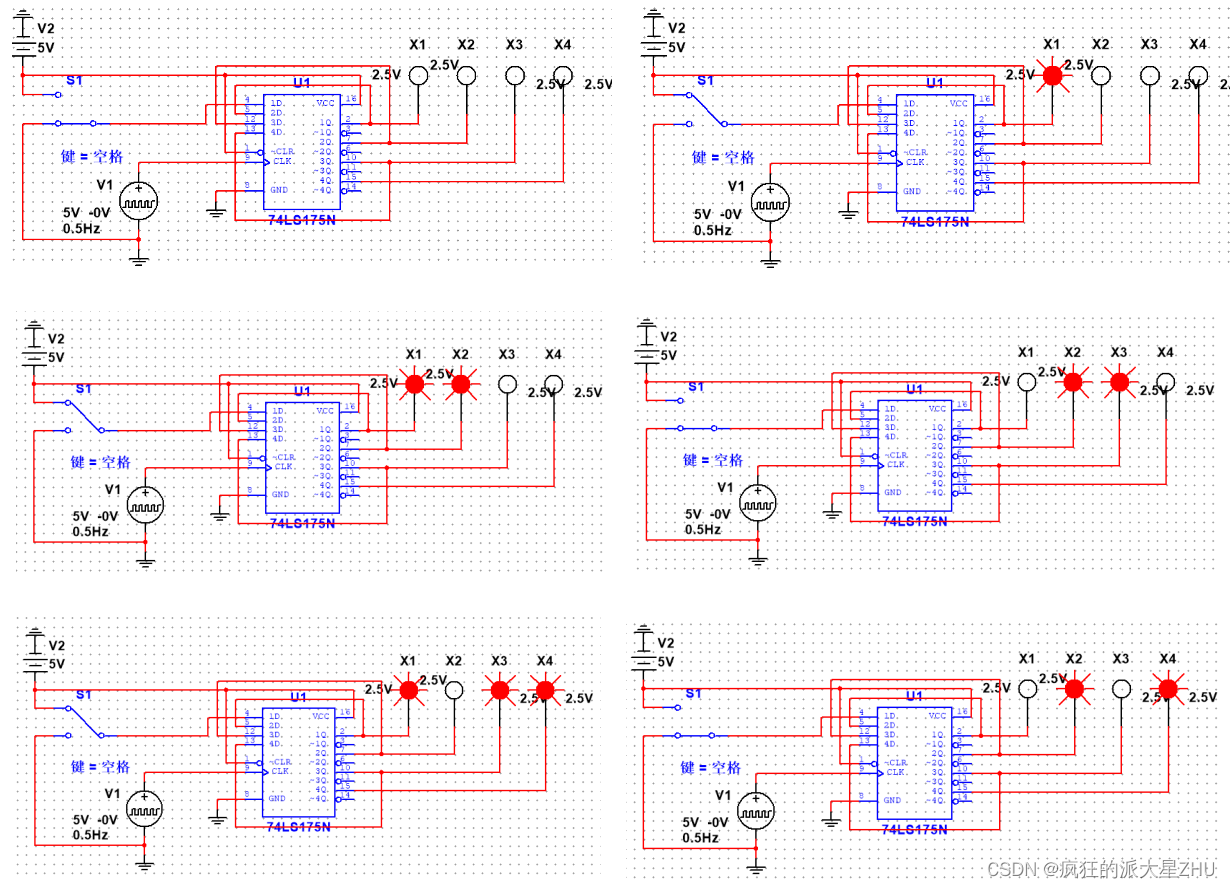

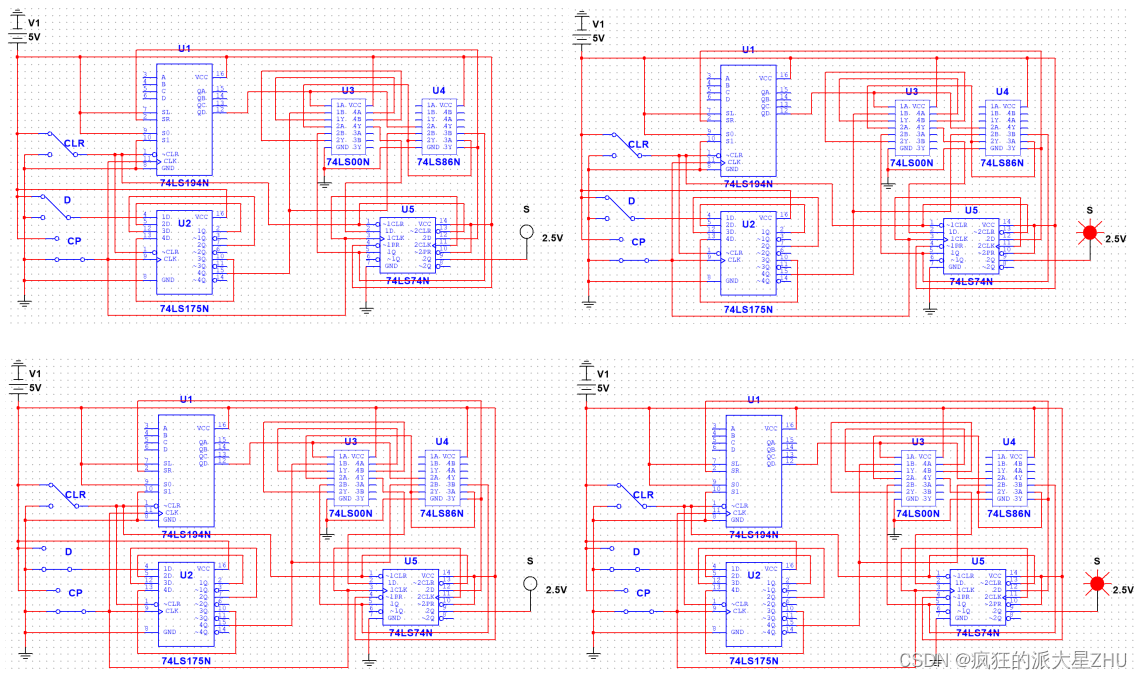

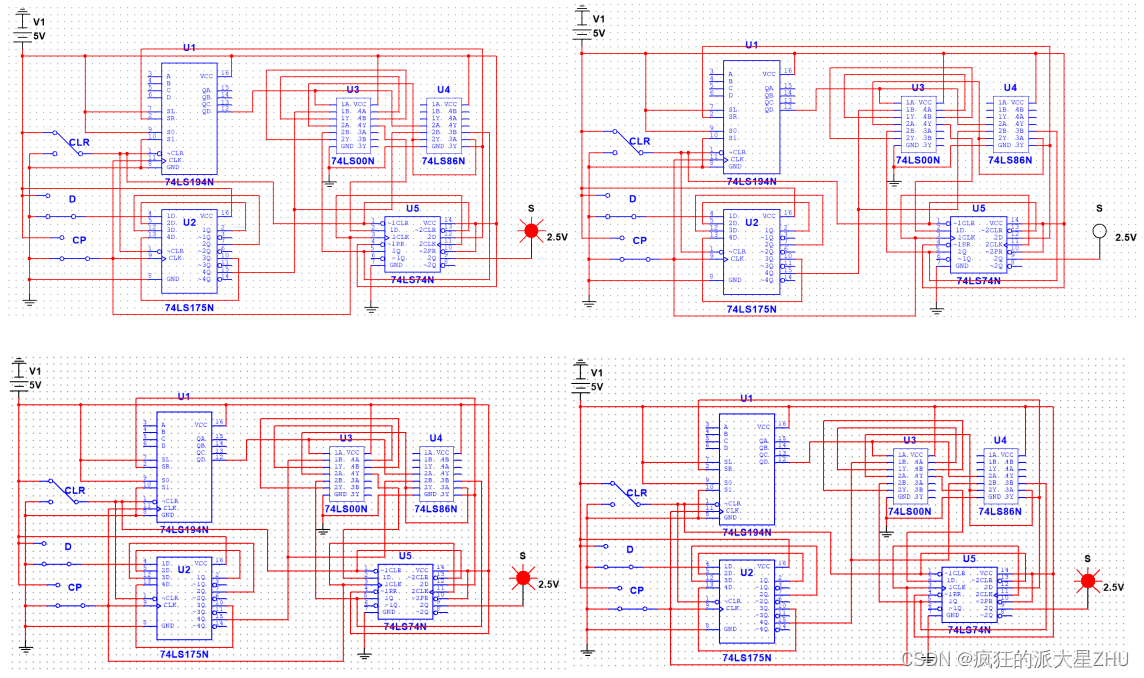

1、将四D触发器74175连接成串行移位寄存器,并调试其正常工作。

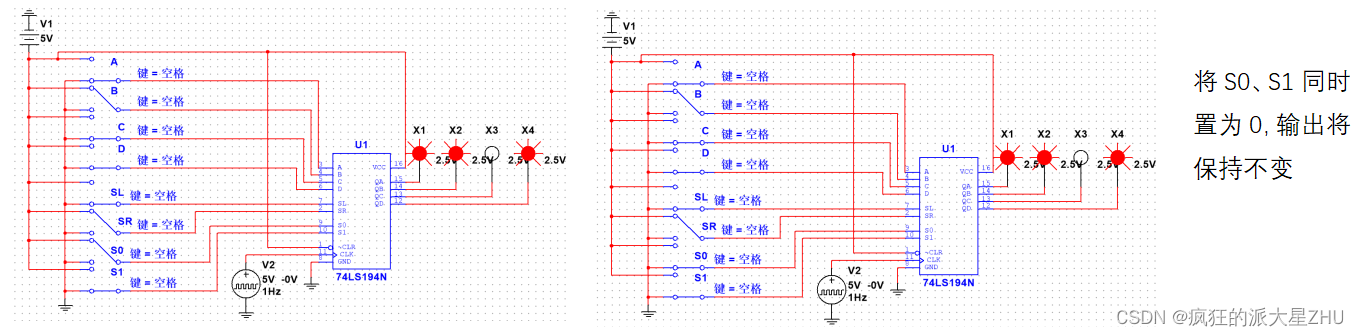

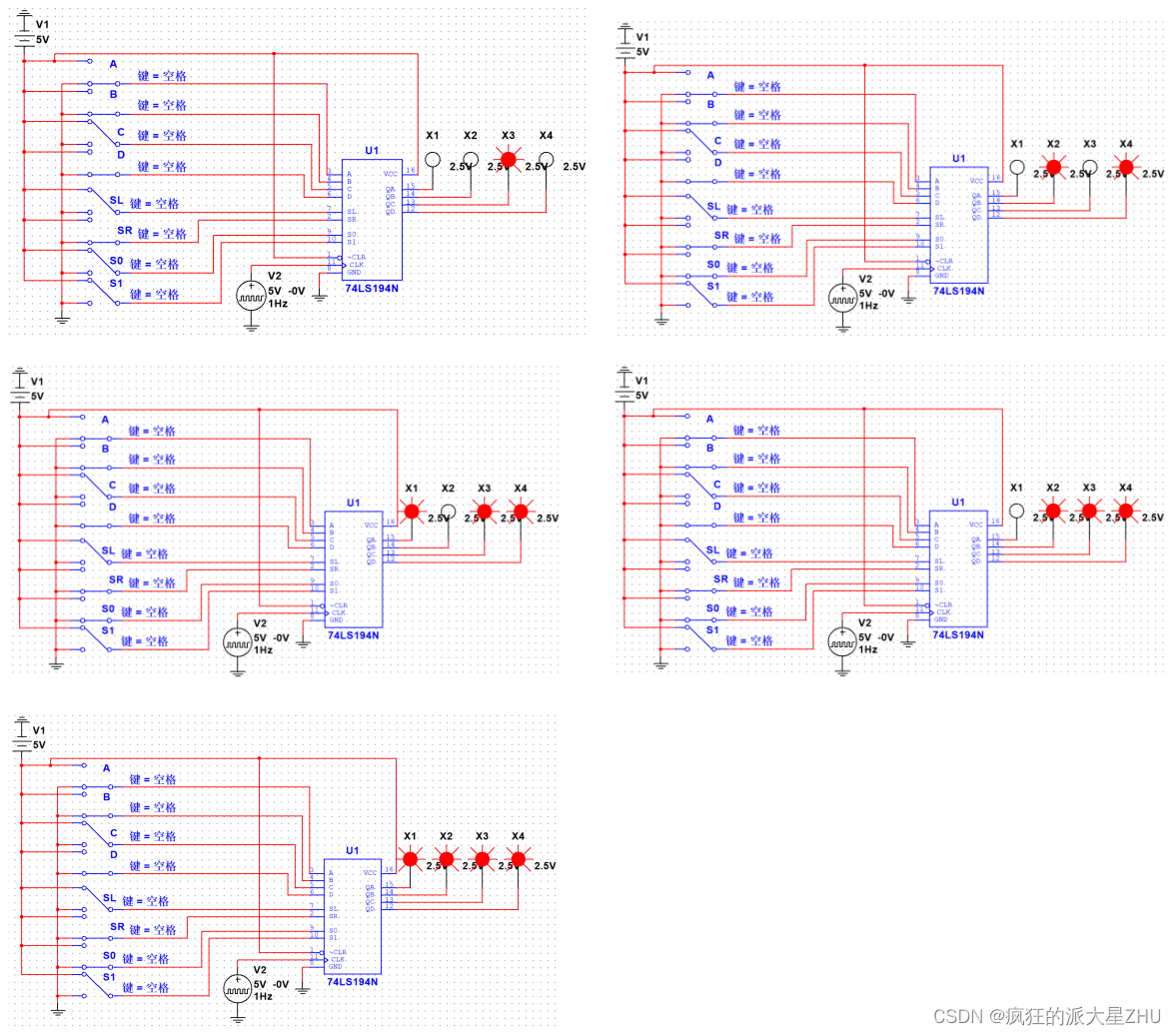

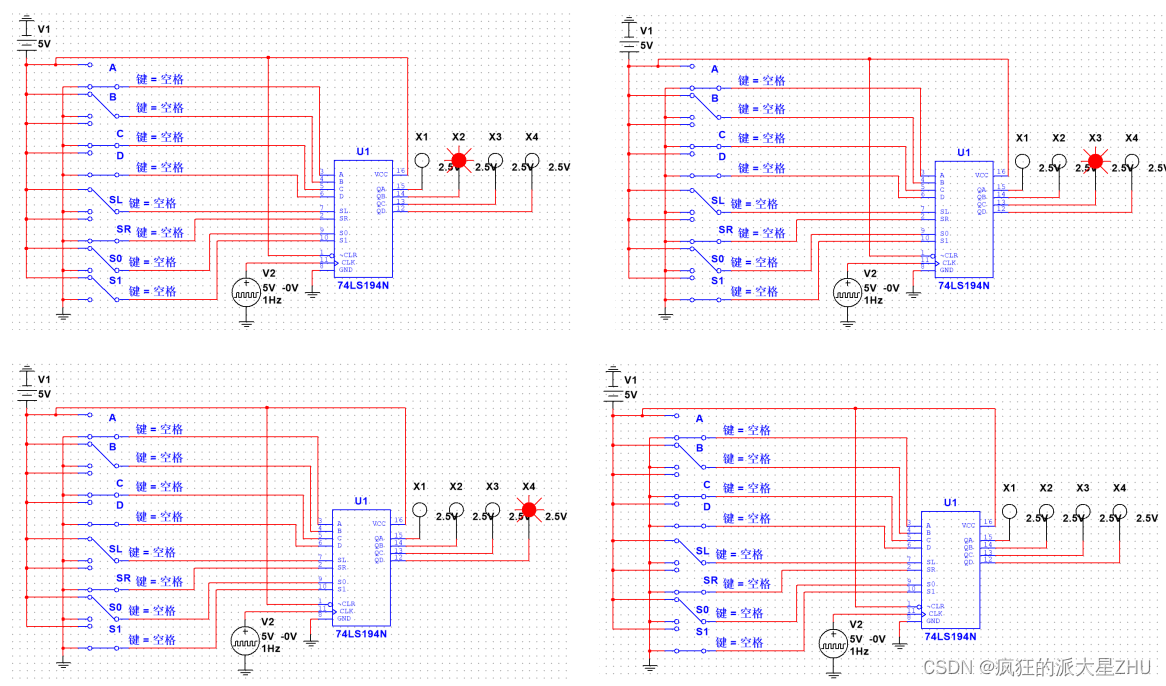

2、熟悉双向移位寄存器74194的功能,并调试使其正常工作。

(1)保持(S0=0,S1=0)

(2)串行左移(S0=0,S1=1)

①LEFT=1

②LEFT=0

(3)串行右移(S0=1,S1=0)

①RIGHT=1

②RIGHT=0

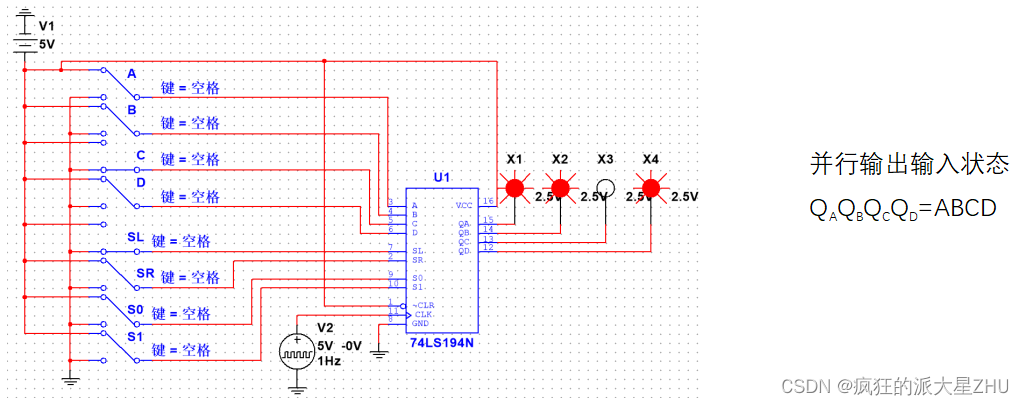

(4)并行(S0=1,S1=1)

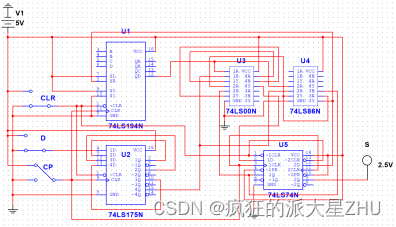

3、搭建全加器电路,并将进位寄存器7474添加进来,调试电路使其可以正常工作。

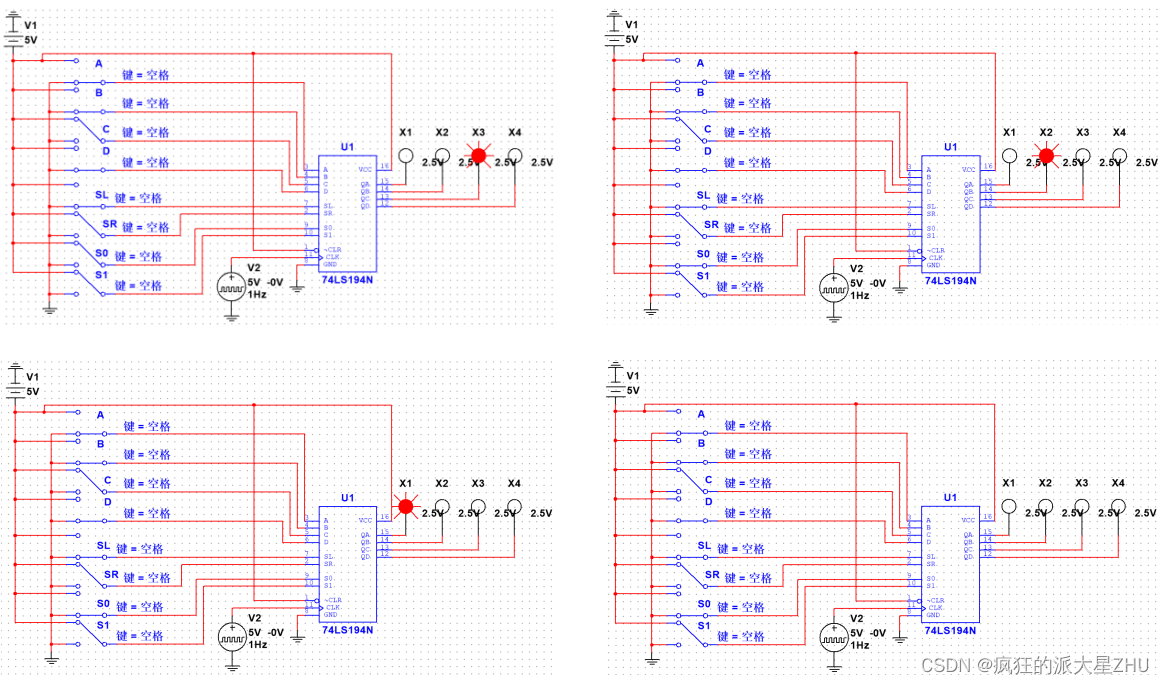

4、将移位寄存器和全加器连接起来构成一个移位寄存和串行累加系统,调试电路使其可以正常工作。完成1010+0011=1101的加法运算。

串行输入0101:

串行输入1100:

按键四次输出结果1011(1010+0011输出结果1101):