设计约束

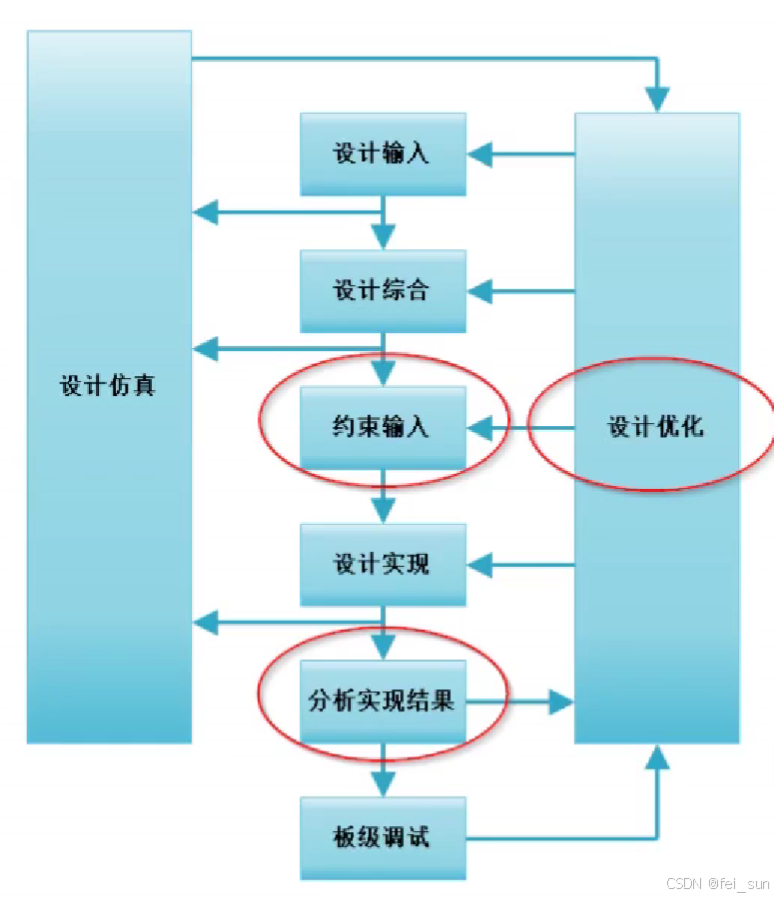

设计约束所处环节:

约束输入

分析实现结果

设计优化

设计约束分类:

物理约束:I/O接口约束(例如引脚分配、电平标准设定等物理属性的约束)、布局约束、布线约束以及配置约束

时序约束:设计FPGA内部的各种逻辑或走线的延时,反映系统的频率和速度的约束

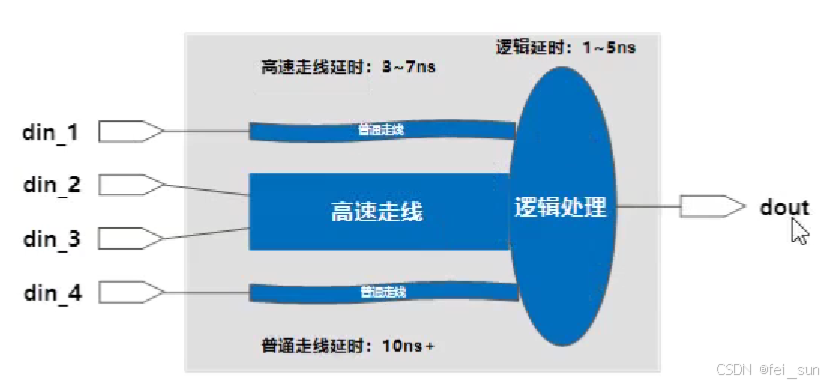

时序约束的目的:让FPGA编译工具合理地调配FPGA内部有限的布局布线资源,尽可能地满足设计者设定的所有时序要求(主要是将走线、逻辑电路等产生的延时限制在指定的范围内)

时序约束的定义

设计者根据实际的系统功能,通过时序约束的方式提出时序要求;FPGA编译工具根据设计者的时序要求,进行布局布线;编译完成后,FPGA编译工具还需要针对布局布线的结果,套用特定的时序模型(FPGA器件厂商能够使用这样的模型,对FPGA布局布线后的每一个逻辑电路和走线计算出延时信息),给出最终的时序分析和报告;设计者通过查看时序报告,确认布局布线后的时序结果是否满足设计要求

时序过约束和时序欠约束

没有任何设计约束的工程,编译器的工作就如同“脱缰的野马”般漫无目的且随意任性;

任何的时序过约束(over-constraining,时序约束过于严格,超过实际设计的要求)或时序欠约束(under-constraining,时序约束过于松散,低于实际设计的要求),都可能导致时序难以收敛(即难以达到设计要求)。因此,为了达到特定应用的设计要求,设计者必须设定合适的时序约束

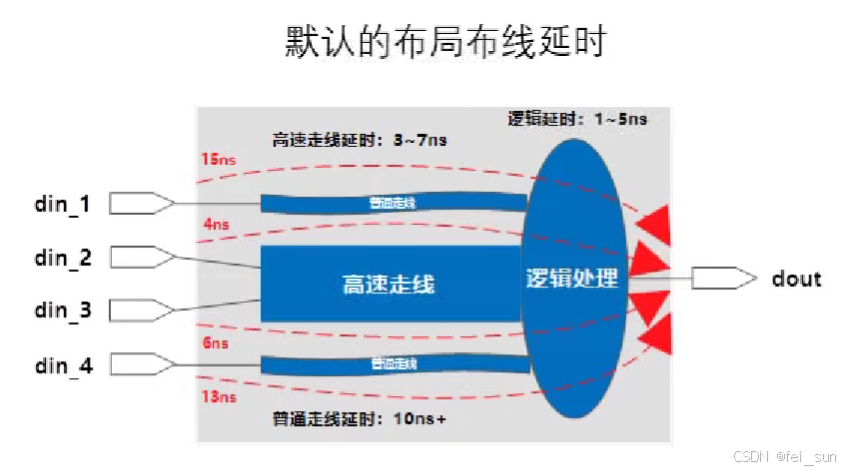

设计约束实例

设计需求:din1<10ns , din2<10ns , din3<20ns , din4<20ns

没有时序约束的情况(可能满足,也可能不满足,不确定)

合理的时序约束

时序欠约束(din1和din2欠约束):din1<20ns , din2<20ns , din3<20ns , din4<20ns

din1或din2若被分配到>10ns的两条普通走线,则时序违规

时序过约束(din3和din4过约束):din1<10ns , din2<10ns , din3<10ns , din4<10ns

受到实际资源限制,时序报告总是时序违规(Fail)

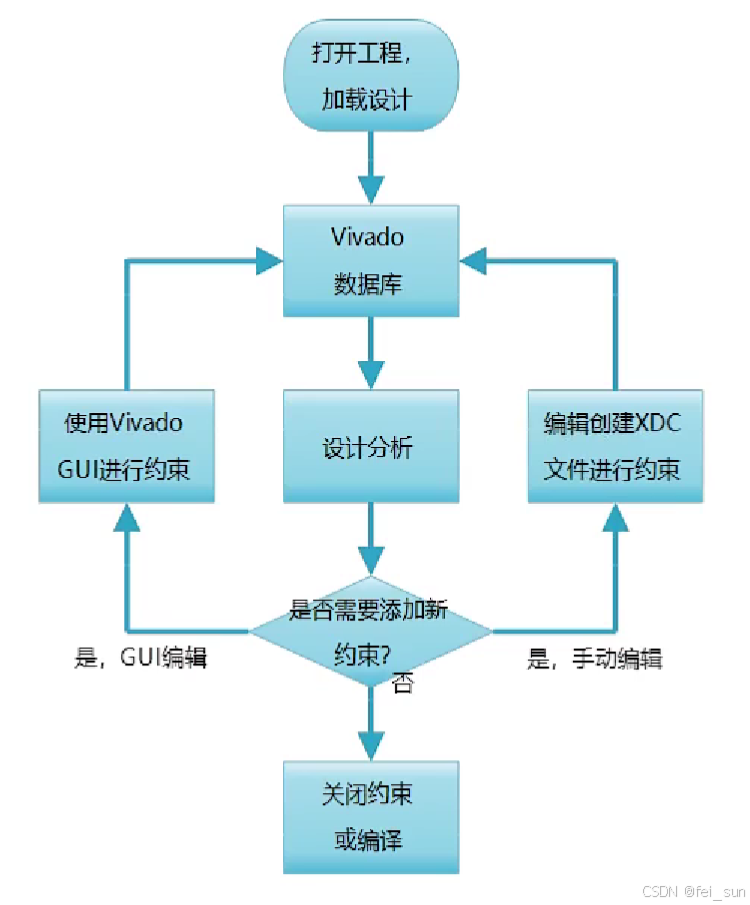

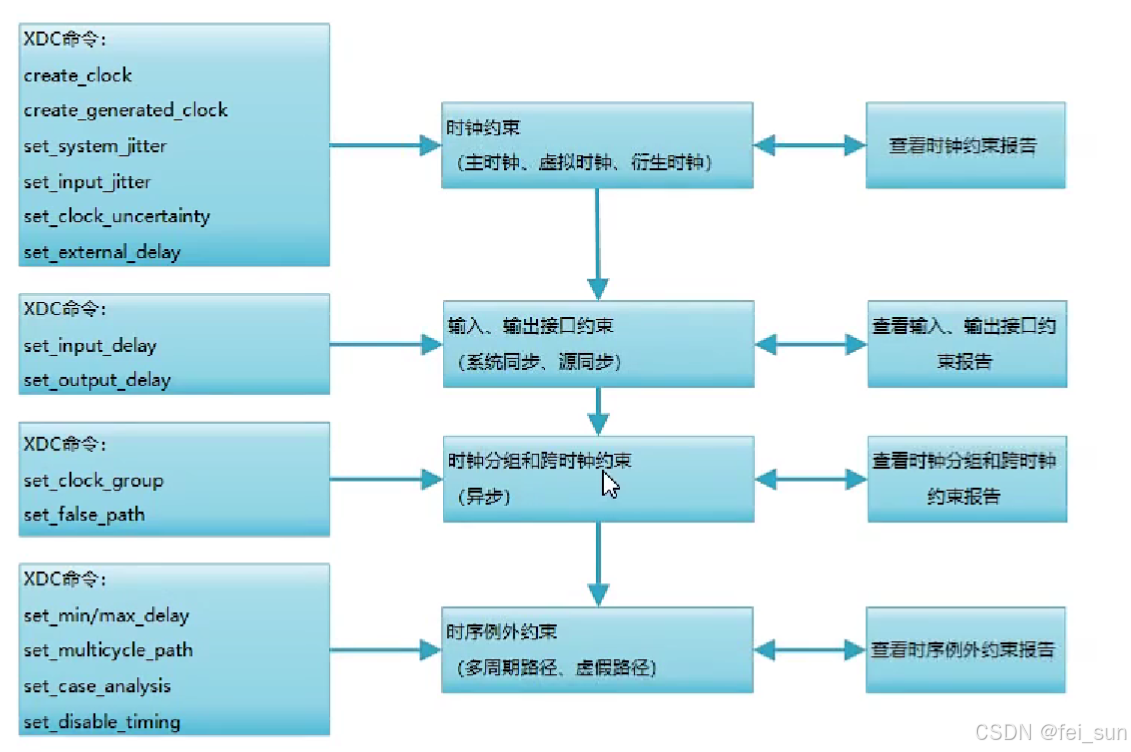

基于Vivado的时序约束方法

时序约束基本步骤

.xdc 引脚分配

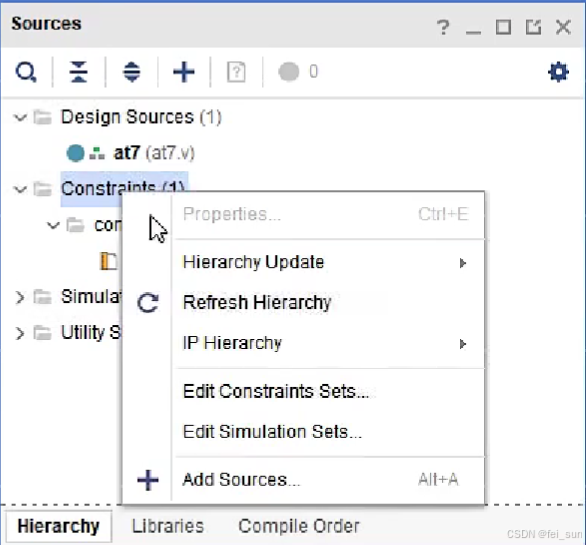

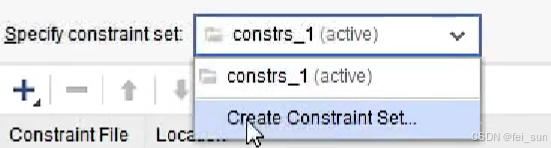

Edit Constraints Sets...

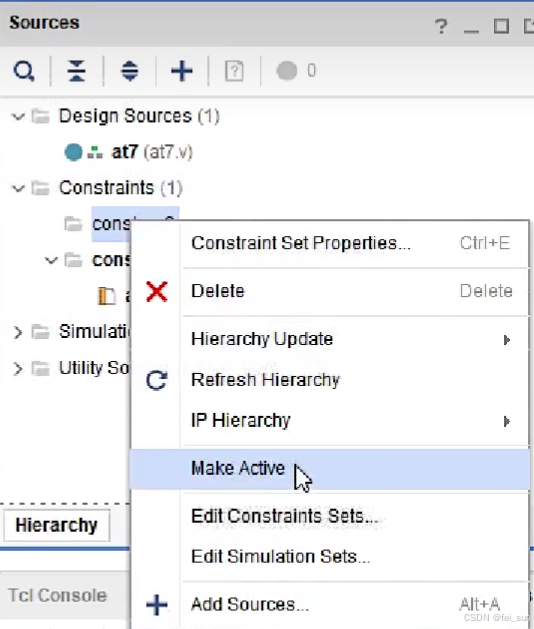

Make active

右键constrs_2,选择Add Sources...,add or create constraints

at7_pins 物理约束、引脚约束

at7_timing 时序约束

Vivado界面

SYNTHESIS

Run Synthesis

Constraints Wizard ,Define Target(存到哪个文件),再次点击Constraints Wizard,识别时钟,Frequency(MHz)可以设置,或使用默认

Edit Timing Constraints,Timing Constraints,Period(ns)时钟周期

切换xdc保存文件,右键要保存的文件,Set as Target Constraint File,此时该文件后面就会出现(target)

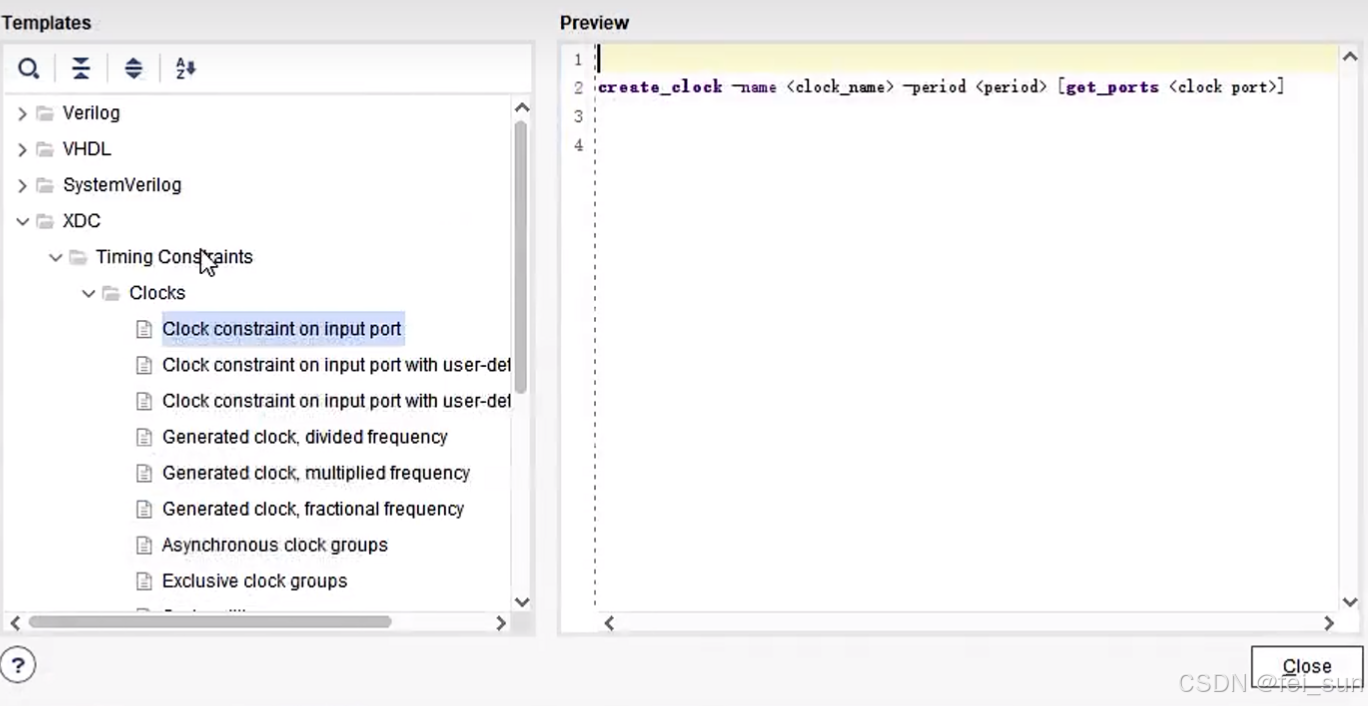

Vivado也提供xdc约束脚本模版:

PROJECT MANAGER

Setting

Language Templates

时钟与时钟偏差

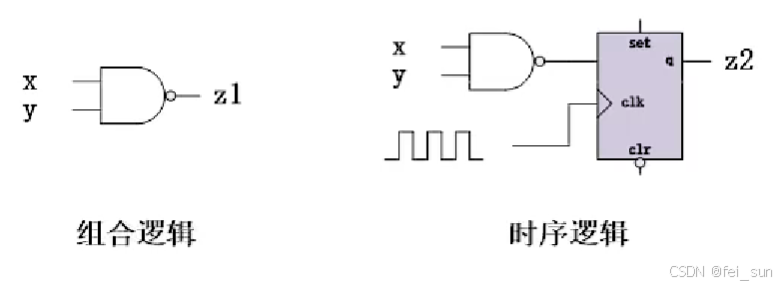

时序逻辑:输出在时钟沿的触发下才能更新输入的变化

组合逻辑:无需时钟沿的触发,输出立刻更新输入的变化

主要差异:

组合逻辑的输出与输入直接相关,时序逻辑的输出和原有状态也有关

组合逻辑立即反应当前输入状态,时序逻辑还必须在时钟上升沿触发后输出新值

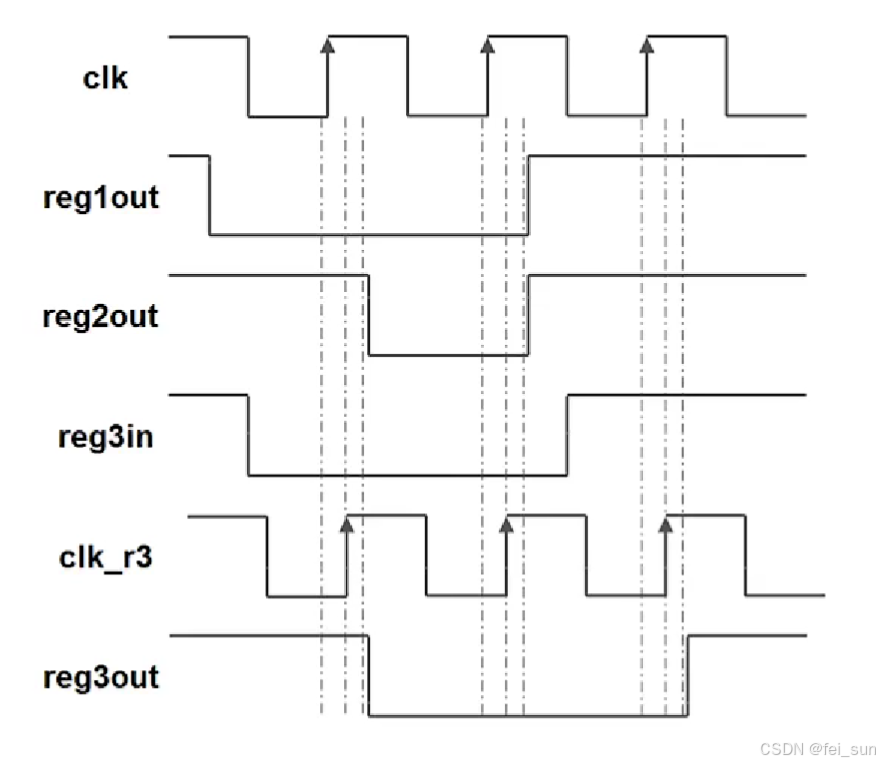

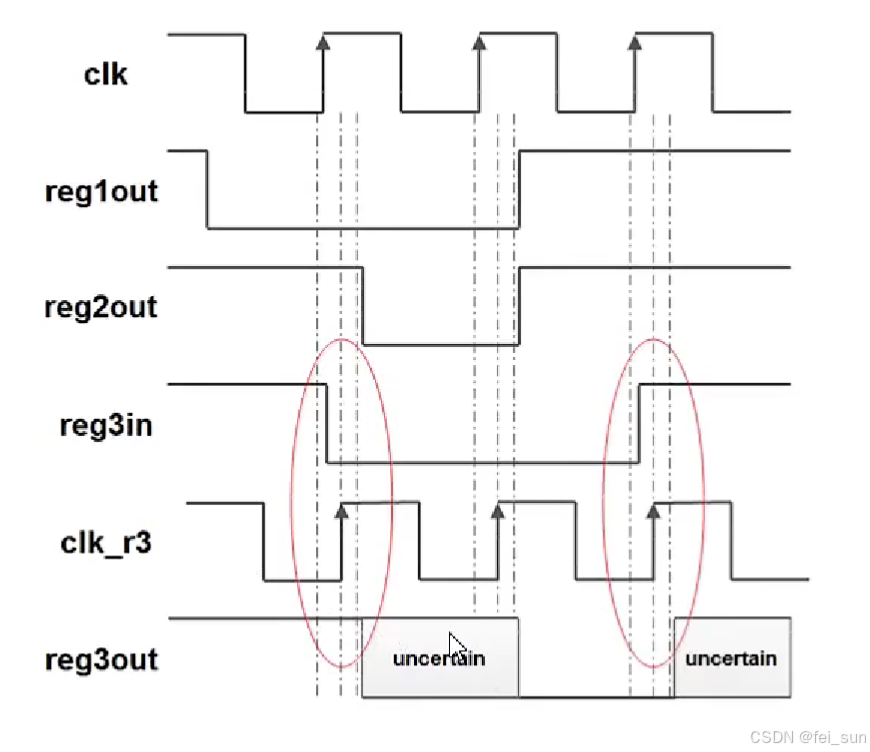

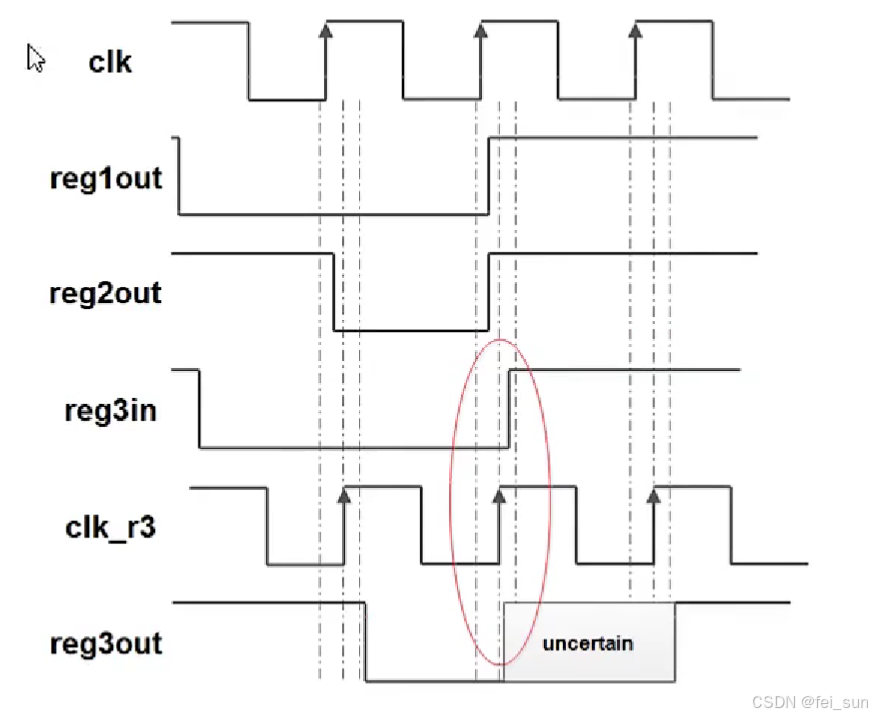

组合逻辑容易出现竞争、冒险现象(组合逻辑中,同一信号经不同的路径传输后,到达电路中的某一会合点的时间有先有后,这种现象称为逻辑竞争,而因此产生输出干扰脉冲的现象称为冒险),时序逻辑一般不会出现竞争、冒险现象

组合逻辑的时序较难保证,时序逻辑更容易达到时序收敛,时序逻辑更可控

组合逻辑只适合简单的电路,时序逻辑能够胜任大规模的逻辑电路

基本时钟模型

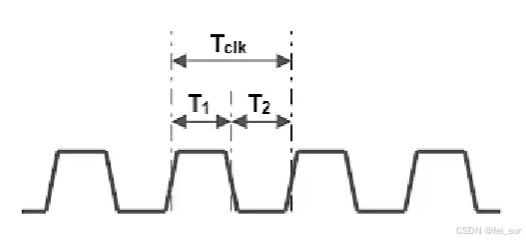

Tclk为一个时钟周期(单位:秒,FPGA的时钟周期一般为纳秒级别,即ns)

时钟的倒数1/Tclk即为时钟频率(单位:Hz,FPGA的时钟频率一般为MHz级别,1MHz=1,000,000Hz)

T1为高脉冲时间宽度,T2为低脉冲时间宽度,Tclk=T1+T2

时钟信号的高脉冲宽度与周期之比T1/Tclk即该时钟信号的占空比

时钟频率是FPGA设计性能一个很重要的指标,但是,单纯的时钟频率并不是衡量设计性能好坏的唯一指标。FPGA设计中,还有并行结构、流水线结构等体系架构方式也是设计性能的重要影响因素。

时钟偏差

无论是来自外部晶振的时钟信号,还是在FPGA内部经过PLL产生的时钟信号,它们的周期都无法保证绝对的精准,影响时钟周期准确性的因素有很多,比如材料、工艺、温度以及各种噪声等。这些对时钟周期的准确性产生的影响导致了时钟的偏差。

在FPGA内部集成的PLL,FPGA编译工具在做时序分析时可以直接套用既有模型给出的时钟的偏差参数,作为一部分需要预留的时序余量计算在内。而外部晶振所产生的时钟信号,设计者需要指定相关的时钟偏差参数,以时序约束的方式告知FPGA编译工具

时钟主要参数

时钟精度(Frequency tolerance)、时钟温漂(Frequency versus temperature characteristic)和时钟抖动(jitter)

以SiTime公司的SiT8021系列晶振规格书为例

精度Initial Tolerance -15~+15 ppm(part per million百万分率或百万分之几)

100MHz也就是10ns,每个时钟周期会产生的时钟偏差为+-15*10的-6次方

抖动RMS Period Jitter 75~110ps (1皮秒=1000,000纳秒,1万亿分之一秒,10的-12次方秒)

温漂Frequency Stability

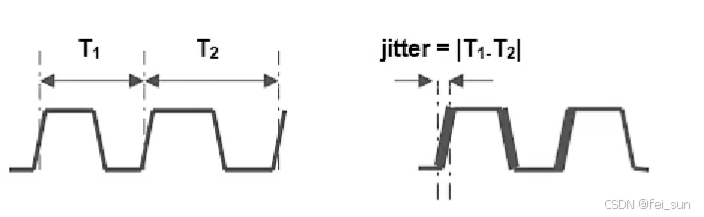

时钟抖动

晶振源固有的噪声和干扰通常会带来时钟信号的周期性的偏差,称之为始终抖动(jjitter),其单位一般是ps

FPGA时序约束分析中,也会将时钟抖动作为时钟不确定性(uncertainty)的一部分加以约束

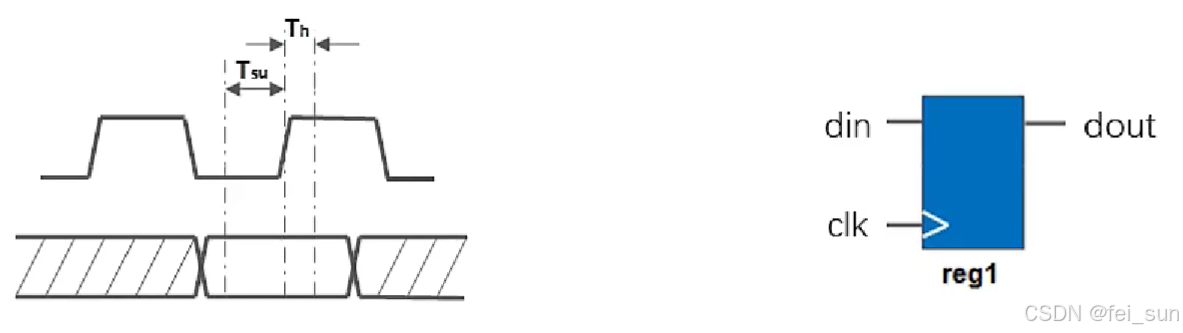

建立时间和保持时间

建立时间(Setup Time,Tsu),是指在时钟上升沿到来之前数据必须保持稳定的时间

保持时间(Hold Time,Th),是指在时钟上升沿到来以后得数据必须保持稳定的时间

一个数据需要在时钟的上升沿被锁存,那么这个数据就必须在这个时钟上升沿的建立时间和保持时间内保持稳定;换句话说,就是在这段时间内传输的数据不能发生任何的变化

建立时间违规

保持时间违规

时序分析中路径、沿和关系的定义

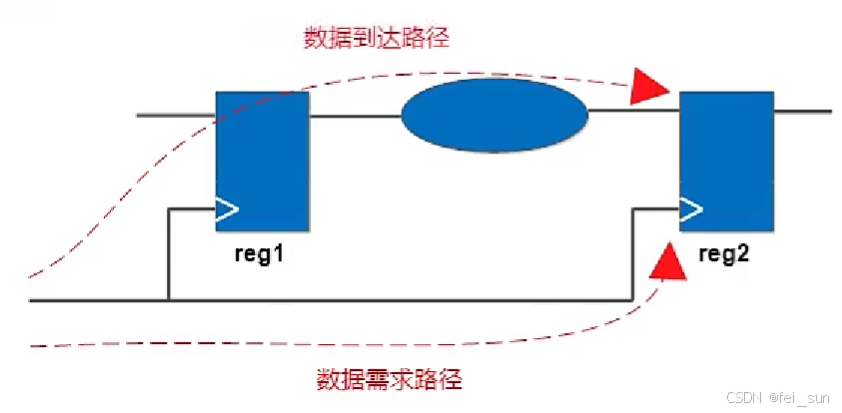

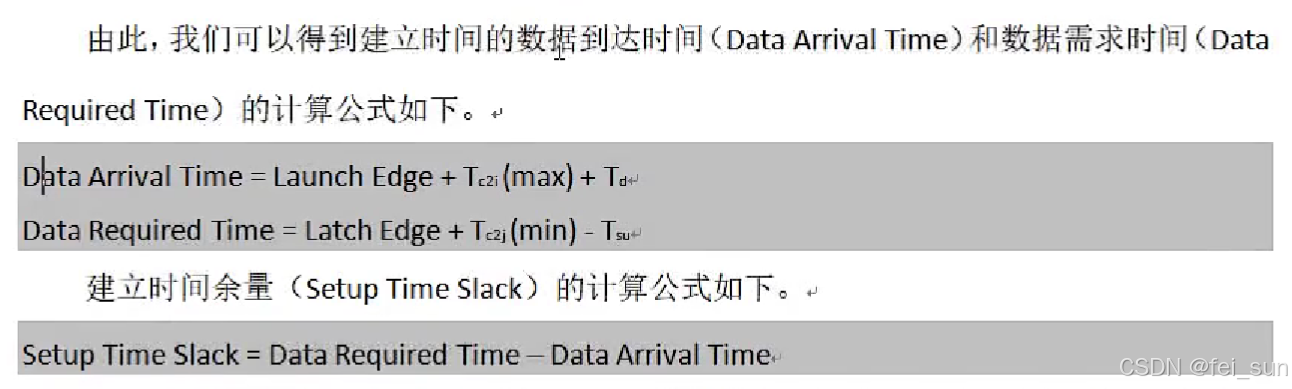

数据到达路径(data arrival path),是指数据在两个寄存器间传输的实际路径,由此路径可以算出数据在两个寄存器间传输的实际时间

数据需求路径(data require path),是指为了确保稳定、可靠且有效的传输(即满足相应的建立时间和保持时间要求),数据在两个寄存器间传输的理论所需时间的计算路径

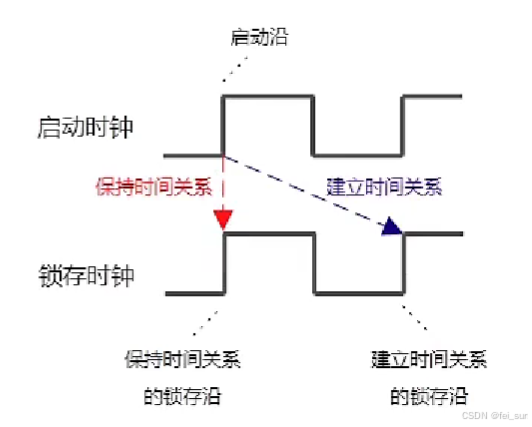

时钟启动沿和锁存沿、建立时间关系和保持时间关系

时钟启动沿:传输到源寄存器的时钟沿

时钟锁存沿:传输到目的寄存器的时钟沿

建立时间关系:

当前数据从源寄存器的时钟启动沿,经过一定的延时,最终到达目的寄存器的时钟锁存沿,保证当前数据被锁存的建立时间得到满足

启动沿从时间上看就要比锁存早一个时钟周期,即他们之间通常是相差一个时钟周期的关系

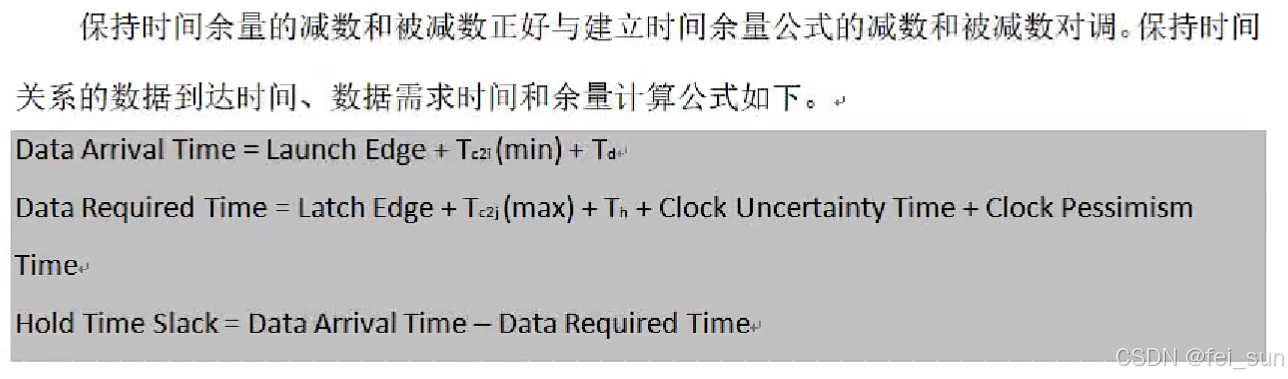

保持时间关系:

当前数据从源寄存器的时钟启动沿,经过一定的延时,最终达到目的寄存器的时钟锁存沿,保证上一个数据的保持时间得到满足

启动沿和锁存沿所分别对应的时钟其实是同一个时钟周期由时钟源传输过来的时钟信号

寄存器到寄存器的时序路径分析

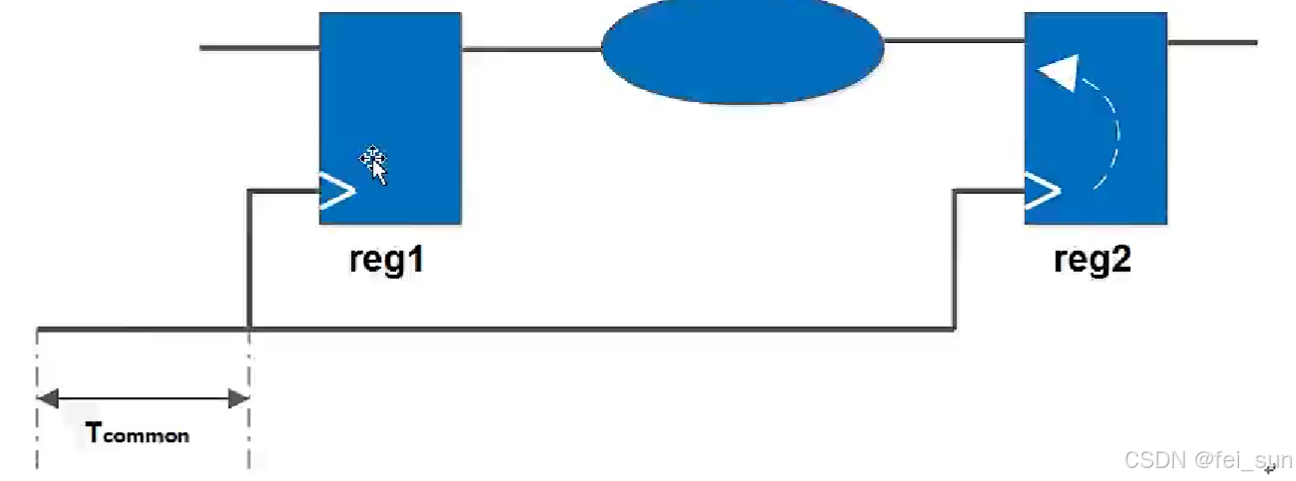

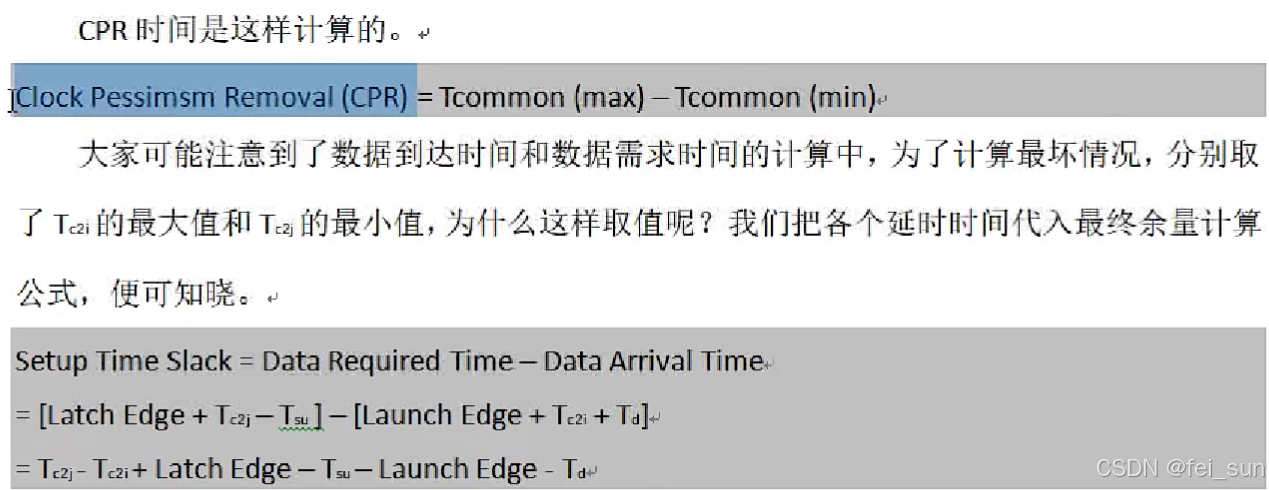

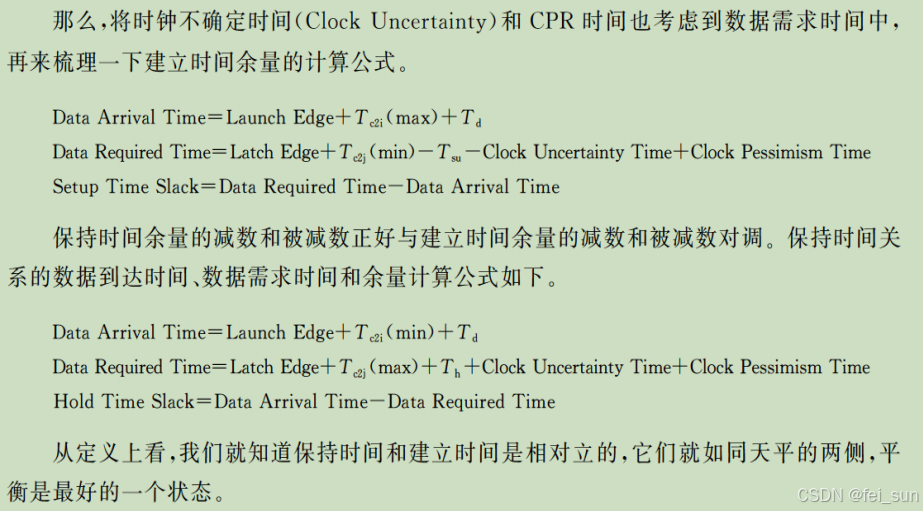

时钟共同路径

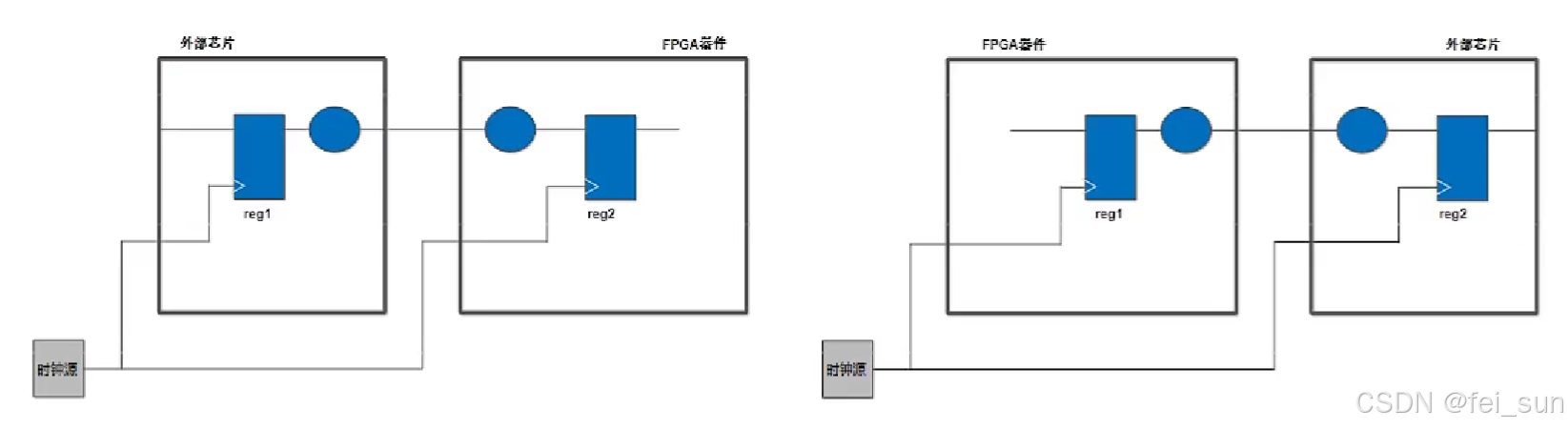

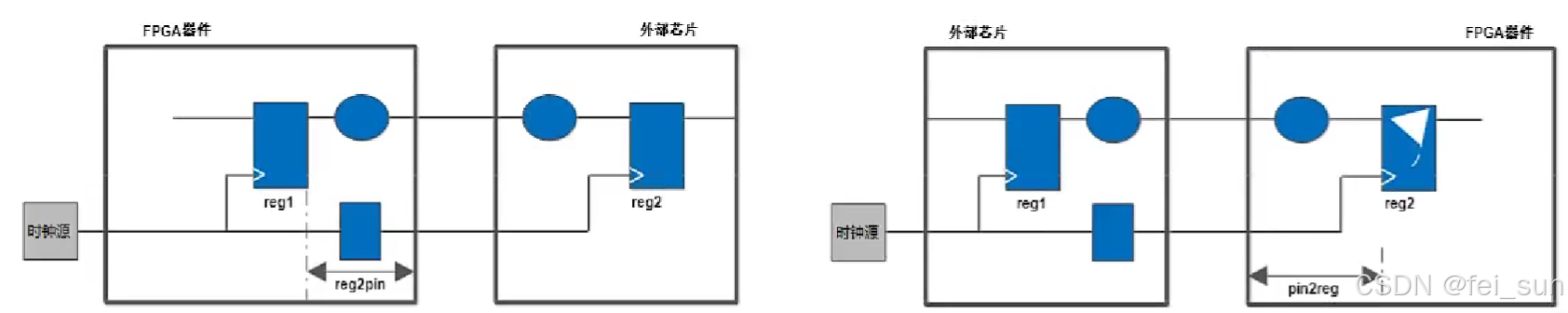

系统同步接口与源同步接口

系统同步接口

FPGA与外部芯片之间的通信时钟都由外部同一时钟源(系统时钟)产生时,我们称之为系统同步接口

源同步接口

FPGA与外部芯片之间的通信时钟都由源寄存器所在一侧(输出端)产生时,我们称之为源同步接口