对于数字系统而言,建立时间(setup time)和保持时间(hold time)是数字电路时序的基础。数字电路系统的稳定性,基本取决于时序是否满足建立时间和保持时间。我自己在初学时一度很难理解清楚他们的概念,在这里用笔记的方式尽量详细解释建立时间和保持时间的要点。

1. 基本概念

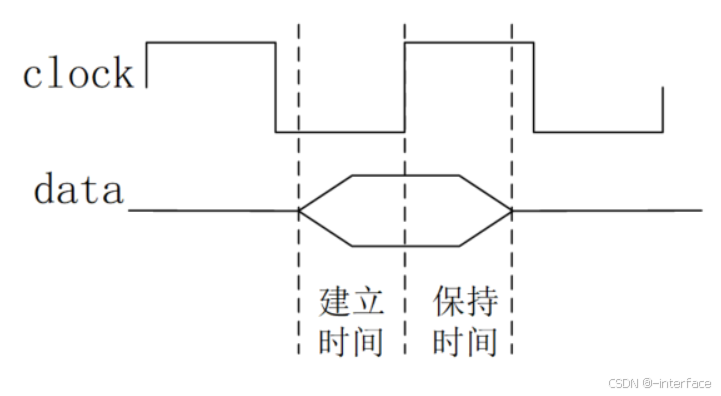

建立时间就是时钟触发事件来临之前,数据需要保持稳定的最小时间,以便数据能够被时钟正确的采样。

保持时间就是时钟触发事件来临之后,数据需要保持稳定的最小时间,以便数据能够被电路准确的传输。

可以通俗的理解为:时钟到来之前,数据需要提前准备好;时钟到来之后,数据还要稳定一段时间。建立时间和保持时间组成了数据稳定的窗口,如下图所示。

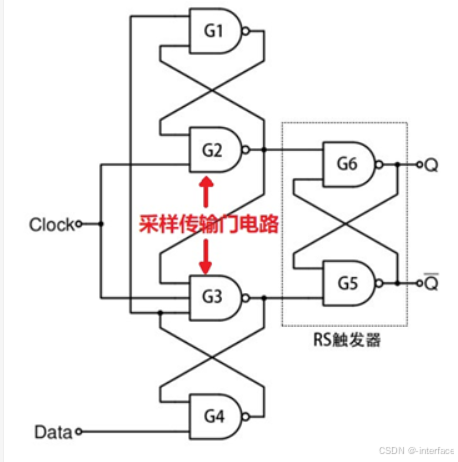

来看一个简单的上升沿D触发器,先试着理解一下保持时间和维持时间的概念。

G1~G4 与非门是维持阻塞电路,G5~G6 组成 RS 触发器。

时钟直接作用在 G2/G3 门上,时钟为低时 G2/G3 通道关闭,为高时通道打开,进行数据的采样传输。但数据传输到 G2/G3 门之前,会经过 G4/G1 与非门,将引入时间延迟。引入建立时间的概念,就是为了补偿数据在 G4/G1 门上的延迟。即时钟到来之前,G2/G3 端的输入数据需要准备好,以便数据能够被正确的采样。

数据被时钟采样完毕后,传输到 RS 触发器进行锁存之前,也需要经过 G2/G3 门,也会引入延迟。保持时间就是为了补偿数据在 G2/G3 门上的延迟。即时钟到来之后,要保证数据能够正确的传输到 G6/G5 与非门输入端。

如果数据在传输中不满足建立时间或保持时间,则会处于亚稳态,导致传输出错。

2. 约束条件

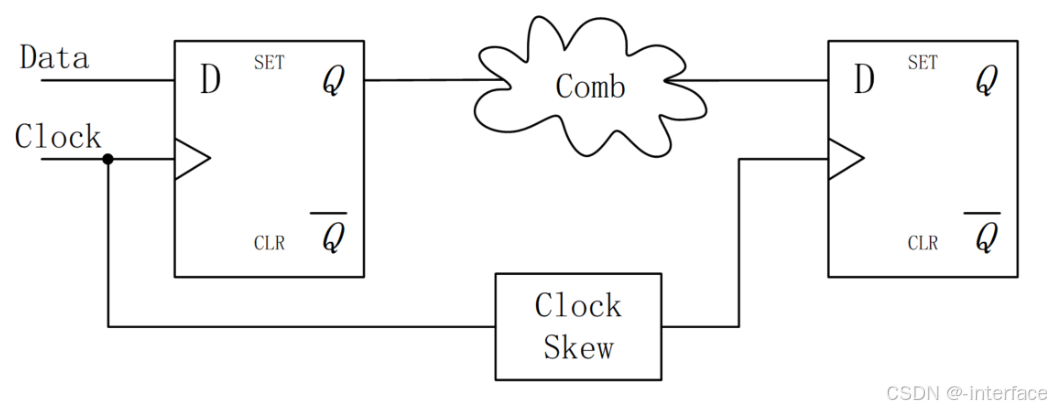

2.1 建立时间约束

以一个典型DFF到DFF的数据传输路径举例,其中 "Comb" 代表组合逻辑延迟,"Clock Skew" 表示时钟偏移,数据均在时钟上升沿触发。时钟到来之前,数据需要提前准备好,才能被时钟正确采样,要求数据路径 (data path) 比时钟路径 (clock path)更快,即数据到达时间(data arrival time)小于数据要求时间(data required time)。则建立时间需要满足的表达式为:

各个时间参数说明如下:Tcq: 寄存器 clock 端到 Q 端的输出延迟;Tcomb:data path 中的组合逻辑延迟;Tsu: 建立时间;Tclk: 时钟周期;Tskew: 时钟偏移。等式左边部分为data path,右边部分为clk path,由此我们又可以得到理论上电路能够承载的最小时钟周期和最高时钟频率分别为:

由上述公式,我们又可以总结出:更大的时钟偏移Tskew、更短的输出延迟Tcq、组合逻辑延时Tcomb有助于满足建立时间约束条件。

2.2 保持时间约束

时钟到来之后,数据还要稳定一段时间,这就要求前一级的数据延迟(data delay time)不要大于触发器的保持时间,以免数据被冲刷掉。那么保持时间需要满足的表达式为:

同样的,等式左边体现的是数据路径,而右边是时间路径,这也是需要理解记忆的两个约束条件表达式。对于保持时间,也可以总结出:更小的时钟偏移Tskew、更长的输出延迟Tcq、组合逻辑延时Tcomb有助于满足保持时间约束条件。

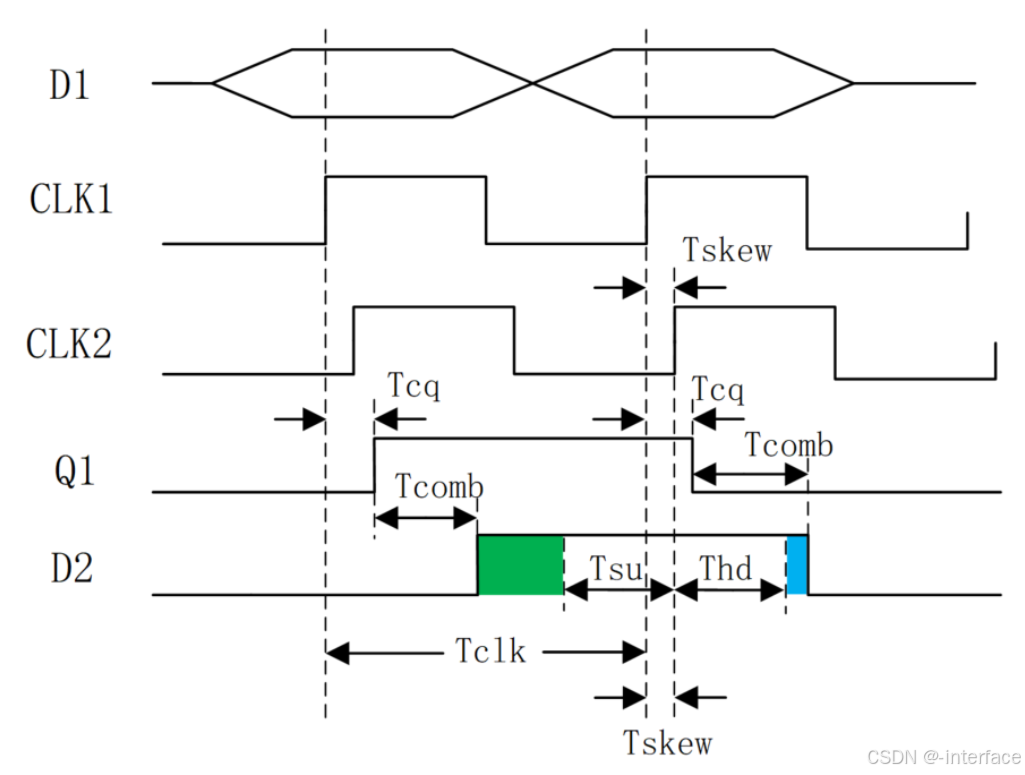

3. 建立时间、保持时间时序图

结合波形,可以再次理解一下建立时间和保持时间;图中绿色部分表示建立时间的裕量(margin),蓝色部分表示保持时间的裕量。时间裕量,其实就是电路在满足时序约束的条件下,不等式两边时间的差值。

建立时间裕量为:时钟路径时间 - 数据路径时间

保持时间裕量为:数据延迟时间 - (保持时间+时钟偏移)

4. 题目举例

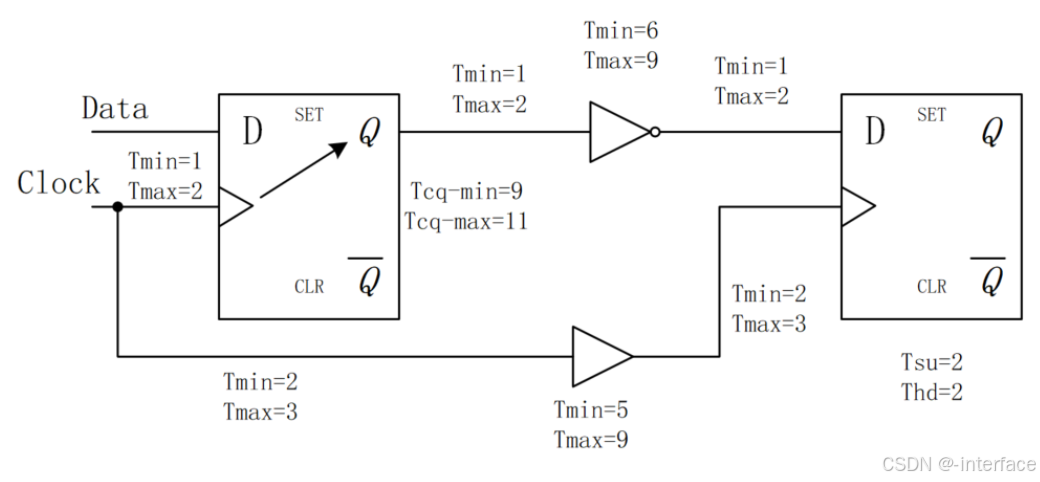

Q1:考虑线网延迟,某电路各种延迟值(单位:ns)如下,时钟周期为 15ns,请判断该电路的建立时间和保持时间是否存在violation?

A1: 根据约束条件不等式,建立时间有:11+2+9+2+2>15+2+5+2-2,max data path time超过了min clk path time,因此存在建立时间violation。保持时间有:9+1+6+1>3+9+3-1+2,满足保持时间约束,不存在hold violation。

Q2:某公司面试题:时钟周期为 T, 第一级触发器 D1 建立时间最大值为 T1max,最小值为 T1min。组合逻辑最大延迟为 T2max, 最小值为 T2min。问:第二级触发器 D2 的建立时间和保持时间应该满足什么条件?

A2: