3.2 高级纠错算法

随着DRAM容量和带宽需求的增加,堆叠Die结构成为广泛应用的趋势。同时,为了最小化错误纠正过程中对延迟的影响,人们倾向于在DRAM芯片内部直接实现ECC技术以应对多比特错误。然而,受限于内存中的面积、延迟和功耗约束,实现强大的多比特错误纠正ECC面临着重大挑战。例如,尽管Chipkill技术在服务器环境中广泛用于有效处理DRAM中的单个或多个错误,但在高容量存储架构中,其应用受到了延迟效率低下的限制。

3.2.1 多Bit纠错与检测算法

多比特错误纠正与检测技术主要是针对随着技术发展而日益显著的软错误问题,尤其是当这些软错误影响超过一个比特时,传统的只能纠正单个错误或在某些情况下检测到双比特错误的编码方法已显得不足。由于技术缩放,软错误同时影响多个比特的概率大大增加,因此需要更先进的纠错技术来应对。

(1)SEC-DAEC(单错误纠正-双相邻错误纠正)

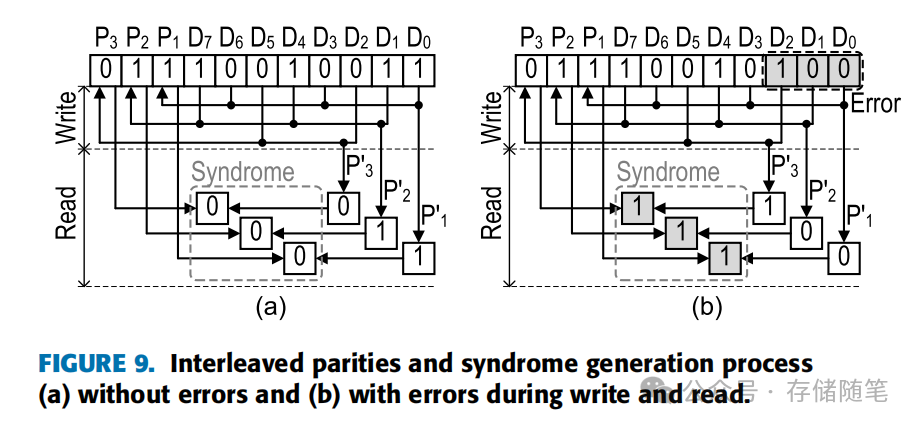

SEC-DAEC是一种能够纠正最多两个相邻错误的技术,它通过一种称为交错奇偶校验(Interleaved Parity, IP)的方法来实现。在这一技术中,奇偶校验位不仅在写入时生成,也在读取时独立生成。通过异或运算(XOR)比较写入和读取时产生的奇偶校验位来计算Syndrome,以此识别是否存在错误以及错误的位置。例如,数据D0、D1、D2在没有错误的情况下,写入时会生成对应的奇偶校验位P1、P2、P3。读取时,会产生额外的奇偶校验位P'1、P'2、P'3。如果所有计算出的Syndrome位为000,则表明没有错误;如果有误,则可能得到如111的结果,据此可以定位错误并进行纠正。

(2)SEC-DEC-TAEC(单错误纠正-双错误纠正-三相邻错误纠正)

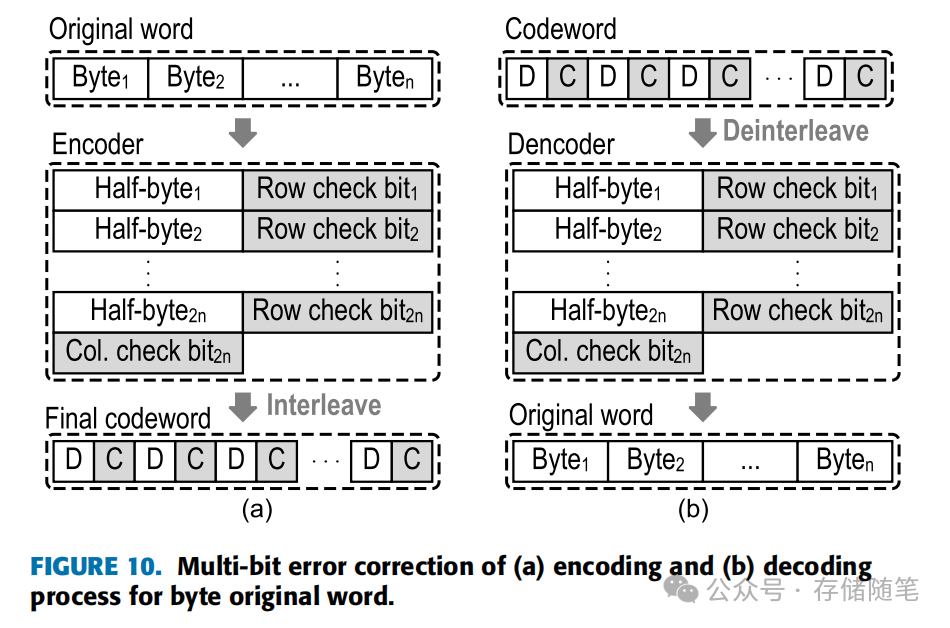

相比SEC-DAEC,SEC-DEC-TAEC技术进一步增强了纠错能力,能够纠正两个独立错误及三个相邻错误,提供了更强大的错误纠正功能和更高的可靠性。其编码过程涉及将原始字节数据分为两倍数量的半字节,并在行和列方向上分别生成校验位,随后通过交织操作重组数据和校验位,形成最终的码字。解码时再进行逆交织,恢复原始数据和校验位,进行错误检测和纠正。

-

图10 描述了使用SEC-DEC-TAEC为原始字节数据生成特定校验位的过程,包括编码、交织、解码等步骤。

-

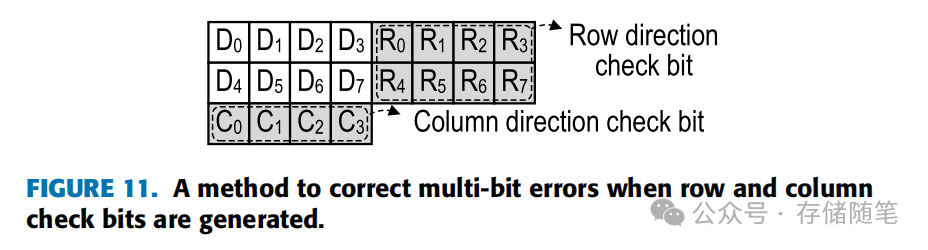

图11 展示了如何利用图10中生成的码字来纠正多比特错误。在此图中,D0至D7代表每个半字节,R0至R7为行方向上的校验位,C0至C3为列方向上的校验位。这些校验位帮助确定数据的具体位置,从而纠正最多两个非相邻错误或三个相邻错误。

虽然SEC-DEC-TAEC提供了更强大的纠错能力,但每半个字节生成一个校验位,相较于传统的SECDED,校验位的使用量超过了三倍,这导致其在功率消耗、芯片面积占用以及访问延迟方面有更高的要求。因此,采用SEC-DEC-TAEC时需要在性能提升与资源消耗之间做出权衡。

3.2.2 高级CRC纠错算法

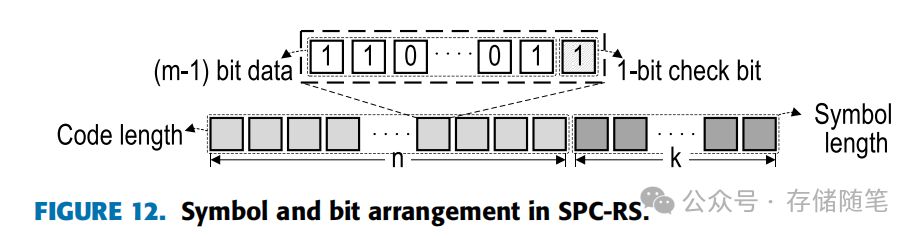

高级CRC技术近年来的研究集中在提升错误检测与纠正能力上,特别是通过将特定比特转换为符号,实现了单符号纠正(Single Symbol Correction, SSC)。这一策略结合了单奇偶校验(Single Parity Check, SPC)和RS码(Reed-Solomon Code),形成了SPC-RS码,如图12所示。这种编码方式中,每个码长包含n个符号,每个符号由m个数据比特组成,其中一个符号作为校验位来检测每个符号内的错误。这样的设计提升了错误检测和纠正的效率,尤其是在数据传输和存储系统中。

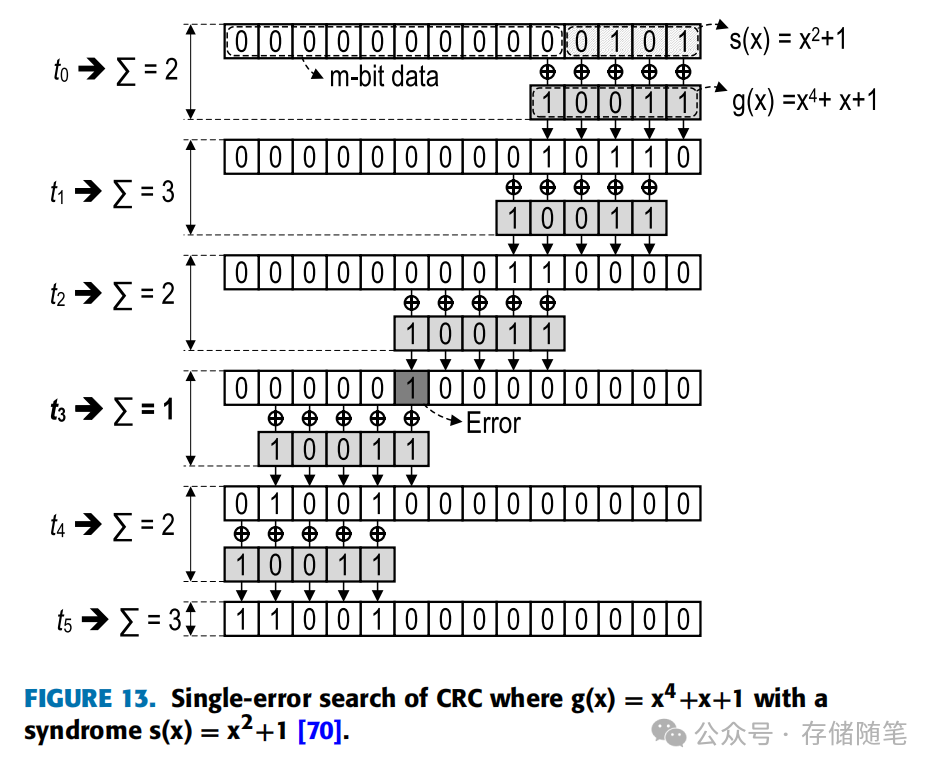

图13展示了一种不依赖查找表的CRC错误纠正方法,该方法使用了一个生成多项式g(x) = x^4 + x + 1,在生成了s(x) = x^2 + 1时,通过与m比特数据的组合结果进行XOR运算,从t0到t5逐步执行,最后通过计算所有数据的总和P来判断是否存在错误。如果P的值在t0, t1, t2, t4, 和t5中至少为2,而在t3中为1,即可识别出一个单独的错误。这种方法不仅能够检测单个错误,通过扩展g(x)多项式的序列,还可以实现对双错误的纠正。

3.2.3 On-Die ECC

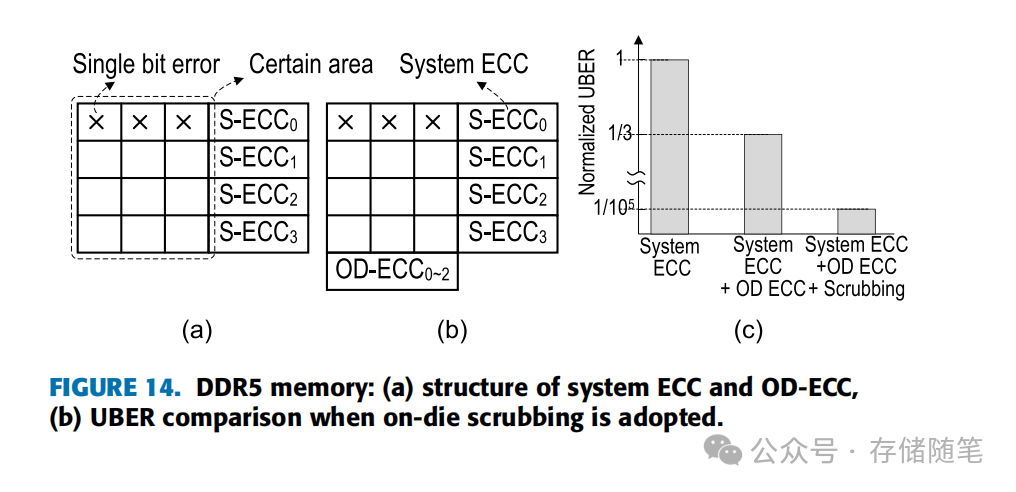

图14(a)展示的是DDR5内存的一个多比特错误校正结构示例,其中包含了四个系统ECC(Error Correction Code)和三个片上ECC(On-Die ECC,简称OD-ECC)。系统ECC采用了汉明码(72,64),意味着在72位编码中,有64位是数据位,8位是校验位;而每个OD-ECC则采用了(104,96)的汉明码,即在104位编码中有96位数据位和16位校验位。通过系统ECC和OD-ECC的同时应用,可以显著降低无法纠正的比特错误率(Uncorrectable Bit Error Rate, UBER)至原来的三分之一。

具体来说,如果没有OD-ECC,当内存中发生如图14(a)所示的3比特错误时,这将被视为无法纠正的错误(Unrecoverable Error, UE),可能导致数据丢失或系统故障。然而,图14(b)展示的情况中,由于OD-ECC与系统ECC相互正交(即它们检测和纠正不同类型的错误模式),这些3比特错误可以通过各自的OD-ECC得到纠正。这意味着随着OD-ECC数量的增加,尽管会占用更多的芯片面积,但UBER可以进一步减少。

图14(c)则通过模拟对比展示了仅使用系统ECC、仅使用OD-ECC以及结合使用这两种ECC加上刷新(scrubbing)技术的效果。系统ECC与OD-ECC的联合应用能将UBER降至原来的三分之一。当所有这三种技术(系统ECC、OD-ECC和刷新)共同作用时,UBER可进一步减小至10^-5水平。这样的改进极大地提升了系统的可靠性,使得内存错误更少发生,系统运行更加稳定。因此,这些高级ECC策略对于高密度、高速度的DDR5内存系统而言至关重要,确保了数据完整性和系统性能。

3.2.4 ECC纠错算法对比

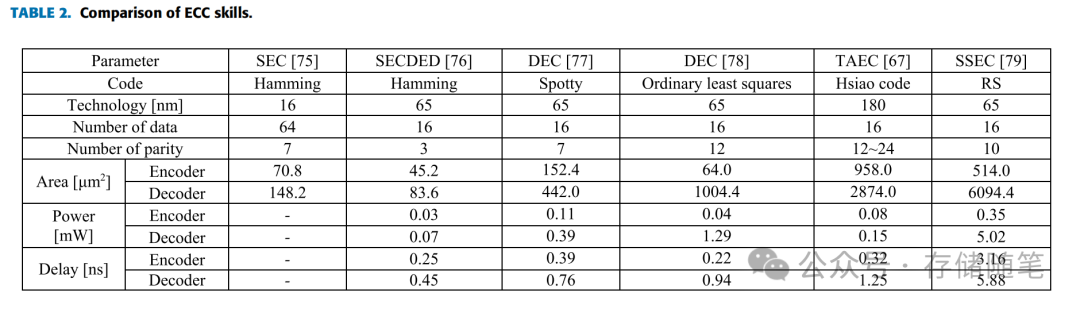

ECC比较分析通常涉及到评估不同ECC技术在关键性能指标上的表现,如所需的校验位数量、面积占用、功耗和延迟等,以适应不同数据宽度(如16位或64位)的应用场景。几种ECC技术的对比,这对于理解各种ECC方案的优势与限制至关重要。

-

单符号错误纠正(SSEC):SSEC技术通过使用符号纠正码来纠正多比特错误。这里的“符号”可以理解为一组连续的比特,其大小依据具体实现而定。SSEC的优点在于它能够处理单个符号内的多比特错误,提高了错误纠正能力。然而,随着需要纠正的错误数量增加,编码器和解码器的复杂度也随之上升,导致硬件实现的面积和功耗增大,以及数据处理的延迟可能增加。

-

校验位需求:不同ECC技术所需校验位的数量不同,这直接影响到存储空间的开销。例如,SECDED(可能只需要较少的校验位,而像SEC-DEC-TAEC或SSEC这样的高级ECC技术,为了实现更强大的纠错能力,可能需要更多的校验位。

-

面积与功耗:更复杂的ECC技术,如能够纠正多比特错误或相邻错误的方案,通常需要更大的硬件面积和更高的功耗。这是因为它们的编码和解码逻辑更为复杂,可能涉及更多逻辑门和存储单元。

-

延迟:ECC编码和解码过程会引入额外的处理时间,这对于高性能应用尤其敏感。简单的ECC方案如Hamming码可能带来较低的延迟,而复杂方案如Chipkill或SSEC则可能导致更高的访问延迟。

在选择适合内存系统的ECC方案时,需仔细权衡以下几个方面:

-

错误纠正需求:根据应用场景中预期的错误率和错误类型(如软错误或硬错误)来决定所需的ECC能力。

-

资源限制:考虑系统对面积、功耗和延迟的容忍度,特别是在高性能计算和移动设备中,这些因素可能成为关键设计约束。

-

实现成本:更高级的ECC技术虽然提供更好的错误纠正能力,但也可能带来更高的实现成本。

因此,ECC技术的选择是一个综合考量的过程,需要根据具体的系统需求、成本预算和性能目标来确定最佳方案。

完整分析解读参考:数据中心内存RAS技术全景剖析