注:相应的源文件在文末的github链接中

实验一 Vivado环境下组合电路的设计与仿真

一.实验要求

1. 在Vivado 环境下完成对简单电路工作情况的仿真模拟;

2. 实现以下组合逻辑功能:编码/译码器,比较器,全加器。

二.Led灯的控制电路实现

源文件

`timescale 1ns / 1ps

module led( input CLK , output reg[1:0] led_out );

reg [32:0] count=0;

parameter T1MS=50000000; //定义一个时间常量

always@(posedge CLK) //上升沿时钟(CLK)敏感

begin

count<=count+1; //非阻塞的赋值,每一个时钟周期count自动+1

if(count==T1MS)

begin //当计数器count到达时间常量就置零

count<=0;

end

if(count<25000000) //前半个周期

begin

led_out<=2'b01;

end

else begin

led_out<=2'b10; end //后半个周期

end endmodule

激励文件(注意可能需要改变延时时间为自己的学号)

module comp_tb();

reg CLK, RST; //输入信号

reg [1:0] A,B;

wire AGTB,ALTB,AEQB; //输出信号

comp cp(CLK,RST,A,B,AGTB,ALTB,AEQB); //调用实例

initial

begin//这个其实就是真值表的应用

RST = 1; CLK = 0;

A = 2'b00; B = 2'b01;

#73 A = 2'b00; B = 2'b00;

#73 A = 2'b00; B = 2'b01;

#73 A = 2'b10; B = 2'b01;

#73 A = 2'b11; B = 2'b10;

#73 A = 2'b01; B = 2'b01;

end

always #73 CLK = ~CLK;

endmodule

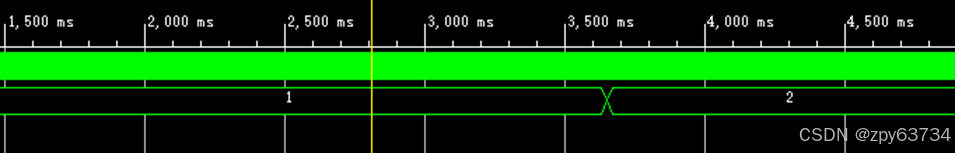

激励图像

三.编码器的实现

源文件

module encoder4_2(q,d);

input[3:0] d; //数据输入端 4

output[1:0] q; //输出端口 2

reg[1:0] q; // reg变量在always语句中赋值

always@(d)

begin

case(d)

4'b0111: q<=2'b11; //D3位有效输入

4'b1011: q<=2'b10; //D2位有效输入

4'b1101: q<=2'b01; //D1位有效输入

4'b1110: q<=2'b00; //D0位有效输入

default: q<=2'bzz;

endcase

end

endmodule

激励文件(注意可能需要改变延时时间为自己的学号)

`timescale 1ns / 1ps

module encoder4_2_tb();

reg [3:0] d; //输入信号

wire [1:0] q; //输出信号

encoder4_2 e2(q,d); //调用实例

initial

begin//这个其实就是真值表的应用

d = 4'b0111;

#73 d = 4'b1011;

#73 d = 4'b1101;

#73 d = 4'b1110;

end

endmodule

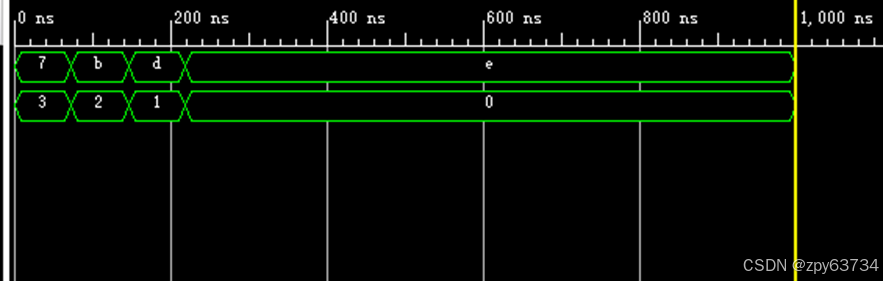

激励图像

四.比较器的实现

源文件

module comp(CLK,RST,A,B,AGTB,ALTB,AEQB);

input CLK,RST; //

input[1:0] A,B; //被比较的两个二位数字

output AGTB,ALTB,AEQB;

reg AGTB,ALTB,AEQB;

always@(posedge CLK or negedge RST) begin //对时钟信号的上升沿和清零信号的下降沿敏感

if(!RST) //如果清零

begin

AGTB<=0; AEQB<=0; ALTB<=0;

end

else

begin

if(A>B) //大于

begin

AGTB<=1; AEQB<=0; ALTB<=0;

end

else if(A==B) //等于

begin

AGTB<=0;

AEQB<=1;

end

else // 小于

begin

AGTB<=0; AEQB<=0; ALTB<=1;

end

end

end endmodule

激励文件(注意可能需要改变延时时间为自己的学号)

reg CLK, RST; //输入信号

reg [1:0] A,B;

wire AGTB,ALTB,AEQB; //输出信号

comp cp(CLK,RST,A,B,AGTB,ALTB,AEQB); //调用实例

initial

begin//这个其实就是真值表的应用

RST = 1; CLK = 0;

A = 2'b00; B = 2'b01;

#73 A = 2'b00; B = 2'b00;

#73 A = 2'b00; B = 2'b01;

#73 A = 2'b10; B = 2'b01;

#73 A = 2'b11; B = 2'b10;

#73 A = 2'b01; B = 2'b01;

end

always #73 CLK = ~CLK;

endmodule

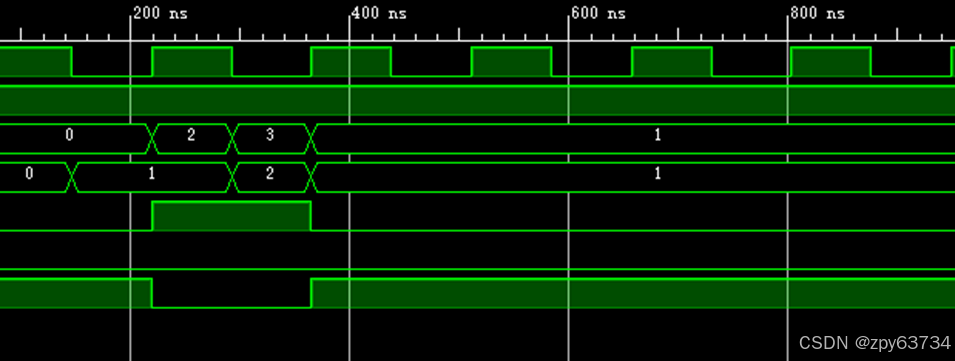

激励图像

五.全加器的实现

源文件

module ful_adder(cout,sum,a,b,cin);

input a,b;

input cin;

output sum;

output cout;

reg sum;

reg cout;

always@(a or b or cin) begin

{cout,sum}=a+b+cin; //使用位拼接符号{},如果有进位就进位到out

end

endmodule

module ful_adder_tb ();

reg a,b,cin; //输入信号

wire sum,cout; //输出信号

ful_adder fa (cout,sum,a,b,cin);

initial

begin//这个其实就是真值表的应用

a = 1'b1; b = 1'b0; cin = 1'b1;

#73 a = 1'b1; b = 1'b1; cin = 1'b1;

#73 a = 1'b0; b = 1'b0; cin = 1'b1;

#73 a = 1'b0; b = 1'b1; cin = 1'b0;

#73 a = 1'b1; b = 1'b0; cin = 1'b1;

end

endmodule

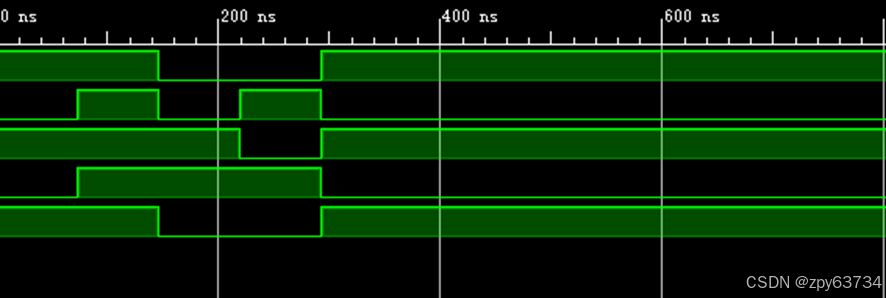

激励文件(注意可能需要改变延时时间为自己的学号)

reg a,b,cin; //输入信号

wire sum,cout; //输出信号

ful_adder fa (cout,sum,a,b,cin);

initial

begin//这个其实就是真值表的应用

a = 1'b1; b = 1'b0; cin = 1'b1;

#73 a = 1'b1; b = 1'b1; cin = 1'b1;

#73 a = 1'b0; b = 1'b0; cin = 1'b1;

#73 a = 1'b0; b = 1'b1; cin = 1'b0;

#73 a = 1'b1; b = 1'b0; cin = 1'b1;

end

endmodule