文章目录

前言

本文仅仅简单介绍了SR触发器、D触发器、J触发器、T触发器的使用。

简介

数字电子技术中的触发器是存储二进制信息的基本单元,广泛应用于时序电路设计。不同触发器类型在结构、功能和应用场景上各有特点。以下详细介绍常用触发器的工作原理、特性方程、逻辑结构及使用示例,并结合实际应用场景进行分析。

1. SR触发器(Set-Reset Flip-Flop)

工作原理

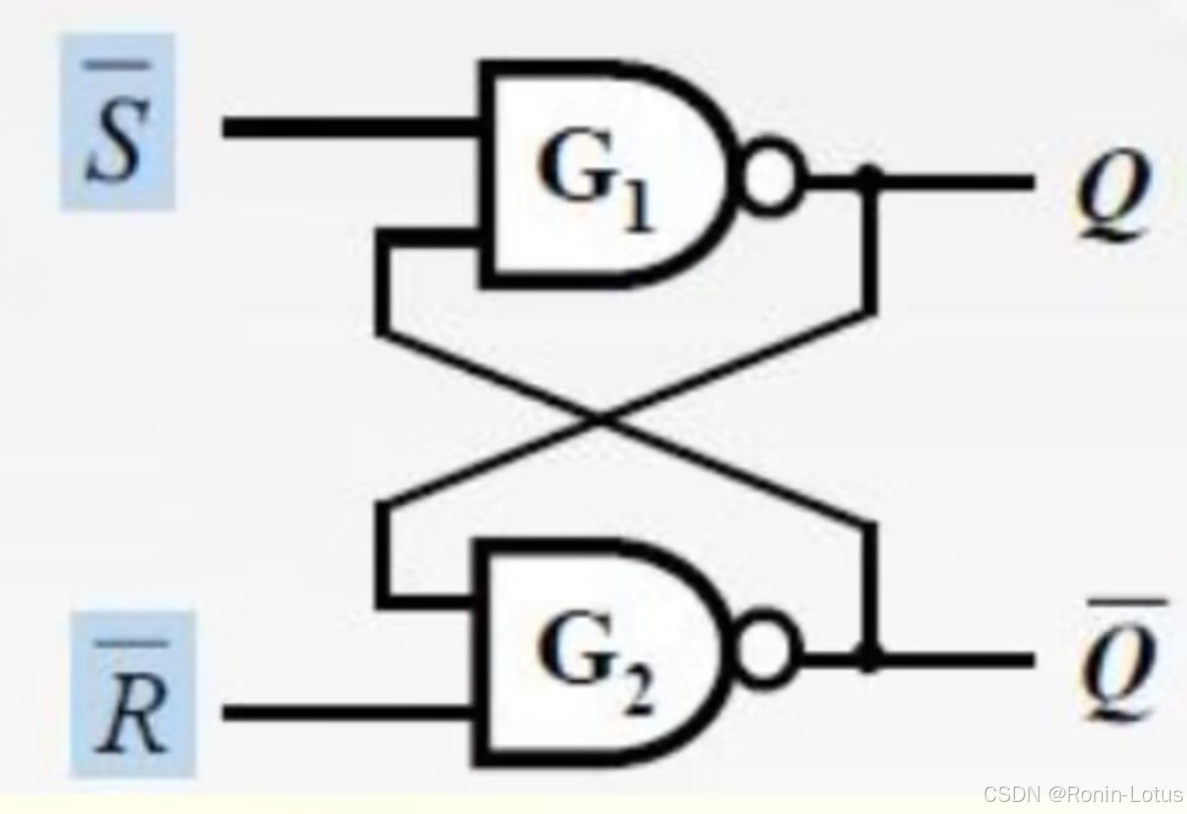

1.基本结构

基本结构:由两个交叉耦合的与非门(或或非门)构成,是最简单的锁存器(电平触发)。

2.输入信号

S(Set):置位端(高电平有效),使输出Q=1。

R(Reset):复位端(高电平有效),使输出Q=0。

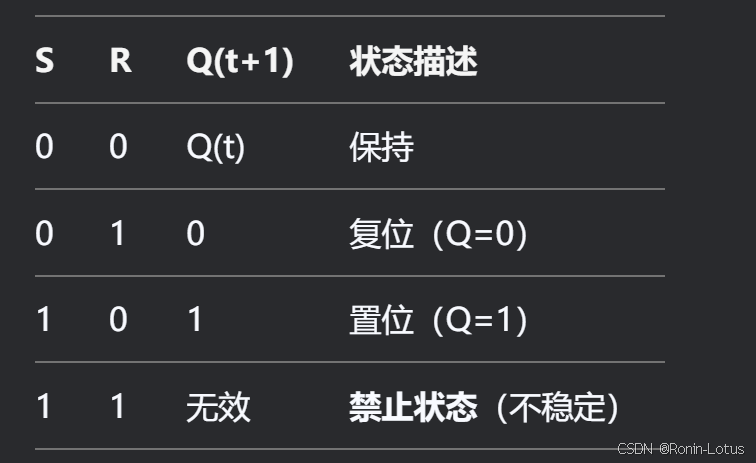

3.真值表

S R Q(t+1) 状态描述

0 0 Q(t) 保持

0 1 0 复位—>0

1 0 1 置位—>1

1 1 无效 禁止状态(不稳定)

4.缺点

缺点:存在禁止状态(S=R=1时输出不确定),需避免输入同时为高电平。

5.应用示例

按键消抖电路:利用SR锁存器消除机械开关的抖动信号。

当按键按下时,S=1、R=0 → Q=1;松开时,S=0、R=1 → Q=0,输出稳定。

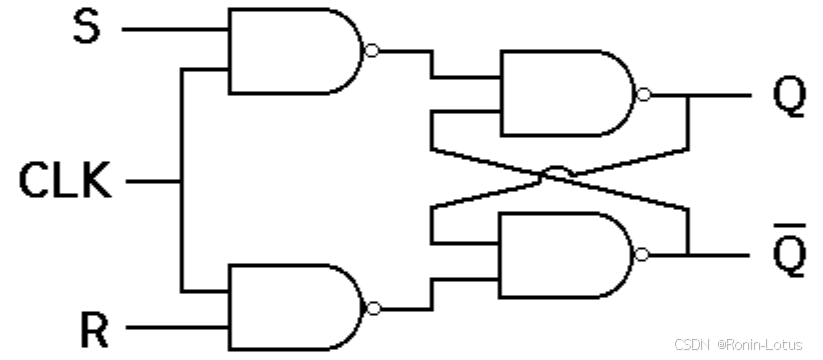

2. 钟控SR触发器(Clocked SR Flip-Flop)

工作原理

1.改进点

改进点:在基本SR触发器前增加时钟控制门(与门),由时钟信号(CLK)控制输入。

2.触发条件

触发条件:CLK=1时,输入S和R有效;CLK=0时保持状态。

3.问题

问题:电平触发可能导致“空翻”(多个状态变化),不适用于高速电路。

4.应用示例

简单状态机:用于CLK信号同步的简单控制逻辑,如电机启停控制。

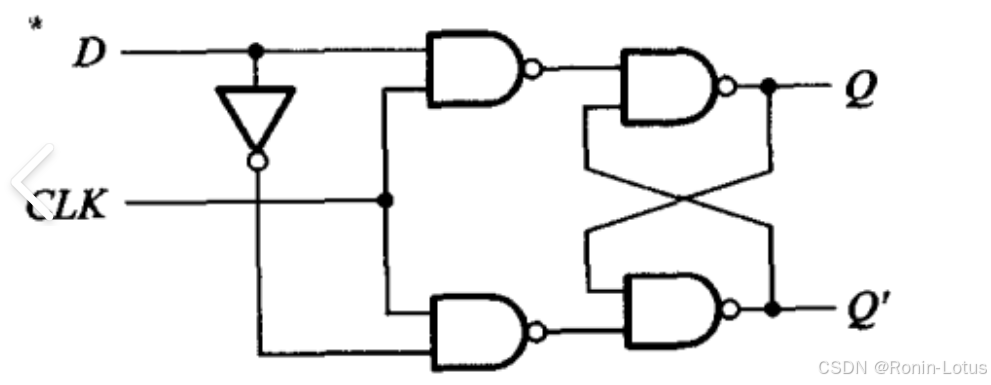

3. D触发器(Data Flip-Flop)

工作原理

1.结构改进

结构改进:通过将SR触发器的S和R端反向连接,避免禁止状态,仅需单个数据输入(D)。

2.功能

功能:CLK边沿(上升沿或下降沿)触发时,输出Q=D。

3.特征方程

特性方程:

𝑄(𝑡+1)=𝐷

4.触发方式

触发方式:边沿触发(抗空翻),常用主从结构或传输门实现。

5.应用示例

寄存器:存储多位数据。

// 4位D触发器寄存器

module reg_4bit (input clk, input [3:0] D, output reg [3:0] Q);

always @(posedge clk) Q <= D;

endmodule

移位寄存器:串行转并行数据转换。

// 右移寄存器(带串行输入)

module shift_reg (input clk, input sin, output reg [3:0] Q);

always @(posedge clk) Q <= {sin, Q[3:1]};

endmodule

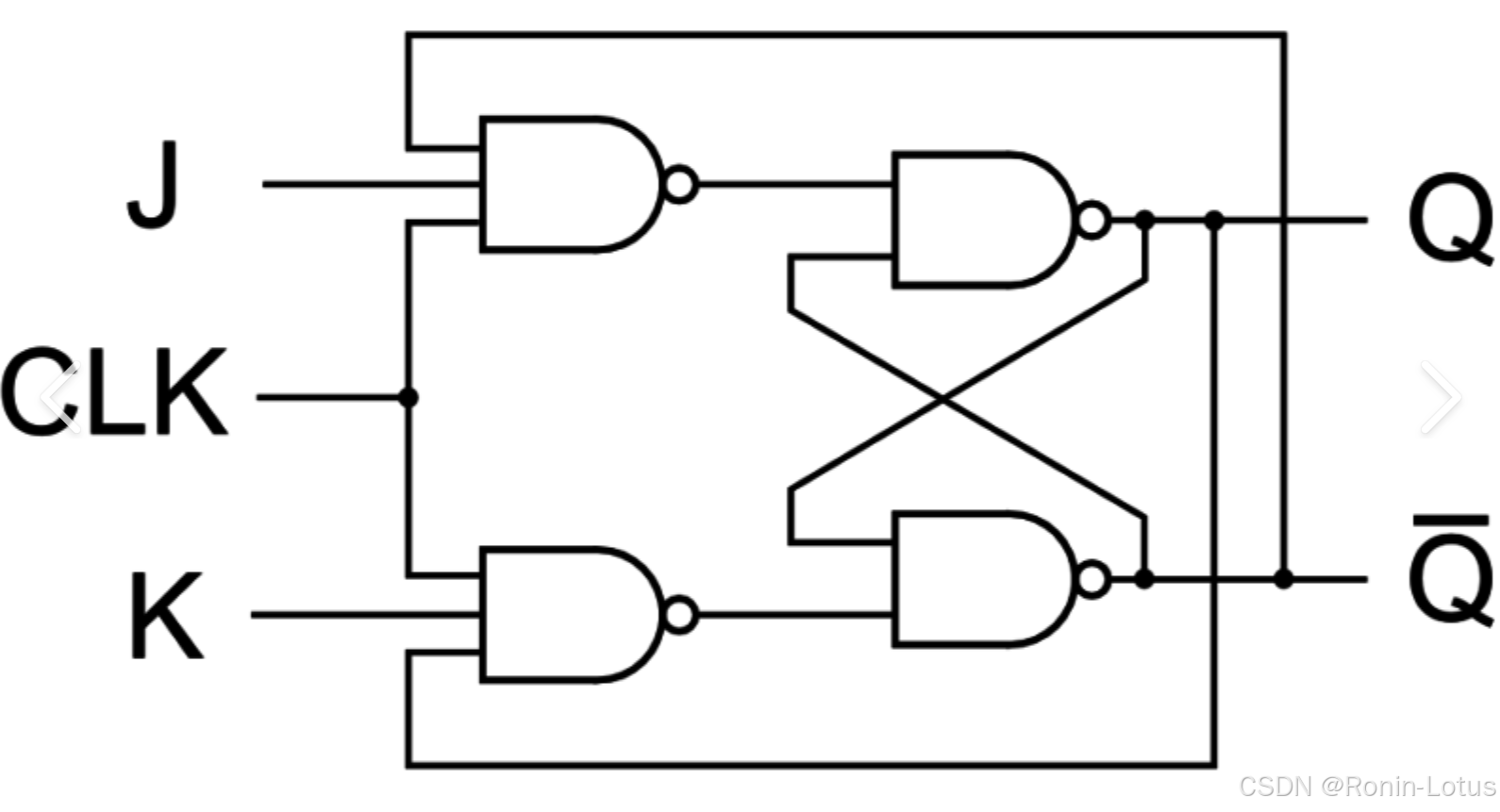

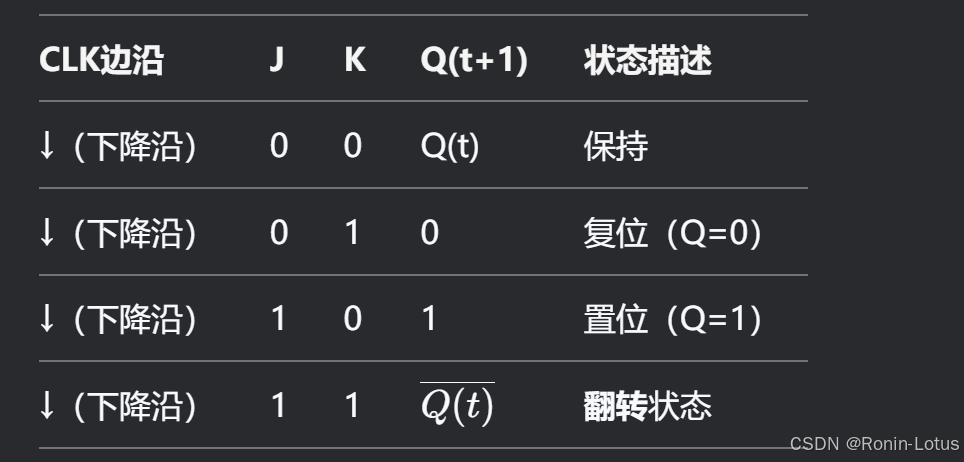

4. JK触发器(JK Flip-Flop)

工作原理

1.结构改进

结构改进:在SR触发器基础上增加反馈,解决禁止状态问题。

输入J(Set)和K(Reset),当J=K=1时,输出翻转(𝑄(𝑡+1)=𝑄(𝑡)‾Q(t+1)= Q(t))。

2.特征方程

特性方程:

𝑄(𝑡+1)=𝐽𝑄(𝑡)‾+𝐾‾𝑄(𝑡)

3.主从结构

主从结构:避免空翻,CLK高电平期间主触发器采样,CLK下降沿从触发器更新。

4.应用示例

计数器:实现二进制计数。

// 模4计数器(使用JK触发器)

module counter_mod4 (input clk, input rst, output reg [1:0] count);

always @(posedge clk or posedge rst) begin

if (rst) count <= 2'b00;

else count <= count + 1;

end

endmodule

状态机:实现复杂控制逻辑。

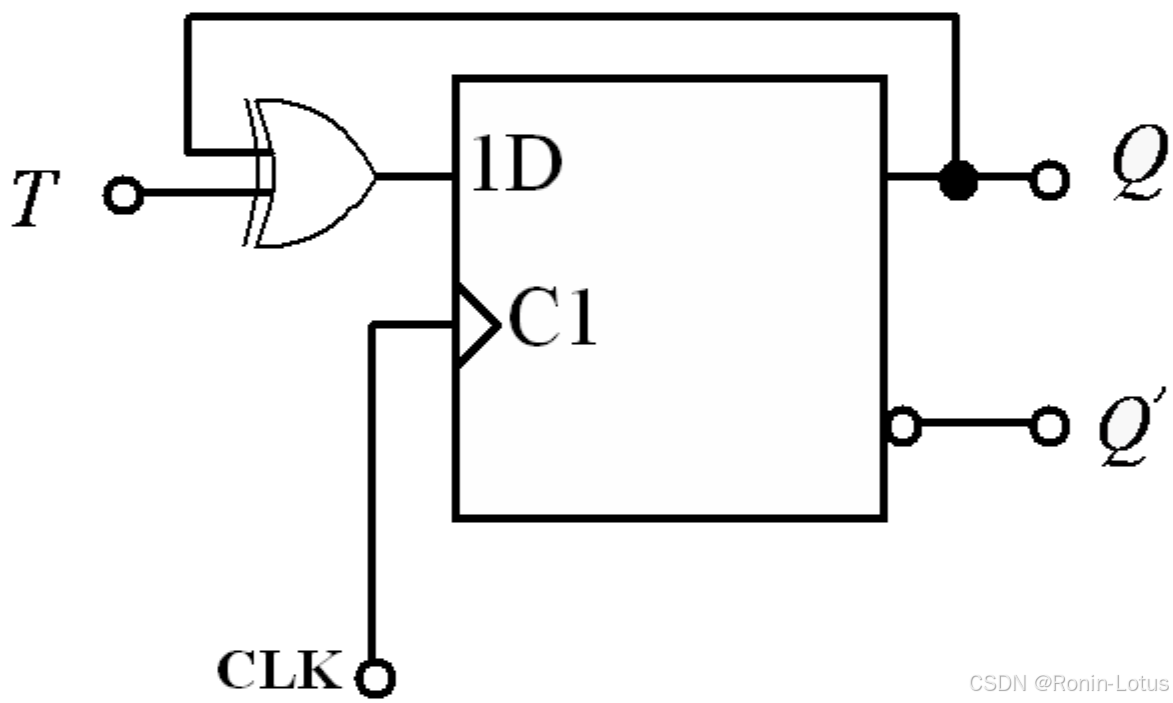

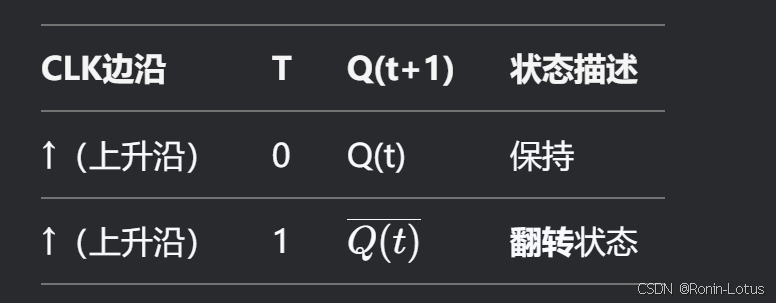

5. T触发器(Toggle Flip-Flop)

工作原理

1.简单版本

简化版本:将JK触发器的J和K端短接为T输入。

T=1时:输出翻转(𝑄(𝑡+1)=𝑄(𝑡)‾Q(t+1)= Q(t))。

T=0时:保持原状态。

2.特征方程

特性方程:𝑄(𝑡+1)=𝑇⊕𝑄(𝑡)

3.应用实例

应用示例

分频器:将时钟频率分频为1/2。

// 2分频电路

module clk_divider (input clk, output reg clk_out);

always @(posedge clk) clk_out <= ~clk_out;

endmodule

6. 集成触发器芯片示例

74LS74(双D触发器)

1.功能

功能:带异步复位(Reset)和置位(Set)的上升沿D触发器。

2.应用

应用:同步数据锁存、去抖动电路。

74LS112(双JK触发器)

1.功能

功能:带异步复位的下降沿JK触发器。

2.应用

应用:计数器、频率合成器。

7. 触发器选择与设计要点

触发方式:

1.边沿触发

- 边沿触发(D、JK)适用于高速电路。

- 电平触发(SR锁存器)用于简单控制。

2.功能需求

-

数据存储:选择D触发器。

-

状态翻转:选择JK或T触发器。

3.时序约束

**建立时间(Setup Time)和保持时间(Hold Time)**需满足。

总结

不同触发器在数字系统中承担不同角色:

1.SR锁存器

SR触发器:基础锁存器,适合消抖和简单控制。基础但需避免禁止状态。

2.D触发器

D触发器:简单可靠,适合数据存储和流水线设计。简单可靠,适合数据流水线。

3.JK触发器

JK触发器:功能灵活,适合计数器和状态机。功能全面,支持保持、置位、复位和翻转。

4.T触发器

T触发器:简化版JK触发器,适合分频和计数。专用于周期翻转场景(如分频器)

设计时需根据功能需求、时序约束和电路复杂度综合选择,并通过仿真验证时序正确性。例如,在FPGA中,D触发器是主流选择;而在ASIC中,可能根据功耗和面积优化选择触发器类型。

总结

以上就是今天要讲的内容,本文仅仅简单介绍了SR触发器、D触发器、J触发器、T触发器的使用。