上回书说到数电中的两种基本存储电路——锁存器和触发器以及时序逻辑电路的设计和分析。今天来看看触发器的几个应用,主要实践实践,不能只说概念。

首先,首当其冲的就是计数器,如果大家看过我之前记的笔记的话,应该不会陌生,不管是STM32中的中断处理器的应用还是STC15的PCA捕获模块都离不开它的身影,基本上都是通过利用触发器在脉冲边沿作用下的状态进行刷新的特性。计数器是一个用以实现计数功能的时序器件。它不仅可用来计脉冲数,还常用作数字系统的定时、分频和执行数字运算以及其它特定的逻辑功能。在各种类型的数字仪表、检测设备及其它数字系统中都是不可缺少的组成部分。

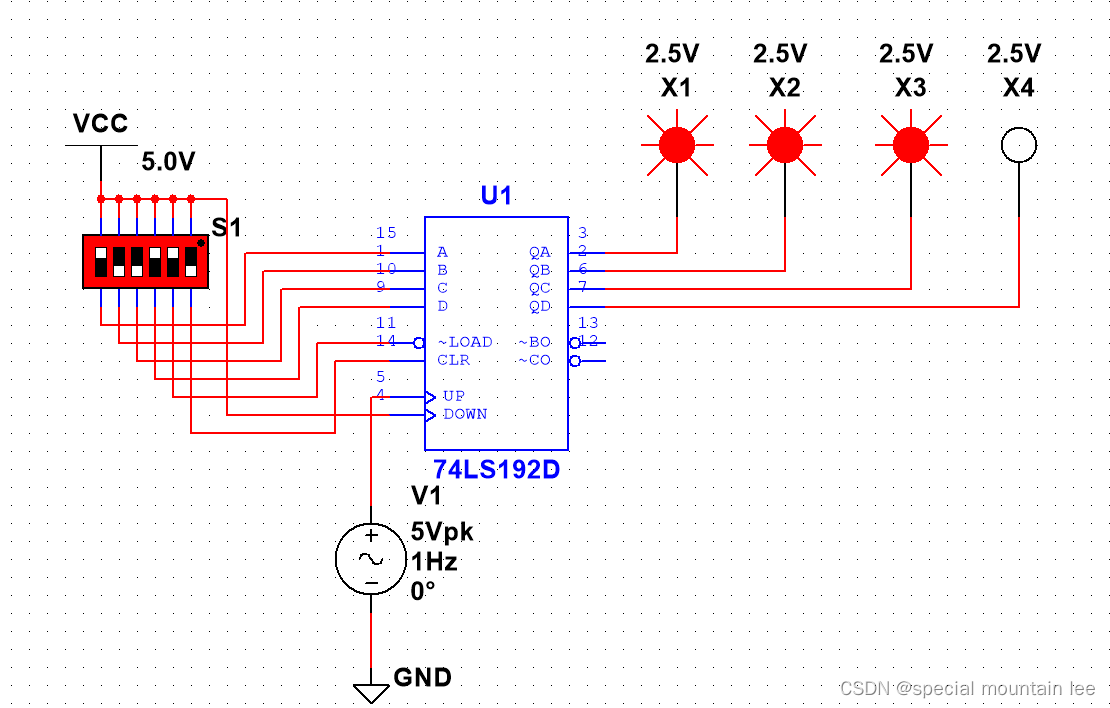

先来看看第一个例子,利用74LS192十进制可加计数。Multisim的电路图如下。

这个电路主要实现的就是十进制的加法计数,如果实现减法计数,大家UP和DOWN上的电平换就行了,UP上加上高电平,DOWN下加上脉冲。这里要注意的是几个引脚的定义。LOAD(并行置数端) 引脚通常用于加载或设置触发器或寄存器的状态。当 LOAD 引脚接收到有效信号时,触发器或寄存器将根据输入的数据进行状态更新。具体的操作方式取决于具体的电路设计。CLR(清零端) 引脚通常用于清零或复位触发器或寄存器的状态。当 CLR 引脚接收到有效信号时,触发器或寄存器的输出将被强制设置为零或初始状态。

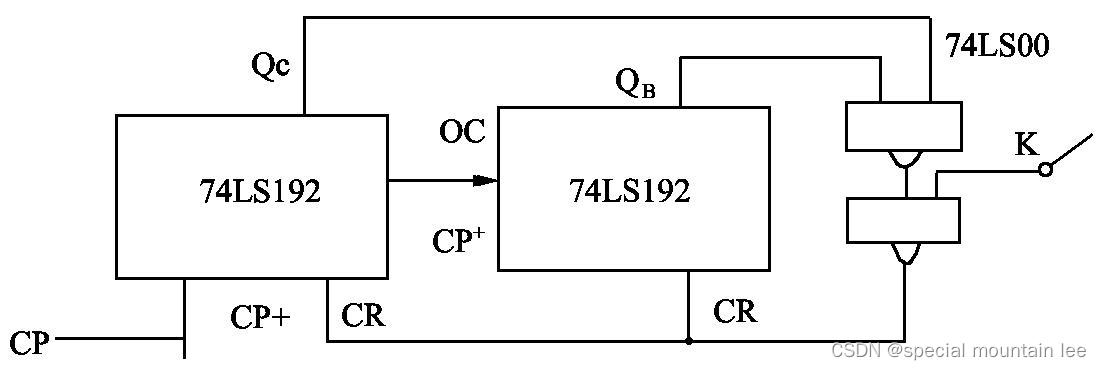

第二个例子较为复杂点实现二十四进制可加计数,就跟咱们通常用的时钟表差不多。先来看看原理图。

我的Multisim的图像也是根据这个原理图慢慢画出来的。可以先根据它画画。下面是我较为丑陋的Multisim电路图。

大家凑合看看吧。与之前的十进制差不多,这里只是通过级联把两个芯片在一块儿。

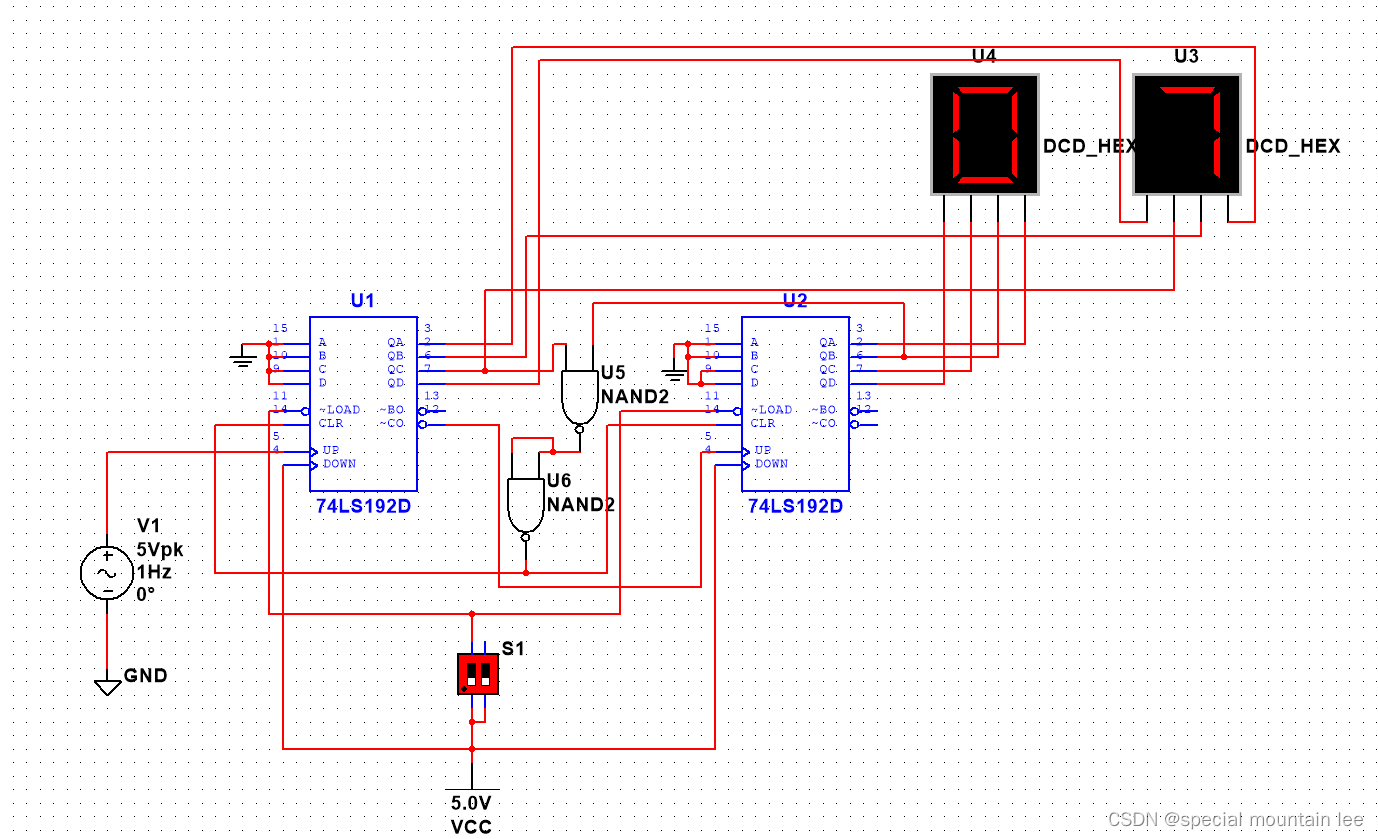

最后一个例子是用555定时器构成单稳态触发器,多谐振荡器和施密特触发器。原理框图如下图。

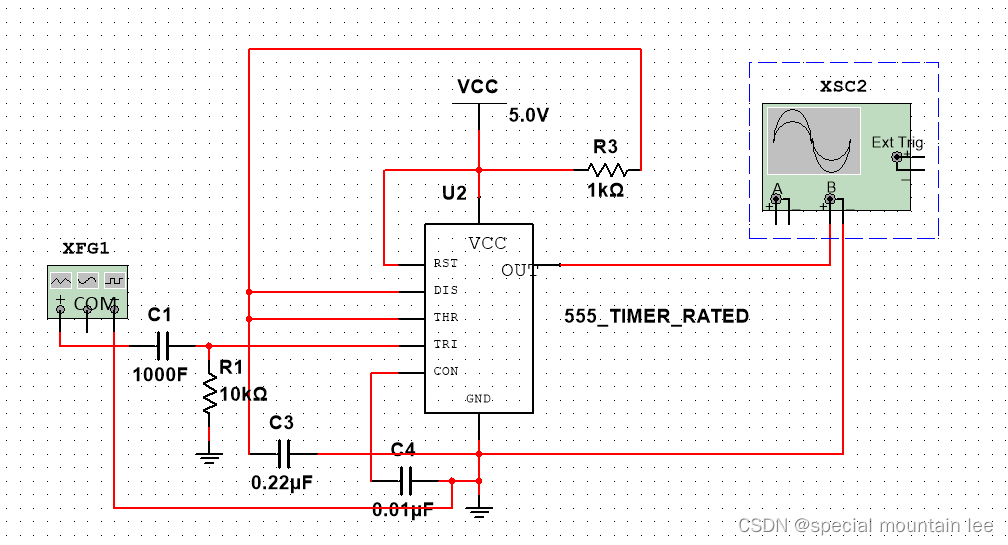

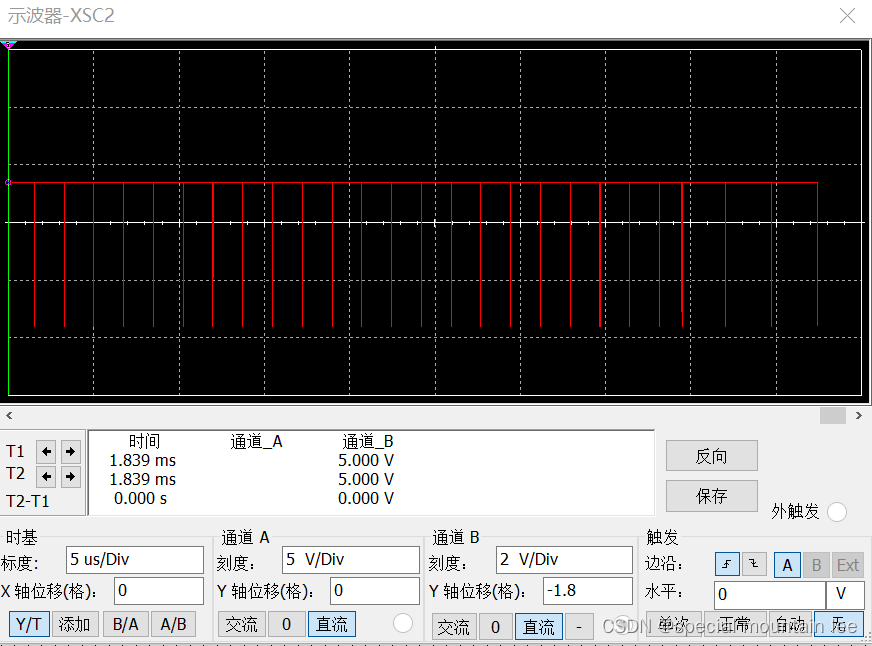

首先来看看单稳态触发器。单稳态触发器是一种具有一个稳定状态和一个暂稳态的脉冲整形电路。在没有触发信号输入时,电路处于稳定状态。当接收到一个触发脉冲后,电路会从稳定状态进入暂稳态,并在经过一段特定的时间后,自动返回到稳定状态。暂稳态的持续时间取决于电路中的电阻和电容等元件的参数值。输出脉冲宽度为RCln3。电路图如下。

波形图如下。

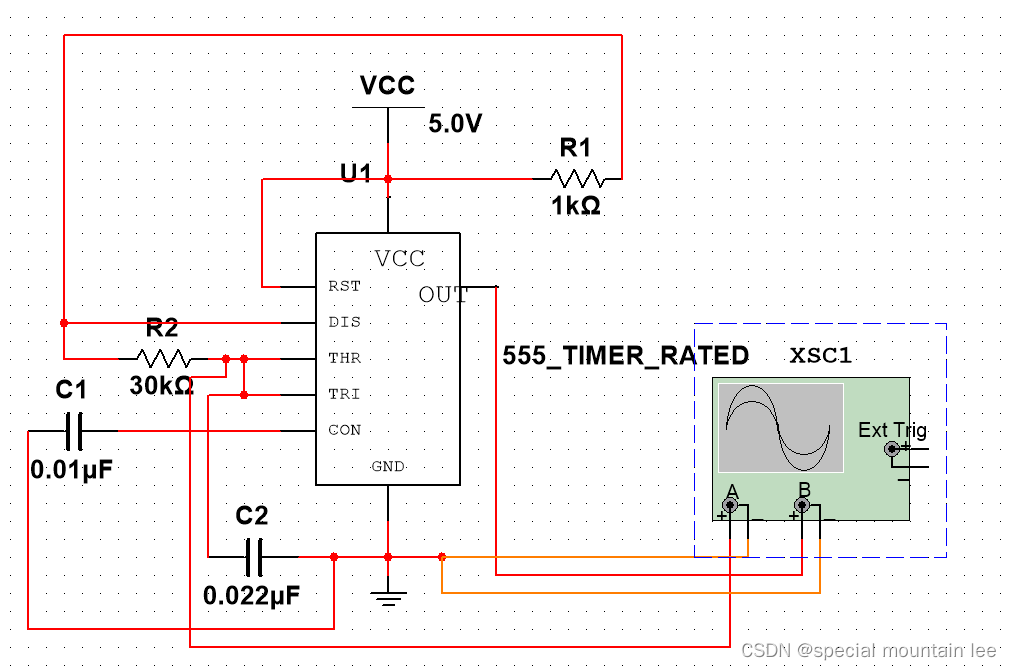

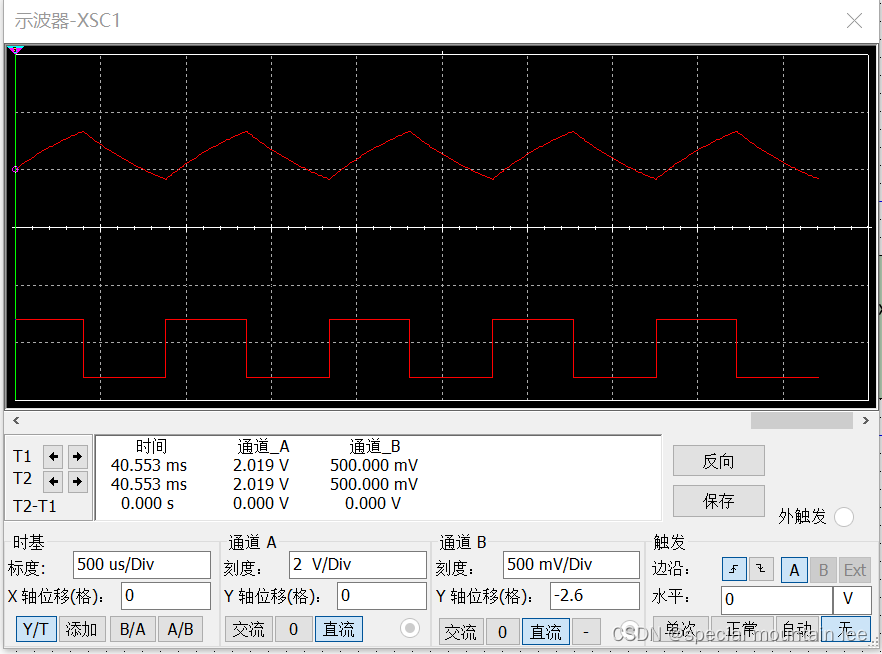

接下来是多谐振荡器。多谐振荡器是一种能够产生矩形波的自激振荡器。它不需要外部输入信号,就能自行产生一定频率和一定占空比的矩形脉冲波。多谐振荡器输出的矩形波的频率和占空比由电路中的电阻、电容等元件参数决定。按照上述的原理图,振荡周期T=(R1+2R2)*Cln2。T充=(R1+R2)*Cln2。占空比p=(R1+R2)/(R1+2R2)。电路图如下。

波形图如下。

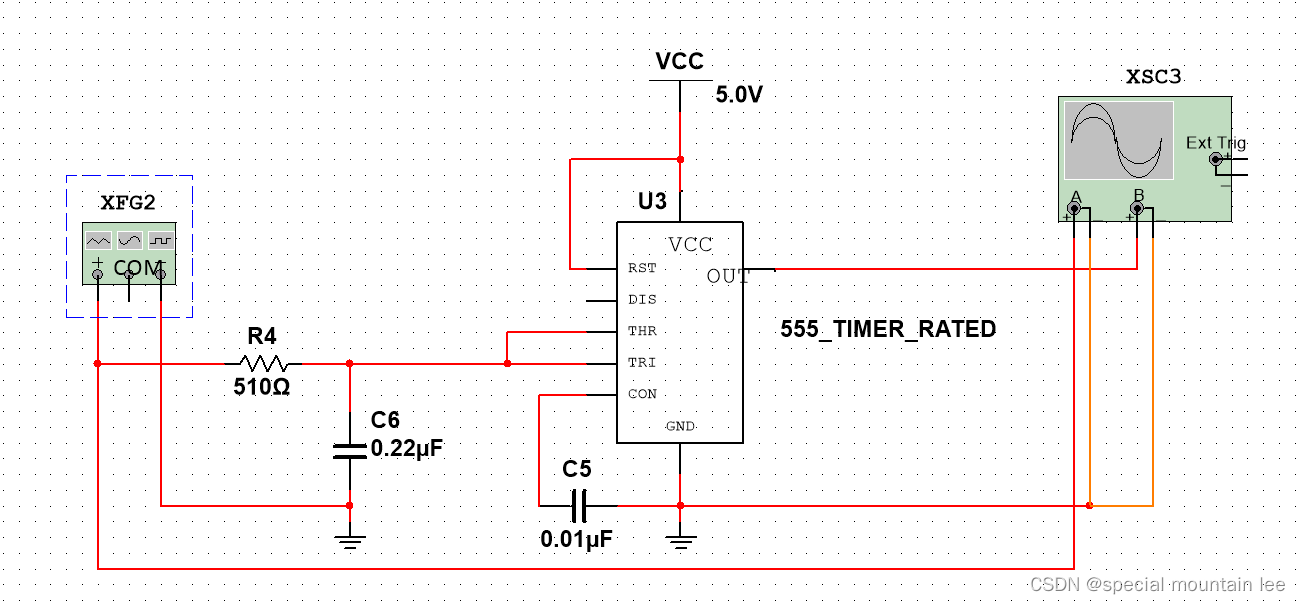

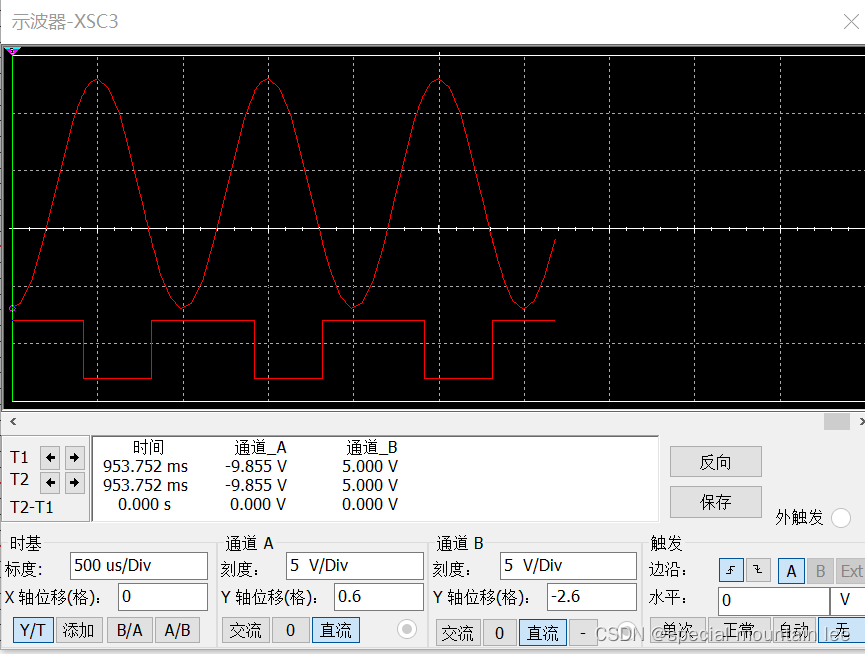

最后是施密特触发器。施密特触发器是一种特殊的双稳态触发器,具有滞回特性。它有两个阈值电压,分别称为正向阈值电压和负向阈值电压。当输入信号从低电平逐渐上升并超过正向阈值电压时,输出状态发生翻转;而当输入信号从高电平逐渐下降并低于负向阈值电压时,输出状态再次翻转。这种特性使得施密特触发器对于缓慢变化的输入信号具有良好的整形作用,能够将缓慢变化的输入信号。上触发电压VT+=2/3*Vcc。下触发电压VT-=1、3*Vcc。电路图如下。

波形图如下。

今天的讲完了,明天再看看一些数电的小东西。

欲知后事如何,且听下回分解。OVO........