Standard EVB硬件开发指南

一、LCD接口电路详解

Standard EVB具备6.8寸和7寸MIPI接口电路,系统中的MIPI接口与LVDS接口可以兼容,但FPC接口引脚定义不能兼容所有屏幕,所以针对9寸或者10.1寸的液晶屏,需要按照液晶屏接口要求更改VCOM、VGH、VGL、AVDD、VLED等电压值。

以下将针对EVB电路板中的电源电压进行调整。

1、VLED背光驱动电路

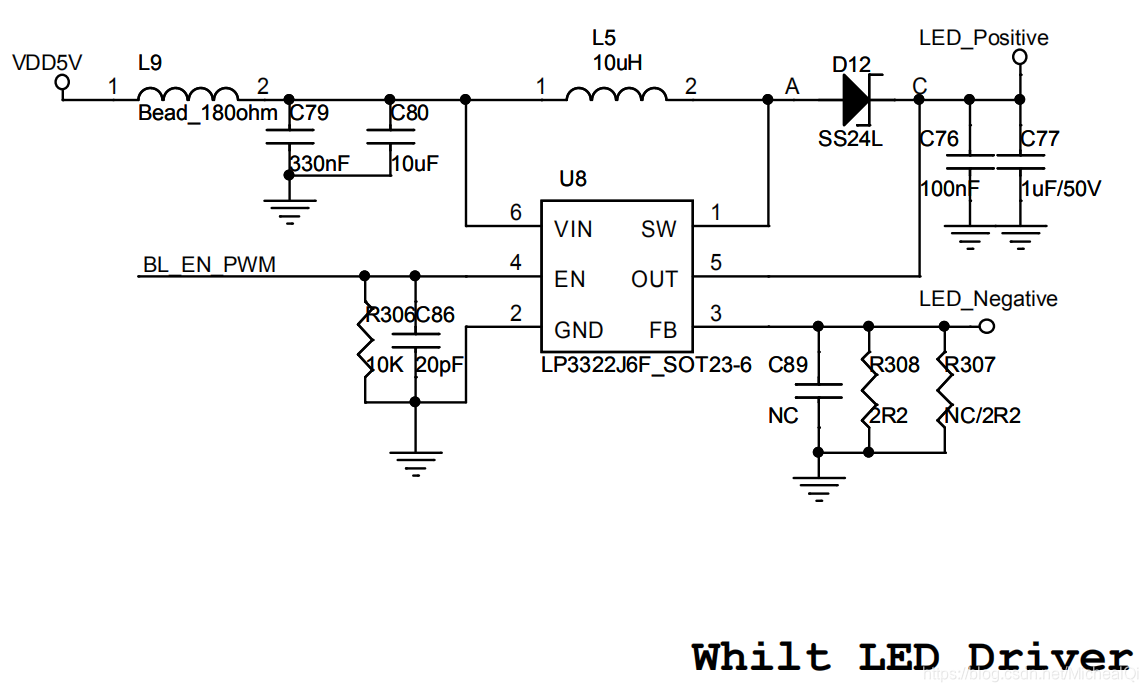

EVB开发板采用的LED背光驱动电路如下:

LED_Positive需要连接到液晶屏幕上的 LED+;

LED_Negative需要连接到液晶屏幕上的 LED-;

依据Backlight的驱动电流值,该电路可以满足9寸和10.1寸屏幕的背光需求。

LED恒流驱动IC:LP3322是微源半导体推出的一款10 LED驱动器,驱动电路参考电压分为200mV【LP3322】和300mV【LP3322A】两种,输入电压范围宽可用电压值为2.7V~6V,输出电压可以达到36V,完全可以满足所有LCD背光驱动。

一般针对LCD显示屏背光驱动电路中,需要根据参考电压与LED串联的电阻值来限定驱动电流。例如原理图中的R308 = 2.2Ω,FB的参考电压值为200mV,则LED驱动电路中的电流值 ILED = 0.2V / 2.2Ω = 90mA。

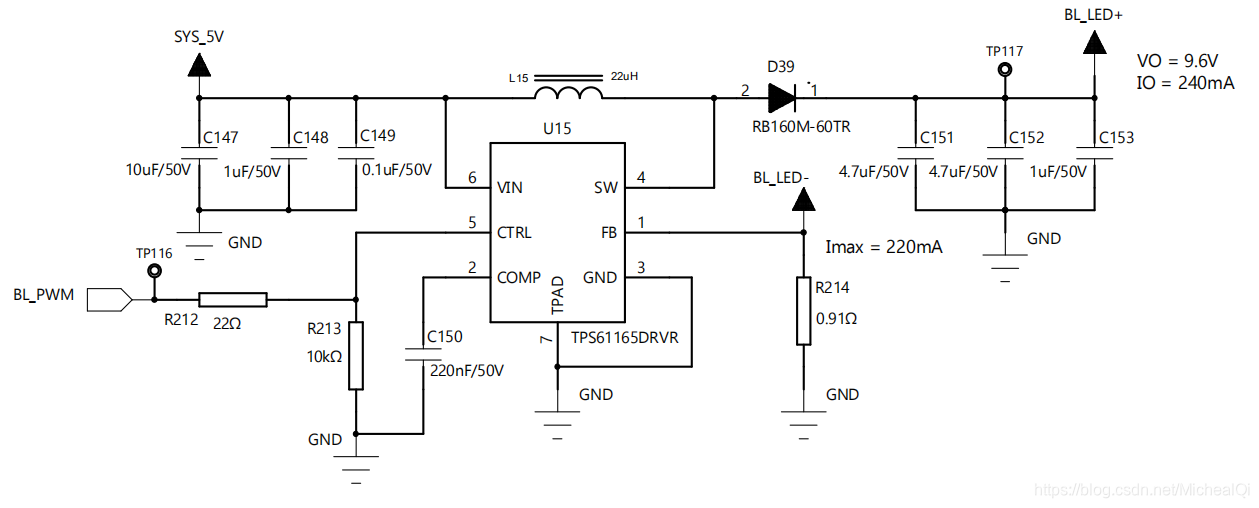

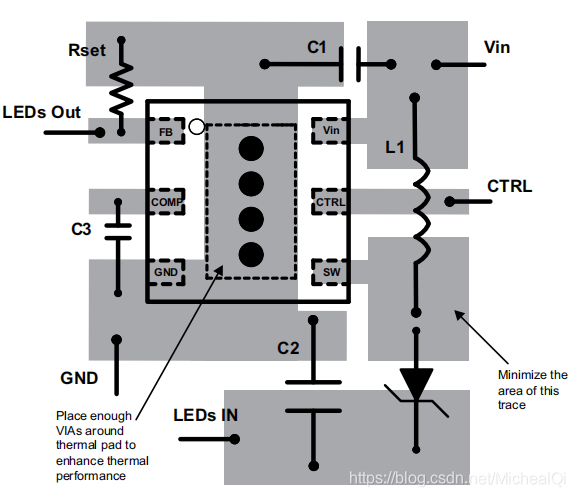

其他厂商利用的LED背光驱动电路参考:

该电路采用TPS61165进行LED背光驱动,输入电压范围3V~18V,输出电压最高38V,参考电压值固定200mV,最大驱动电流1.2A。

关于限流电阻的选择需要依据Backlight的电流值限定。

在进行背光驱动电路设计时,一定要注意背光调试PWM使能引脚,该引脚必须接在GPIO端口上(PWM输出功能),且上电默认应该是低电平模式。待系统上电稳定后,再开启PWM输出功能,否则背光可能会出现频闪问题,甚至损坏相关元器件。

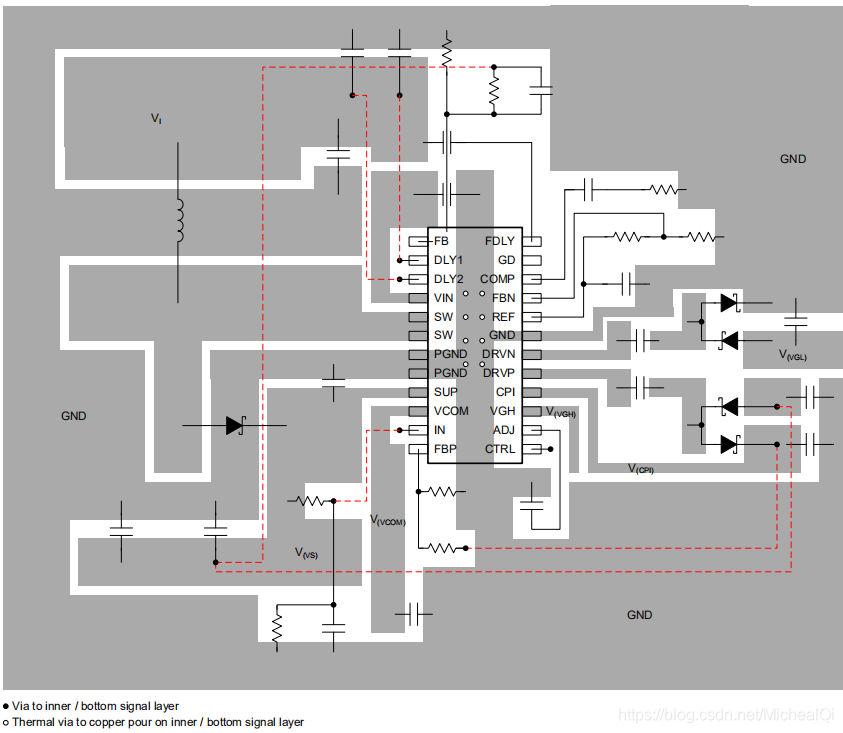

2、LCD多电源管理器(VCOM、VGH、VGL、AVDD)

由于TFT LCD也称为薄膜场效应开关管显示屏,需要利用VGH、VGL点亮像素点,同时驱动电源中也有VCOM、AVDD两种其他功能的电源接口。

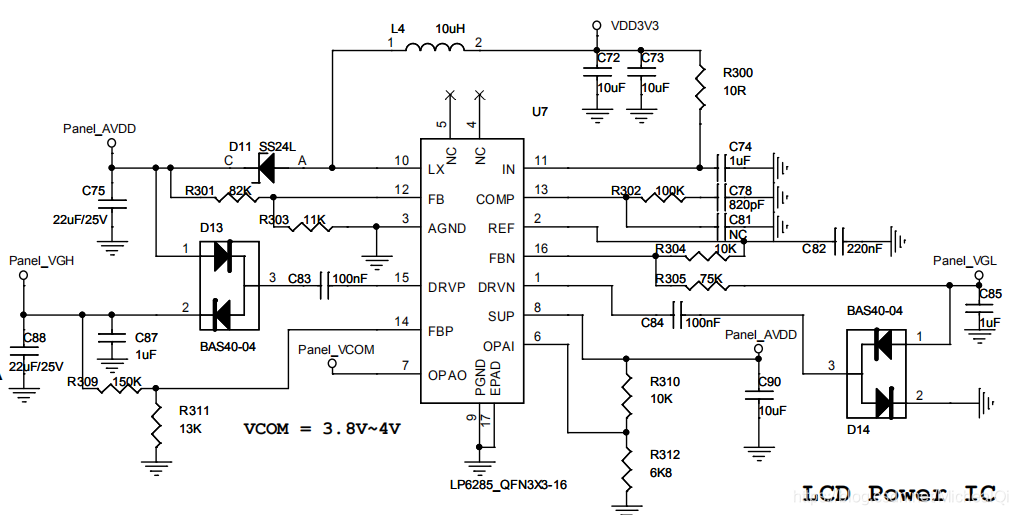

EVB开发板提供的LCD Power多电源电路包括Panel_AVDD、Panel_VCOM、Panel_VGH、Panel_VGL。

这些电源电压需要匹配对应的LCD接口电压,所以就目前的9寸和10.1寸显示屏,这些端口的电压都需要进行更改。

FB、FBP、FBN、REF的参考电压典型值为1.2V

Panel_AVDD =(VFB / R303) x (R303+R301) = 1.2 x (1+R301/R303) = 1.2 x 8.45 = 10.14V;

Panel_VCOM =(VAVDD / (R312+R310)) x R312 = (10.14 / 16.8) x 6.8 = 4.1V;

Panel_VGH=(VFBP / R311) x (R309+R311) = 1.2 x (1+R309/R311) = 1.2 x 12.5 = 15V;

Panel_VGL= - ((VREF -VFBN )/ R304) x R305 = - (1.2-0.27) x R305/R304 = -0.93 x 7.5 = -6.95V;

当需要更换或者使用9寸和10.1寸显示屏时,将以上电阻值按照电压值匹配规则,产生显示屏对应引脚电压即可。

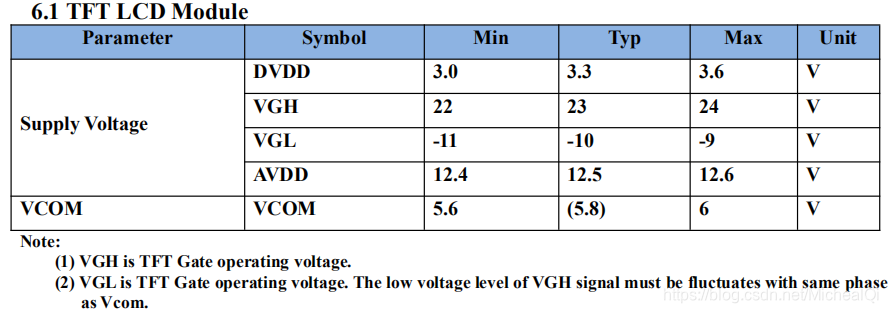

其中9寸显示屏电源电压值说明:(显示屏型号-TYW090HLJ2019-AA1)

按照上述电路进行电阻取值,进而满足设备使用要求

AVDD = 1.2 x (1+R301/R303) = 1.2 x (1+100/11)= 12.1V;所以R301 = 100KΩ。

VCOM = (12.1 x R312) / (R312+R310) = (12.1 x 6.8) / (6.8+8) = 5.6V;所以R310 = 8KΩ。

VGH = 1.2 x (1+R309/R311)= 1.2 x (1 + 100/5.6)= 23.3V;所以R311 = 5.6KΩ,R309 =100KΩ 。

VGL = - 1.2 x (R305/R304)= -(1.2-0.27) x (100/10)= -9.3V;所以R305 = 100KΩ。

3、MIPI、LVDS接口定义

Standard EVB电路板提供MIPI接口,但IT986x提供MIPI接口的同时也定义了LVDS接口,且MIPI与LVDS接口对应,都是高速差分信号线。

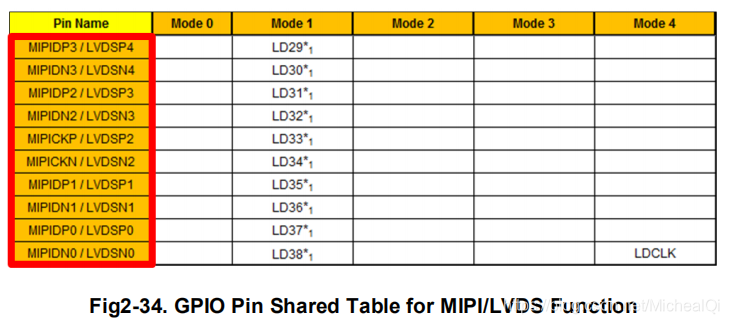

在进行PCB走线设计时,需要注意LVDS I/F 在 IT986x SoC 的 Shared GPIO Pin Table 与 MIPI 信号共用 PIN脚。芯片端口上的Pin Define为硬件设计时的命名规定,实际上具备可调整性,包含整组信号中的P/N均可互换。因为LVDS信号属于差分高速信号线,PCB设计时需要进行阻抗匹配,所以调换时必须整组信号调换,不能拆分。差分对彼此间需要包地进行屏蔽,差分线间需要阻抗匹配到100Ω,布线间距满足3W原则。这样既可以增加器件布局的空间,也会降低与屏幕有关的EMI干扰等。

4、LVDS显示控制接口

RESET、STBYB

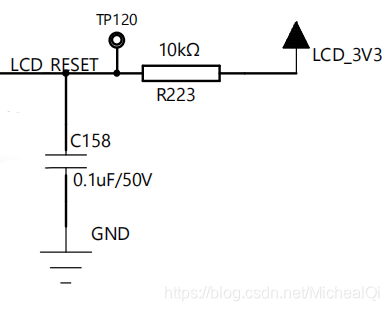

RESET 显示屏控制重置引脚,"0"表示进入复位重置状态。

建议与控制器RC复位电路连接在一起,以便获得稳定性。或者直接连接低电平硬件复位电路进行上电自动复位,如果I/O引脚富余可以连接至I/O端口进行复位实时控制。

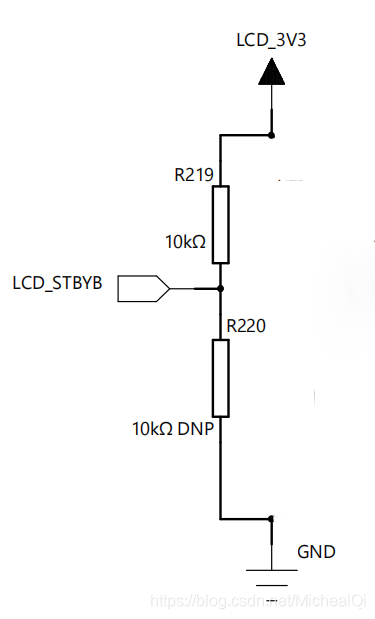

STBYB 工作模式选择引脚,"0"表示待机模式(驱动器输出为HighZ,定时器关闭),"1"表示正常工作模式。默认使用上拉电路形式或I/O端口控制形式。

SELB

SELB 6bit/8bit模式选择引脚,"0"表示LVDS输入的数据是8bit数据,"1"表示LVDS输入的数据是6bit数据。电路设计时采用短接电阻进行选择。

U/D、L/R

U/D、L/R 这两组引脚主要控制显示屏的旋转显示方向。如果I/O端口富余,可以利用I/O端口进行屏幕方向的旋转。

当L/R=”0”表示从右向左扫描;L/R=”1”表示从左向右扫描。

当U/D=”0”表示从上到下扫描;U/D=”1”表示从下到上扫描。

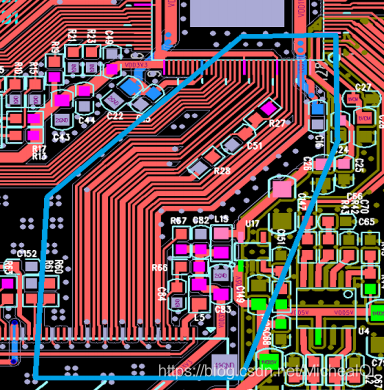

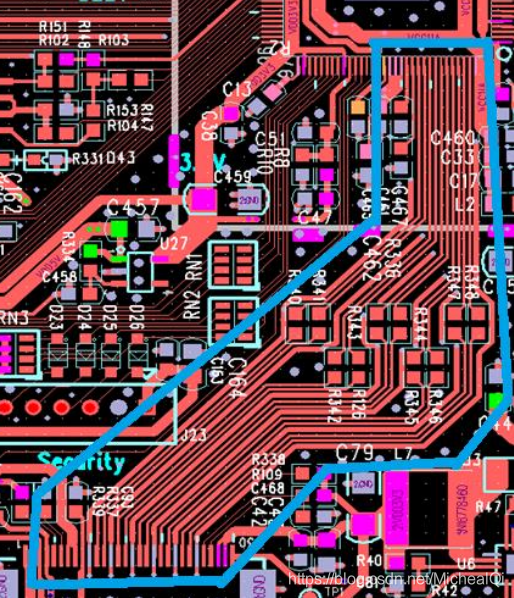

5、LCD Layout设计要求

VLED BackLight Power

对于所有的开关电源(Switching Power),特别是高开关频率(>500KHz)或大电流(>1A)的开关电源芯片,外部电路元器件的布局是一个重要的设计步骤。如果没有仔细进行布置,开关电源调节器可能会出现不稳定和噪音问题。所以无论是我们目前使用的BackLight Power还是其他Switching Power都需要注意以下相关问题。

1、为了减少开关造成的损耗,尽可能使SW引脚的升降时间变短。

2、为了防止高频共振问题的辐射,正确布局高频切换路径至关重要。

3、最小化所有连接到SW的走线长度和面积,并始终在开关调节器下使用一个地平面来最小化平面间耦合。

4、包括PWM开关、肖特基二极管和输出电容器等回路,以及在ns内的高电流上升和下降,必须保持尽可能短。

5、输入电容器必须同时靠近VIN针脚和GND针脚,以减少设备电源纹波。

LCD Bias Power

LCD多电源管理器也是TFT显示的偏执电源,在Layout设计过程中,偏执电源的PCB布局是一个重要的步骤。不正确的布局可能会导致电源转换器不稳定、负载调节问题、噪声和电磁干扰问题。特别是在高负载电流下的DC-DC开关转换器,过薄的PCB铜层会导致显著的电压峰值,而良好的接地条件也是至关重要的。

1、建议使用一个公共地平面来尽量减少模拟地面(GND)和电源接地(PGND)之间的地面位移。

2、升压转换器输出电容器、输入电容器和电源接地(PGND)应形成星形接地,或应直接连接在公共电源地面上。

3、将输入电容器直接从输入引脚(VIN)处放置,并就近接地。

4、使用尽量粗的PCB走线,将SUP连接到输出Vs。

5、放置一个小的从SUP引脚到接地的旁路电容器。

6、对VGH和VGL的电荷泵驱动引脚(DRVN、DRVP)使用短走线路径的方式,因为这些走线携带着开关电流,所以长度尽量短。

7、将电荷泵飞跨电容器尽可能靠近DRVP和DRVN引脚,避免这些引脚上出现高压峰值。

8、将肖特基二极管尽可能靠近设备和连接到DRVP和DRVN的飞跨电容器上,避免高频噪声或干扰的产生。

9、小心地排列电荷泵的路径,以避免干扰其他电路,因为它们携带高压开关电流。

10、将VCOM缓冲器的输出电容器尽可能靠近输出引脚(VCOM)。

11、热焊盘必须焊接到PCB上,以获得良好的的热效能。

LCD Data Port For MIPI/LVDS

1、LVDS信号线

LVDS 属于高速差分信号线,在Layout布线过程中需要做到阻抗匹配,匹配值为100Ω。

LVDS差分对之间必须有GND Shielding进行数据保护和屏蔽,通常包地处理是抗干扰处理中非常常见的一种手段。Altium Designer提供了包地功能,具体方法参照 Altium Designer如何进行包地处理.

LVDS引脚在CPU引脚上是彼此相邻的,无法做到引脚引出位置的包地,所以在引脚附近应该尽量保证每组差分信号间的间隔最大(最小保证3W间隔)。

2、MIPI信号线

MIPI属于高速差分信号线,在Layout布线过程中需要做到阻抗匹配,匹配值为100Ω。

MIPI差分对之间必须有GND Shielding进行数据保护和屏蔽,通常包地处理是抗干扰处理中非常常见的一种手段。

MIPI引脚在CPU引脚上是彼此相邻的,无法做到引脚引出位置的包地,所以在引脚附近应该尽量保证每组差分信号间的间隔最大(最小保证3W间隔)。