案例展示

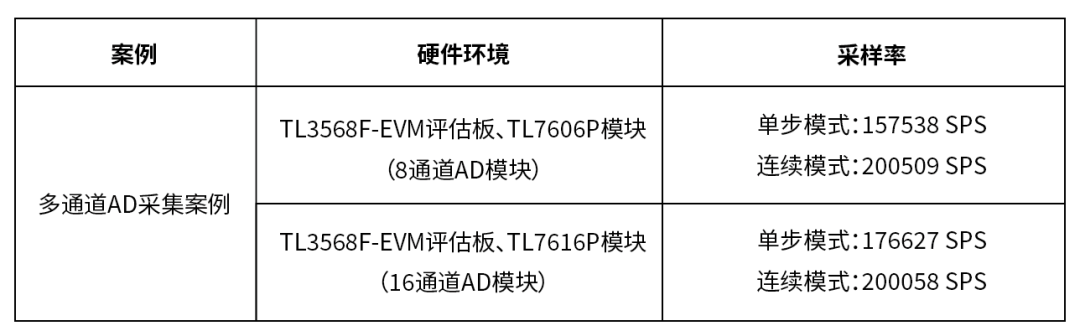

测试数据汇总

表 1

本文带来的是基于瑞芯微RK3568J + 紫光同创Logos-2的ARM + FPGA多通道AD采集处理与显示案例。本次案例演示的开发环境如下:Windows开发环境:Windows 7 64bit、Windows 10 64bitLinux开发环境:Ubuntu18.04.4 64bit虚拟机:VMware15.5.5U-Boot:U-Boot-2017.09Kernel:Linux-4.19.232、Linux-RT-4.19.232LinuxSDK:LinuxSDK-[版本号](基于rk356x_linux_release_v1.3.1_20221120)AMP SDK:rk356x_amp_sdk_release_v1.2.3_20230515硬件开发环境:创龙科技TL3568F-EVM评估板(瑞芯微RK3568J + 紫光同创Logos-2)、TL7606P模块、TL7616P模块。

RK3568J + FPGA全国产平台介绍

创龙科技TL3568F-EVM是一款基于瑞芯微RK3568J/RK3568B2四核ARM Cortex-A55处理器 + 紫光同创Logos-2 PG2L50H/PG2L100H FPGA设计的异构多核国产工业评估板,由核心板和评估底板组成,ARM Cortex-A55处理单元主频高达1.8GHz/2.0GHz。核心板ARM、FPGA、ROM、RAM、电源、晶振、连接器等所有元器件均采用国产工业级方案,国产化率100%。

核心板内部RK3568J/RK3568B2与Logos-2通过PCIe 2.0、FSPI、I2C、GPIO连接,并通过工业级B2B连接器引出PCIe 2.1、SATA、GMAC、USB、HDMI、LVDS、RGB、MIPI DSI、SDIO、CAN、SPI、UART等接口及FPGA IO引脚。ARM端支持多屏异显、Mali-G52-2EE GPU、1080P@60fps H.265/H.264视频编码、4K@60fps H.265/H.264视频解码,并内置1TOPS算力NPU。核心板经过专业的PCB Layout和高低温测试验证,质量稳定可靠,可满足各种工业应用环境要求。

RK3568J + FPGA典型应用领域

RK3568J + FPGA应用场景十分广泛,涵盖小电流选线、继电保护测试仪、运动控制器、医疗内窥镜、血液分析仪、目标识别跟踪等领域,可满足多种工业应用要求。

图 1 RK3568J + FPGA典型应用场景

多通道AD采集案例演示

本章节主要介绍多通道AD采集案例演示,为了简化描述,正文仅摘录案例功能描述与测试结果,详细产品资料请扫描文末二维码下载。

案例说明

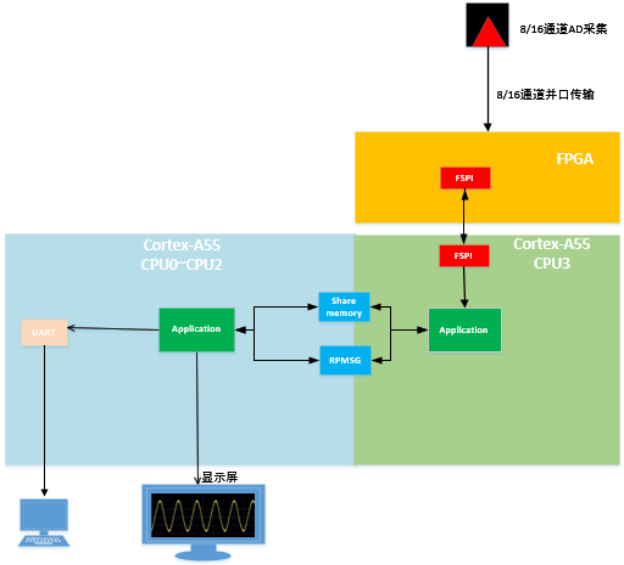

案例功能:案例基于FPGA端采集8/16通道AD数据,ARM端CPU3核心运行RT-Thread(RTOS)程序,并通过FSPI总线从FPGA端接收AD数据。ARM端CPU0、CPU1、CPU2核心运行Linux系统,CUP3核心(运行RT-Thread(RTOS)程序)通过rpmsg将AD数据发送至Linux应用程序,Linux应用程序通过rpmsg接收RT-Thread(RTOS)发送的AD数据,并将数据转换得到电压值,然后通过Qt显示波形至显示屏。

备注:

本案例目前仅支持在CPU3核心运行RT-Thread(RTOS)程序。

系统工作示意框图如下所示。

图 2 系统工作示意框图

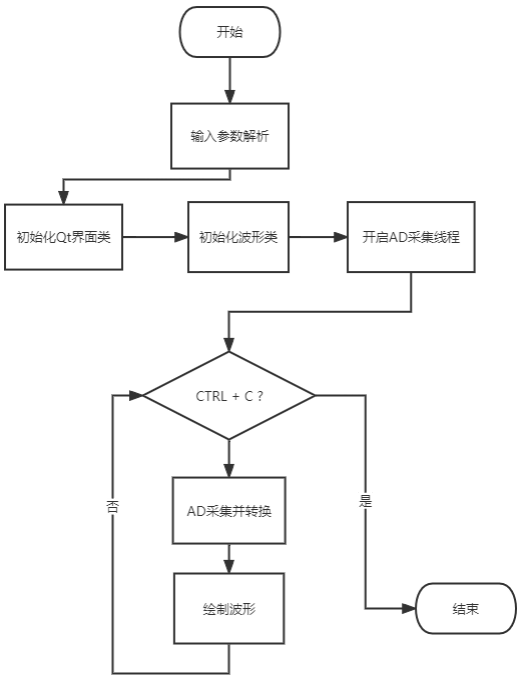

AD采集数据通过rpmsg传输流程图如下所示。

图 3 rpmsg传输流程图

案例支持如下2种模式:(1)单步模式:程序采集1024个数据后,显示静态波形。(2)连续模式:程序将会连续采集数据,并实时显示动态波形。

程序流程如下图所示。

图 4 程序流程图

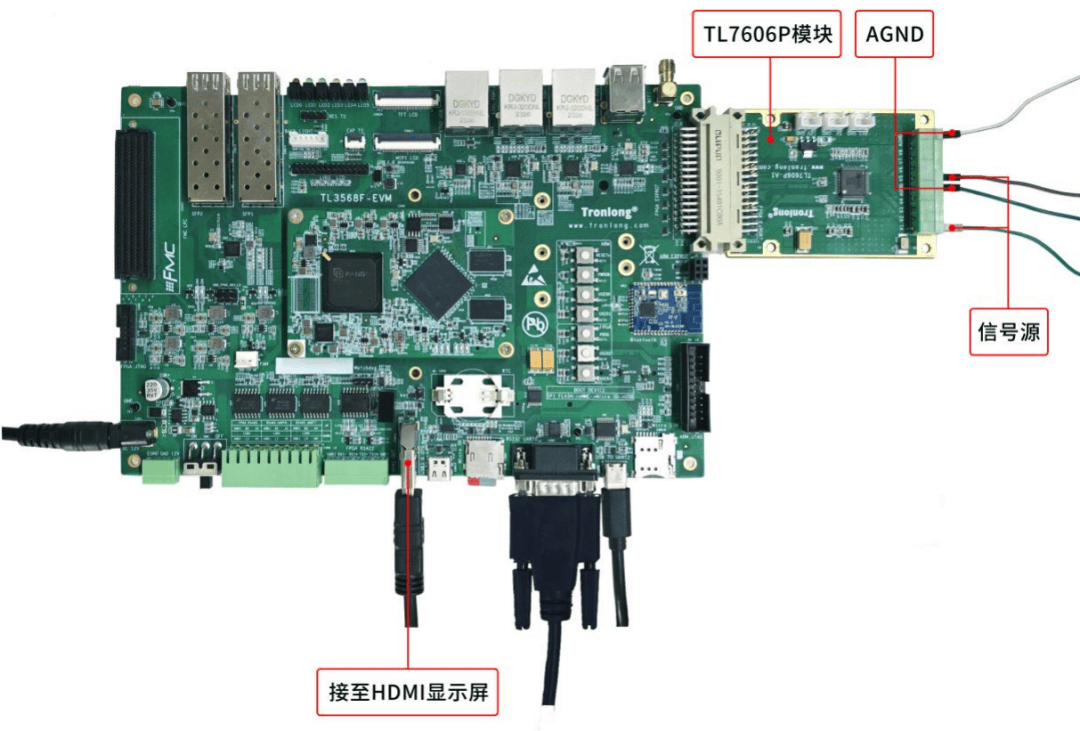

TL7606P模块测试

请将创龙科技TL7606P模块连接至评估板FPGA EXPORT(CON26)接口,将HDMI显示器与评估板HDMI OUT接口连接,请使用Type-C线将评估板USB TO UART2串口连接至PC机,使用RS232交叉串口母母线、USB转RS232公头串口线将评估板RS232 UART0串口连接至PC机,硬件连接如下图所示。

图 5

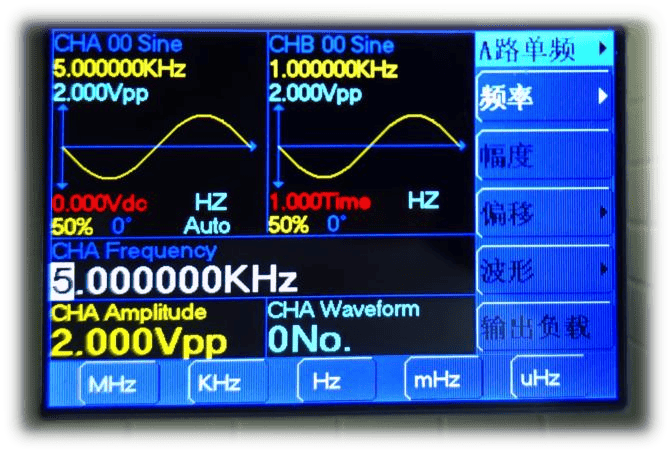

案例支持TL7606P模块8通道同时采集与显示。本次测试以TL7606P模块V1和V5通道为例,请将TL7606P模块的V1和V5通道分别正确连接至信号发生器A通道和B通道。信号发生器设置A通道输出频率为5KHz、峰峰值为2.0Vpp(即幅值为1.0V)的正弦波信号,B通道输出频率为1KHz、峰峰值为2.0Vpp(即幅值为1.0V)的正弦波信号,如下图所示。

备注:

TL7606P模块量程为±5V,待测信号电压请勿超过模块量程,否则可能会导致模块损坏。

图 6

请参考我司产品资料的用户手册,进行环境搭建、将FPGA端的可执行程序固化至FPGA运行、amp.img镜像文件固化至评估板(用于运行RT-Thread(RTOS)程序)等操作,然后进行如下步骤进行操作。a)单步模式执行如下命令,以单步模式采集数据。

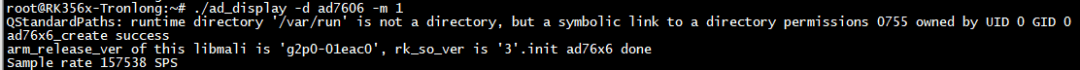

Target#

./ad_display -d ad7606 -m 1参数解析:-d:指定设备节点;-m:选择运行模式(1表示单步模式,2表示连续模式)。

图 7

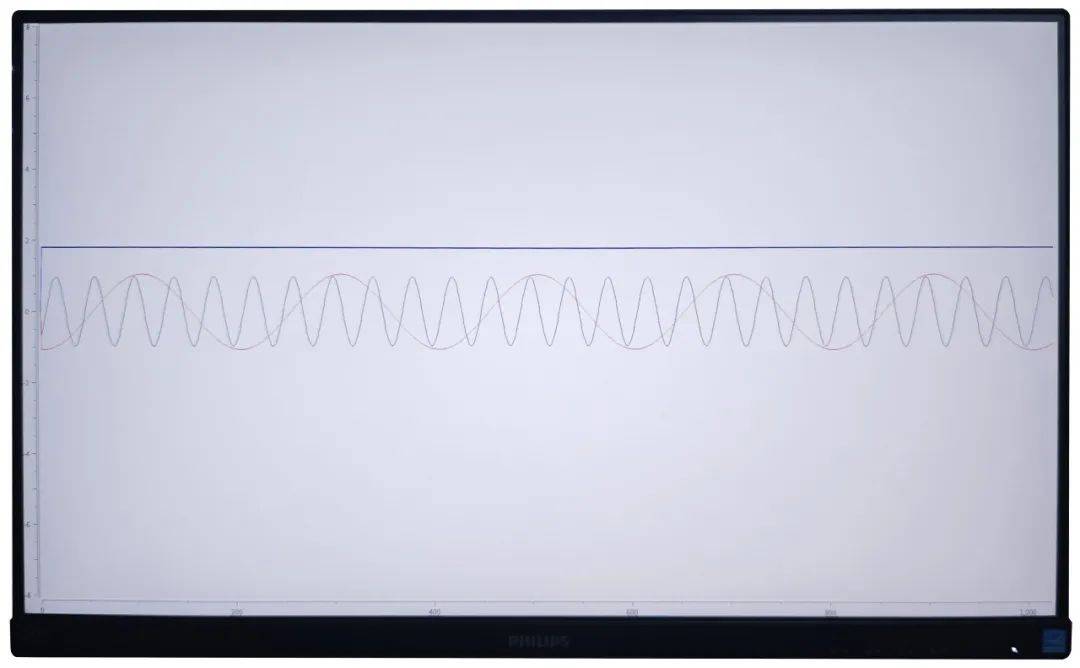

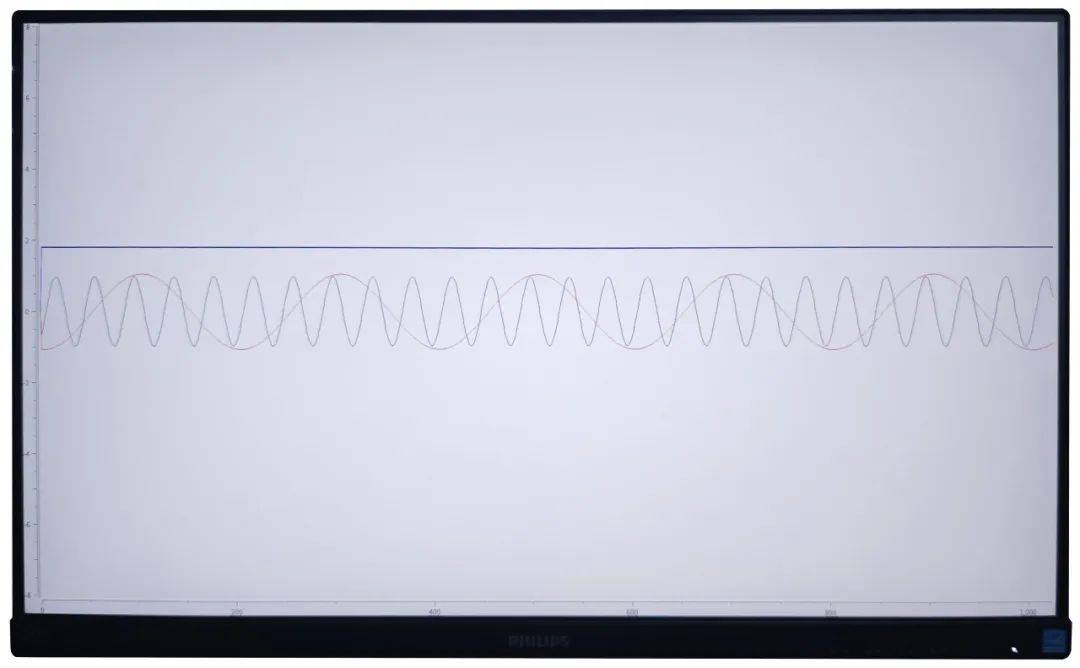

同时,HDMI显示屏将会显示静态波形,如下图所示。

图 8

按下"Ctrl + C"可停止程序运行。b)连续模式执行如下命令,以连续模式采集数据。

Target#

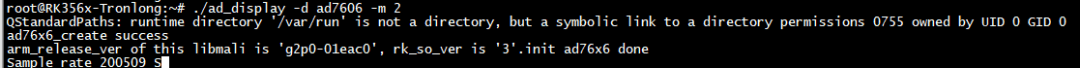

./ad_display -d ad7606 -m 2

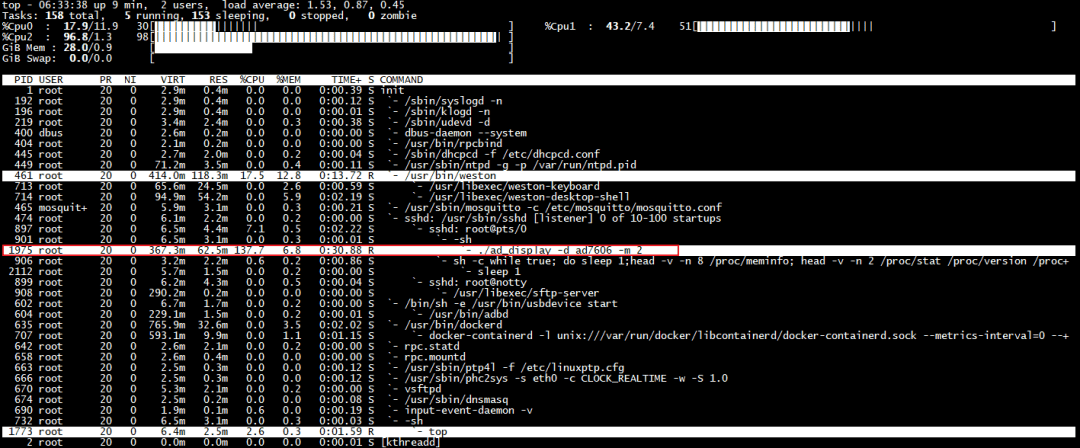

图 9

同时,HDMI显示屏将会实时显示动态波形,如下图所示。

图 10

程序运行过程中,CPU占用率约为137.7%。

图 11

按下"Ctrl + C"可停止程序运行。

TL7616P模块和TL7606P模块测试步骤类似,可以参考我司的案例说明文档。