使用软件:vivado2020.1、仿真用vivado自带的仿真

摘要: 不谈AXI stream、lite、interconnect等等东西,仅仅讨论一下这个IP核的用法,从这个IP核入手,实际掌握tvalid、tready的用法,对日后整体了解并掌握AXI,应该会有帮助。

目录

1.IP核

vivado ——> IP Catalog ——> AXI4-Stream Data FIFO

一开始只需要关注一些简单的东西就行了,比如:FIFO depth、TDATA width(bytes)。位宽决定了传一个数据的最大宽度,深度决定了能传多少个这样的数据。如果什么都不改,1 width(bytes)就是8bit,数据最大表示的数是255(十进制),一共能传512 * 8bits。

直接创建IP核之后,可以点开它的IP Example design去熟悉了解怎么用。

2.master(写)和slave(读)

写一个例子,比如一共要读写16384个数,那么一次要写256个数(64次),TDATA width(bytes)给2,FIFO depth看着给,给小了,那么在写和读的时候会不一样,这里直接给了16384。

写的时候注意master、fifo、slave之间的连线就可以

无论在读的时候还是在写的时候,tvalid和tready只能input一个,output一个。tvalid和tready的变化可以自己根据协议去写,这里我直接根据的IP Example design去写的,不知道对应的是AXI协议中的哪一种。

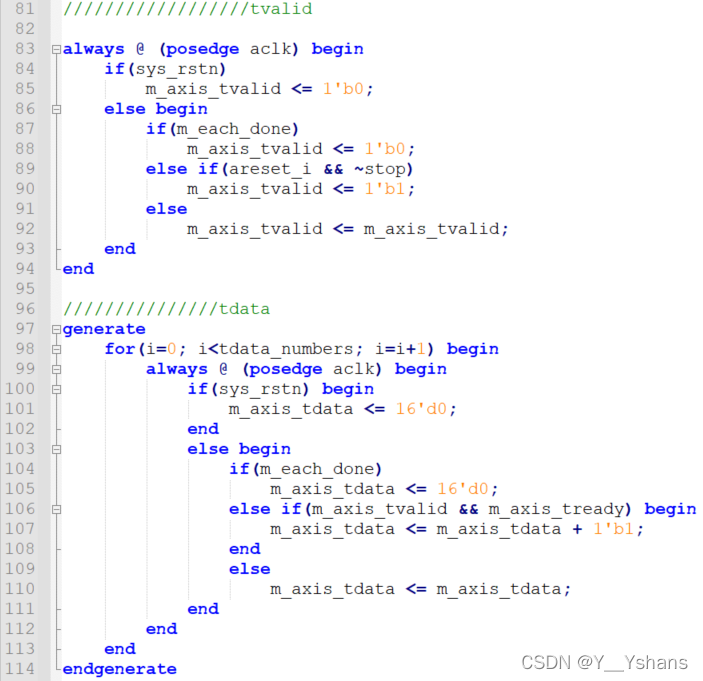

下图是master里面的tvalid和tdata

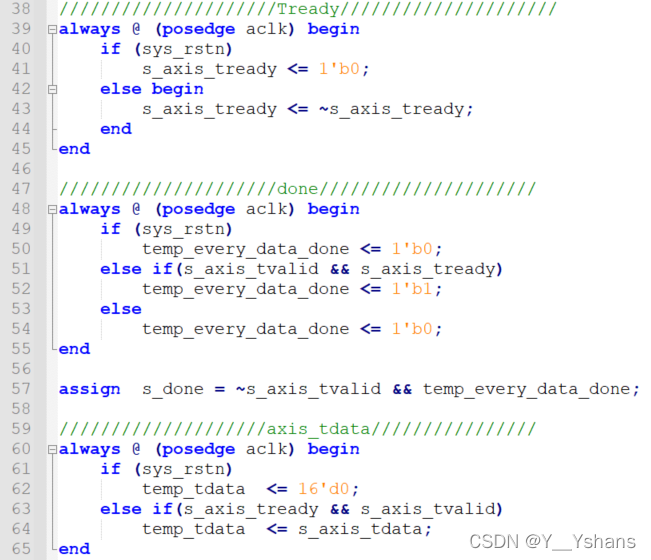

下图是slave里面的tready和data

总结

工程的代码已经上传。

AXI_Stream_Data_FIFO.7z-硬件开发文档类资源-CSDN下载

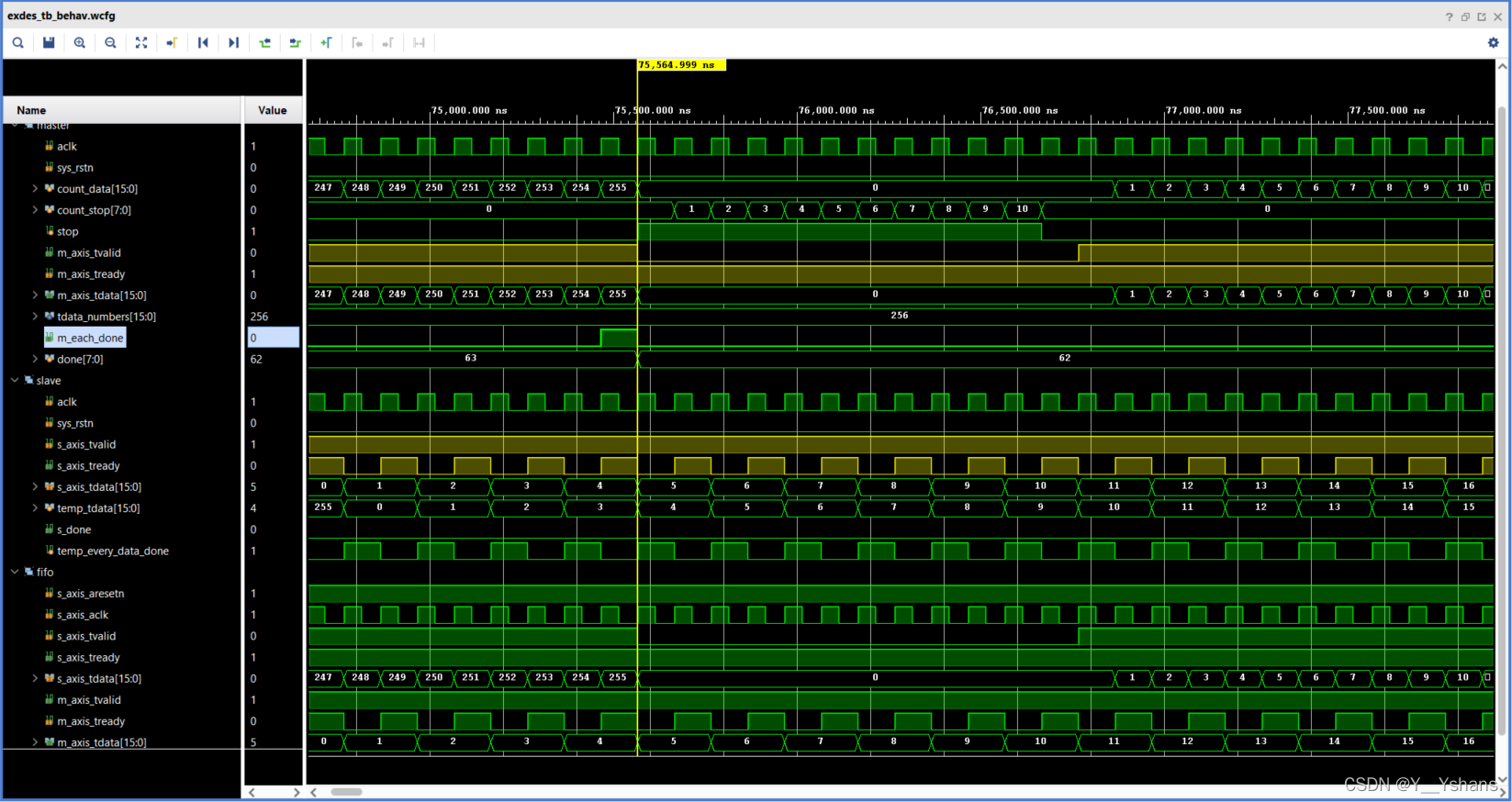

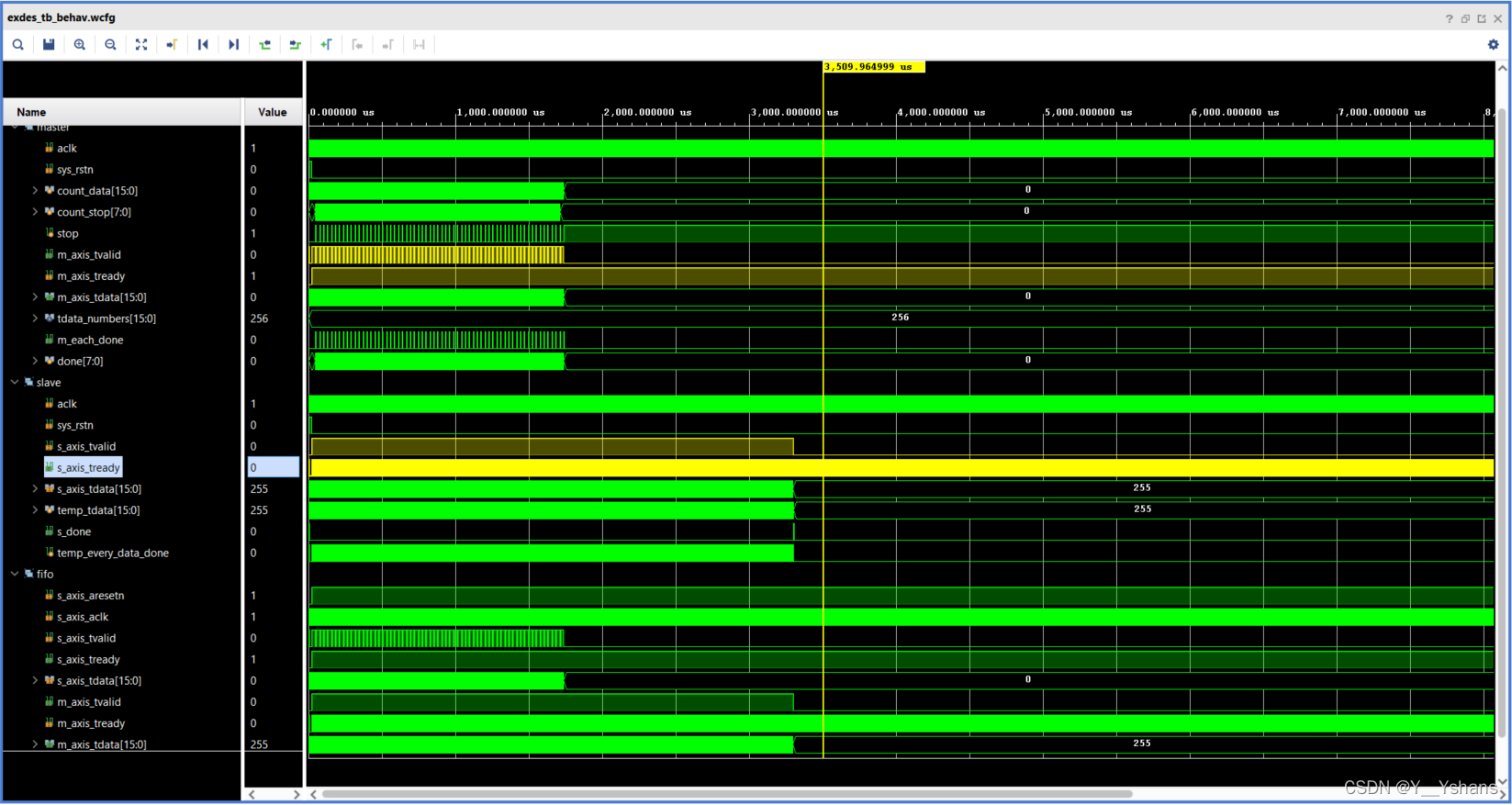

最终实现图