系列文章目录

目录

前言

由于博士的研究课题涉及到了VLSI设计,并且我以前从事的研究几乎没有对这个方向有任何的涉猎,因此开坑记录一下自己从零开始学习的心得与体会。同时也希望能够帮助到有同样科研任务的你。

此篇文章为工具包yosys的概述,包含简单介绍及一个简单的工程实例。

一、Yosys是什么?

Yosys是一个用于执行RTL合成的开源工具(关于RTL的相关介绍,可以参考(还没写完,马上了))。其支持多种输入格式,包括今天实例中的Verilog。

Yosys可以输出多种格式的合成网络列表,在这篇教程的实例中,我们使用Yosys合成一个简单的数字逻辑,并将其映射到一个标准的Cell library中。

二、开始使用Yosys

请确保使用Linux系统,本文中使用的系统为CentOS7.9

1.使用指令安装Yosys

在使用Yosys之前,请先安装一些必须的依赖项,使用以下指令时请注意使用管理员权限

$ sudo apt-get install build-essential clang bison flex libreadline-dev gawk tcl-dev libffi-dev git graphviz xdot pkg-config python3 libboost-system-dev libboost-python-dev libboost-filesystem-dev zlib1g-dev

$ git clone https://github.com/YosysHQ/yosys.git

$ cd yosys

$ make

$ sudo make install2.启动Yosys工具

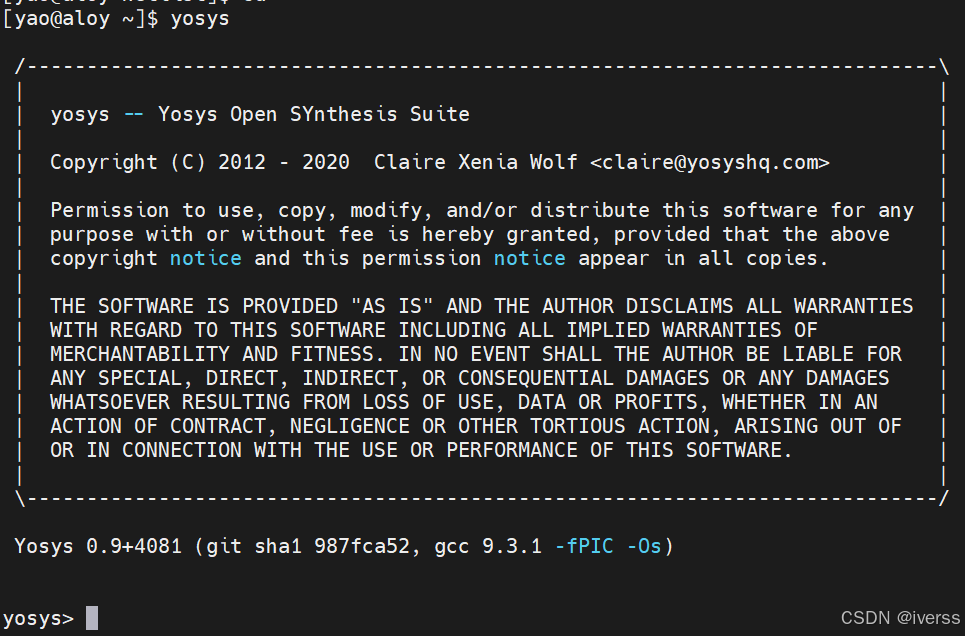

安装完成相关依赖后,使用.yosys指令在当前目录下启动工具包,如下图所示。由于我使用的服务器端已经在安装了Yosys并设置了环境变量,因此我直接使用yosys指令即可。

3.开始逻辑综合

首先使用Verilog定义一个选择器器件,储存与top.v中,这是一个基本的选择器设计,包含基本的逻辑组合及顺序元素。同时需要一个来自Slivaco Open-Cell 45 nanometer 免费的PDK库。整个项目的代码文件及库文件可以从此链接项目下载 yosys_top ;或自行通过官方申请15nm Open-Cell Library and 45nm FreePDK。

top.v文件代码:

/* Verilog code to demonstrate the netlist synthesis */

module top(a, b, clk, select, out);

input a, b, clk, select;

output out;

reg out;

wire y;

assign y = (select) ? b : a;

always @(posedge clk)

begin

out <= y;

end

endmodule使用TCL脚本命令对top.v器件进行逻辑综合:

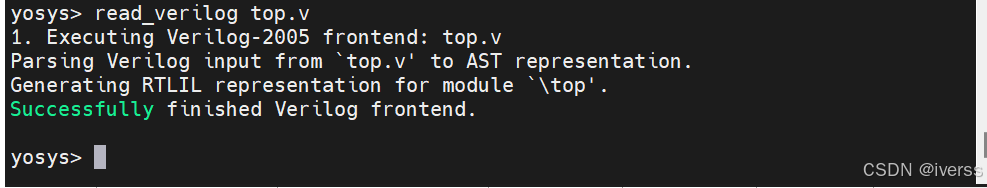

1)读取模型

read_verilog top.v 读取 Verilog 文件 top.v。Yosys 将此文件中的设计加载到它的设计数据库中。这一步将硬件设计代码导入工具内。

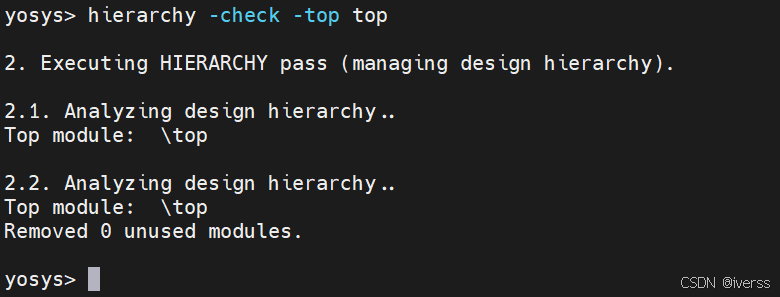

2)检查并展开设计层次结构

hierarchy -check -top top 这个命令检查并展开设计层次结构,-check 参数用于检查设计中的潜在问题,比如未定义的模块。-top top 表示指定 top 为顶层模块。顶层模块是电路设计的起点,也是所有其他子模块的父模块。

3)netlist转换

proc 这个命令将 Verilog 代码中的进程(如 always 块)转换为netlist。netlist是一种反映电路连接关系的描述,它将高级的行为描述(如 always 块的行为)转化为门级电路结构。

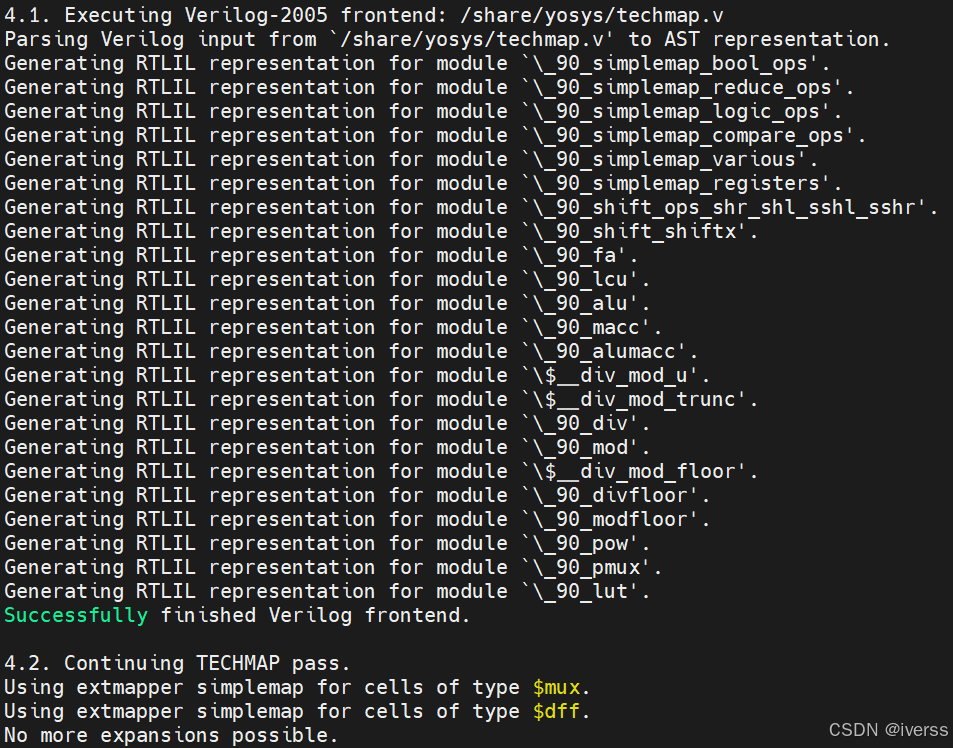

4)逻辑块映射为门级电路库

techmap该命令将设计中的抽象逻辑块映射到内部的门级电路库。Yosys 使用内建的基础单元库(如与门、或门、触发器等),将高级描述的硬件设计映射到这些基础单元上。

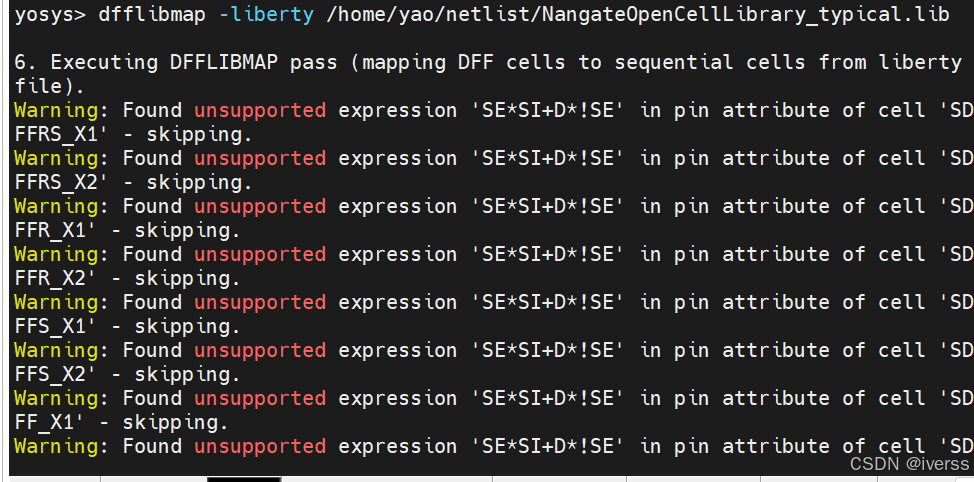

5)触发器映射到实际的标准单元

dfflibmap -liberty NangateOpenCellLibrary_typical.lib 专门用于触发器(D 触发器等)的映射。使用 NangateOpenCellLibrary_typical.lib 这个标准单元库文件,将设计中的触发器映射到实际的标准单元。标准单元库是晶圆厂提供的包含各种逻辑门、触发器等电路的物理实现和电气特性描述的文件。这里的 -liberty 选项表明输入的是 Liberty 格式的库文件。注意,NangateOpenCellLibrary_typical.lib 需要替换为你服务器中的对应路径。NangateOpenCellLibrary_typical.lib 的下载地址为,或者直接使用此项目中的库文件。

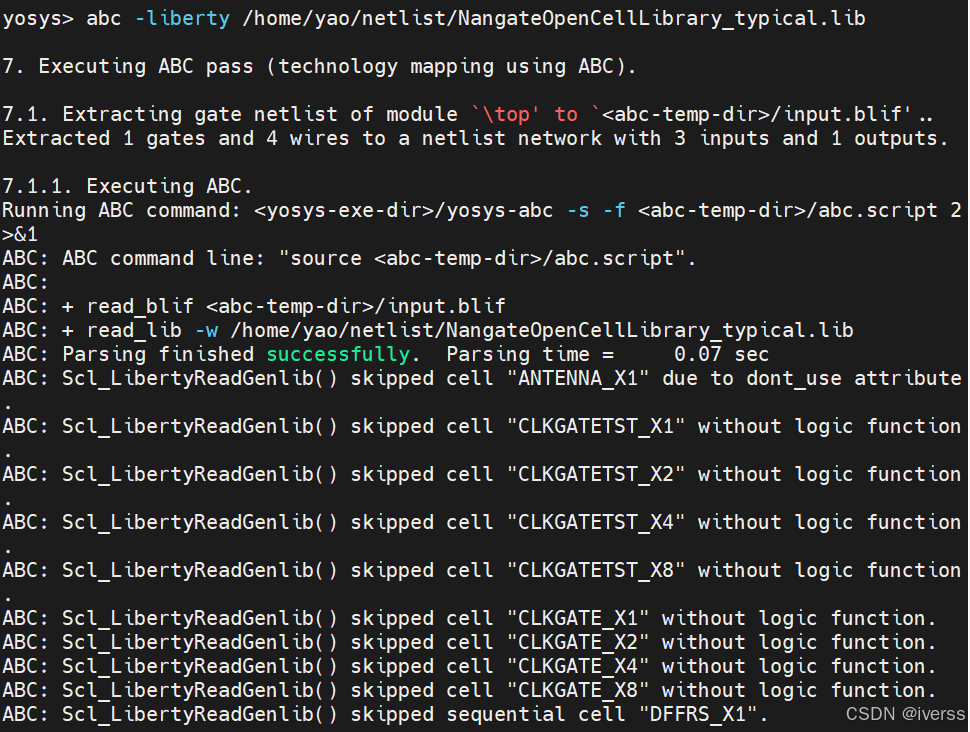

6)逻辑综合

abc -liberty NangateOpenCellLibrary_typical.lib abc 是 Yosys 内部集成的逻辑优化和综合工具。这个命令将设计中的组合逻辑(如 assign 语句)映射到 NangateOpenCellLibrary_typical.lib 中定义的标准单元上。它同样使用 Liberty 格式的库文件。同样需要使用自己服务器上的路径替换NangateOpenCellLibrary_typical.lib。

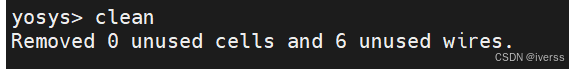

7)简化电路

cleanclean命令移除设计中未使用的逻辑单元或未连接的信号(多余的门、线、触发器等)。这样可以简化电路,减少资源消耗。

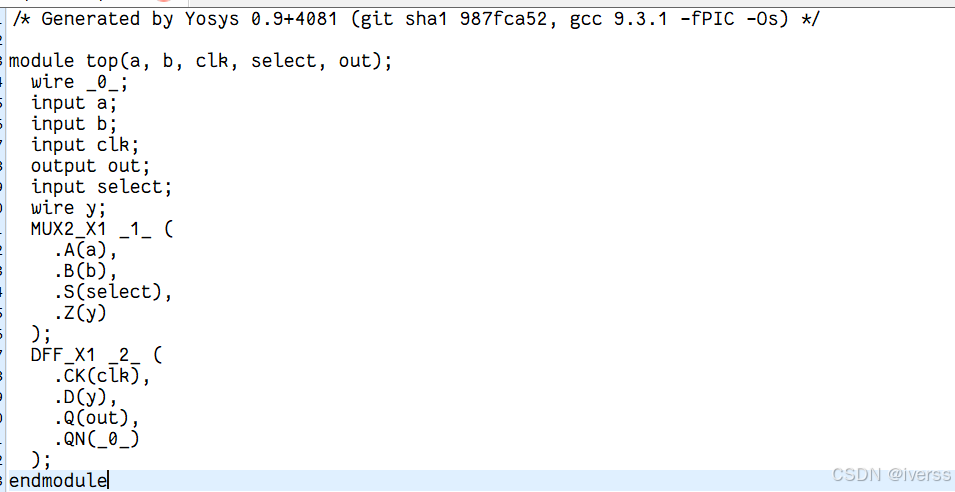

8)生成综合后设计的Verilog文件

write_verilog -noattr synth-example.v 这个命令将当前综合后的设计写回到一个新的 Verilog 文件 synth-example.v 中。-noattr 选项表示不输出原 Verilog 代码中的属性(attributes),通常这些属性是在综合过程中附加的信息,用户可能不需要在输出文件中看到这些信息。生成后的文件如图所示。

三、解析综合出的netlist文件

1.模块定义

module top(a, b, clk, select, out);

这行定义了模块 top,与原始 top.v 中的模块定义一致。它包括输入信号 a, b, clk, 和 select,以及输出信号 out。

2.信号声明

wire _0_;

input a;

input b;

input clk;

output out;

input select;

wire y;

wire _0_是一个在门级净表中生成的内部信号,表示未使用的输出信号或中间信号。这里的_0_是没有特别含义的自动生成的信号名,在综合后用于优化某些未使用的部分。input a,input b,input clk,input select和output out对应于原始模块中的输入输出定义,没什么变化。wire y对应于原始代码中用于表示assign y = (select) ? b : a;的组合逻辑输出。

3.多路选择器(MUX)部分

MUX2_X1 _1_ (

.A(a),

.B(b),

.S(select),

.Z(y)

);

这里的 MUX2_X1 是一个标准单元库中的 2:1 多路选择器(MUX)。这是对原始代码中 assign y = (select) ? b : a; 的实现。

.A(a)表示 MUX 的第一个输入A接收信号a。.B(b)表示 MUX 的第二个输入B接收信号b。.S(select)表示选择输入S接收信号select,用于决定输出是a还是b。.Z(y)表示 MUX 的输出接到信号y上。

4.D触发器部分

DFF_X1 _2_ (

.CK(clk),

.D(y),

.Q(out),

.QN(_0_)

);

这里的 DFF_X1 是一个 D 触发器单元。它将信号 y 存储到寄存器中,并在时钟信号 clk 的上升沿更新输出信号 out。

.CK(clk)表示时钟输入连接到clk。.D(y)表示数据输入D接收信号y,这对应于y的值在时钟上升沿时被存储。.Q(out)表示触发器的输出Q接到输出信号out,这与原始代码中的out <= y;相对应。.QN(_0_)表示触发器的反向输出QN接到内部信号_0_,但这个信号在这里没有实际用途(可能是为了占位或优化目的)。在实际设计中,这个反向输出_0_是未使用的。

总结

本文通过一个简单实例完成了对Yosys基本功能运用的介绍。完成了RTL到最终的netlist文件的综合。

参考文献

【1】Exploring Logic Synthesis with Yosys: A Tutorial Overview