1.思考题

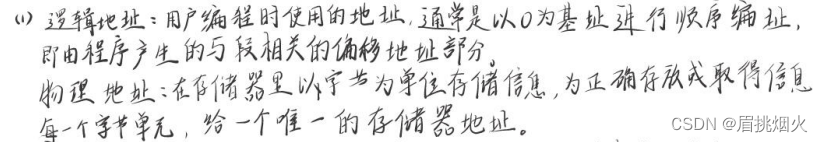

(1)什么是逻辑地址?什么是物理地址?

(2)什么是地址转换?哪些方法可以实现地址转换?

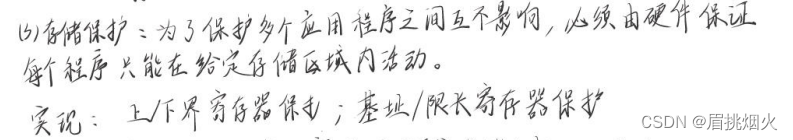

(3)什么是存储保护?在分区存储管理中如何实现分区的存储保护?

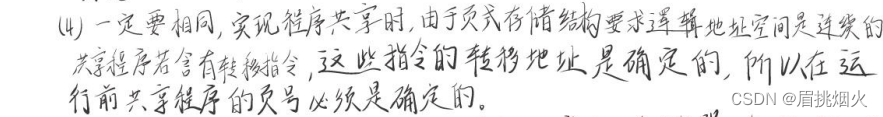

(4)在页式存储器中实现程序共享时,共享程序的页号是否一定要相同?为什么?

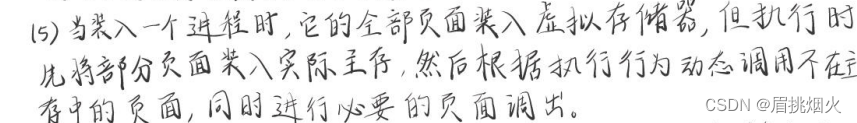

(5)试述页式虚拟存储管理的实现原理。

(6)什么是抖动?试述抖动产生的主要原因。

2.应用题

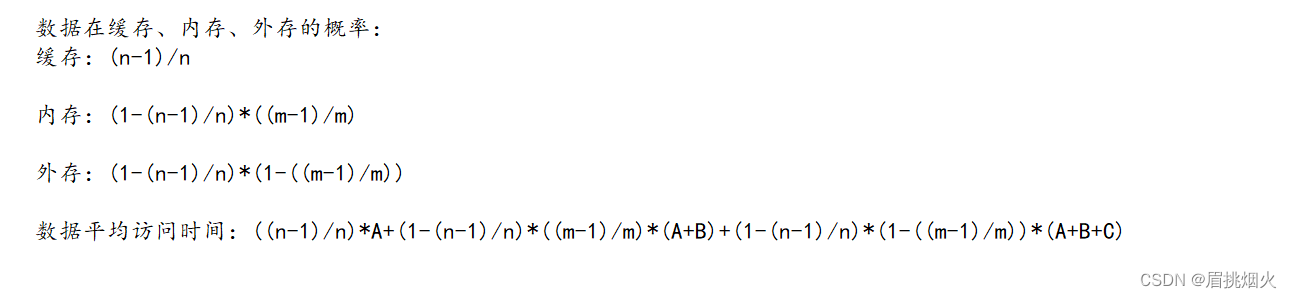

(1)某虚拟存储器基于缓存、内存、外存实现。如果数据在缓存中,访问数据需要 A ns;如果数据在内存中,则另外需要B ns将其装人缓存;如果数据在外存中,则还需要C ns 将其读人内存。假设缓存命中率为(n-1)/n,内存命中率为(m-1)/m,则数据的平均访问时间是多少?

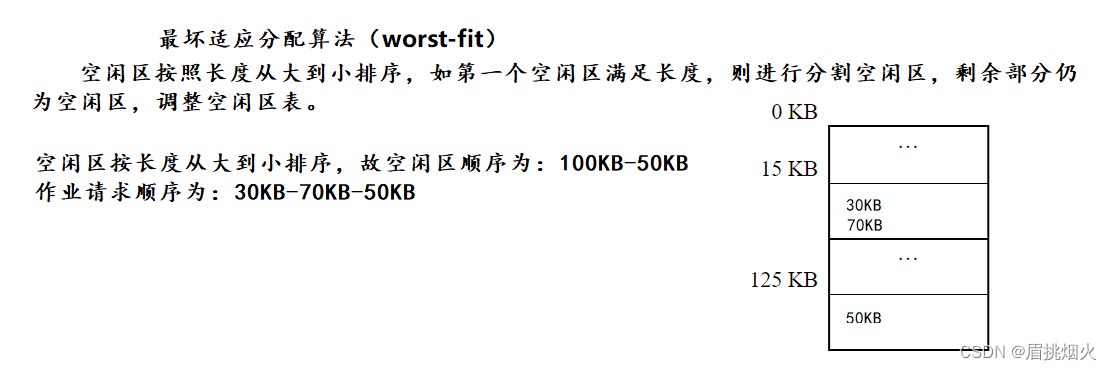

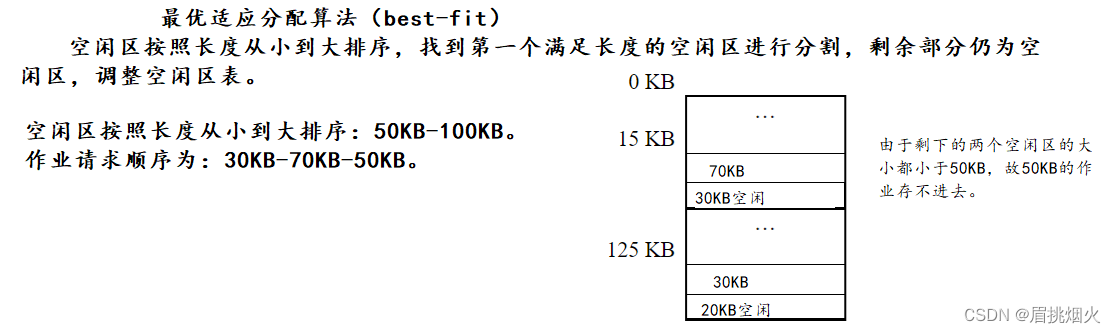

(2)在可变分区存储管理方式下,如题图 3-1 所示,内存中有两个空闲区。现有大小分别为30 KB、70 KB、50 KB 的作业依次发出请求,分别使用最先适配、最坏适配和最优适配算法处理这个作业序列,请向哪种算法可以满足所有作业的分配要求?为什么?

题图 3-1

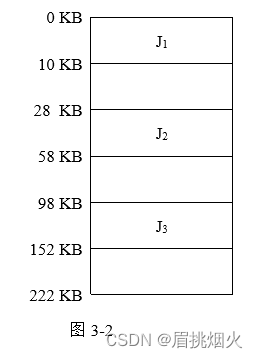

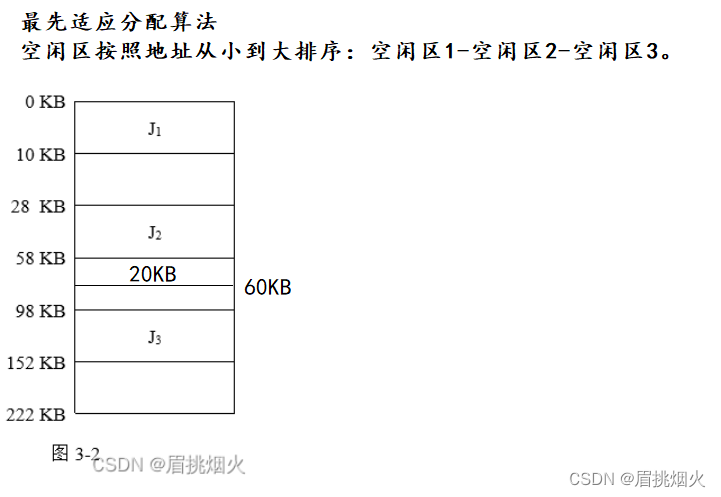

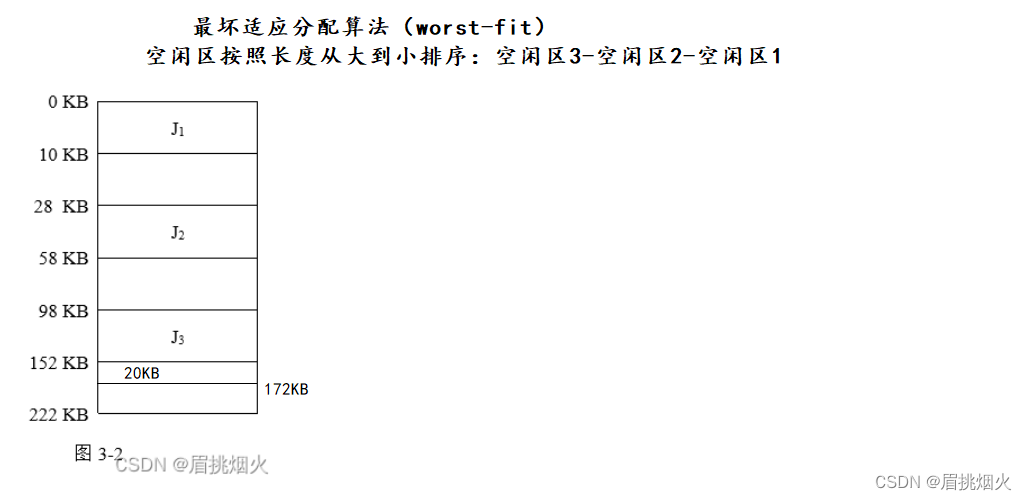

(3)设某系统中作业J1、J2、J3占用内存的情况如题图3-2 所示。现有一个长度为20 KB 的作业J4要装入内存,当采用可变分区存储管理时,请回答:①J4装入前的内存已分配表和末分配表的内容。②写出装入J4的工作流程,并说明采用了何种分配算法。

(4)某一页式存储管理系统,假设其页表全部存放在内存中。① 若访问内存的时间为120 ns,那么访问一个数据的时间是多少?② 若增加一个快表,无论命中与否均需20 ns的开销,假设快表的命中率为80%,则此时访问一个数据的时间是多少?

① 120*2=240ns

② (120+20)*0.8+(120+120+20)*0.2=164ns

(5)在一个有快表的页式虚拟存储管理系统中,设内存访问周期为 1 μs,内外存传送一个页面的平均时间为5 ms。已知快表的命中率为75%,缺页中断率为 10%,忽略快表访同时间,计算内存的有效存取时间。

1*0.75+2*0.15+(5000+2)*0.1=0.75+0.3+500.2=501.25us

(6)采用 LRU 页面调度算法的页式虚拟存储管理系统,其页面尺寸为 4 KB,内存访向时间为100 ns,快表访问时间为20 ns,缺页中断处理耗时 25 ms。现有一个长度为30 KB 的进程P进入系统,分配给P 的页框有3块,进程的所有页面都在进行时动态装入。若P访问快表的命中率为 20%,对于页面号访向序列 7-0-1-2-0-3-0-4-2-3-0-3-2-1-2-0-1-7-0-1,计算平均有效访问时间。

-

页号 7 0 1 2 0 3 0 4 2 3 0 3 2 1 2 0 1 7 0 1 页框号1 7 0 1 2 0 3 0 4 2 3 0 3 2 1 2 0 1 7 0 1 页框号2 7 0 1 2 0 3 0 4 2 3 0 3 2 1 2 0 1 7 0 页框号3 7 0 1 2 2 3 0 4 2 2 0 3 3 1 2 0 1 7 命中 否 否 否 否 是 否 是 否 否 否 否 是 是 否 是 否 是 否 是 是 系统缺页率:12/20=0.6

-

访问时间:(100+20)*0.2+(100+100+20)*0.8*(1-0.6)+(100+100+20+2500)*0.8*0.6

(7)在某页式虚拟存储管理系统中,用户编程空间为32个页,页面大小为1 KB,内存空间为16 KB。如果应用程序有10页长,且己知页号为0—3的页已依次分得页框号为4、7、8、10的页框,试把逻辑地址 0AC5H 和 1AC5H 转换成对应的物理地址(十六进制表)。

已知页面大小为1KB,则页内偏移有10位。

0AC5H 的二进制为: 0000 1010 1100 0101,高六位为页号:0000 10,即为2,对应页框号为8,故物理地址为:0010 0010 1100 0101,即为:22C5H

1AC5H 的二进制为: 0001 1010 1100 0101,高六位为页号:0001 10,即为6,页号6对应页框号不在内存空间上(缺页),无物理地址。

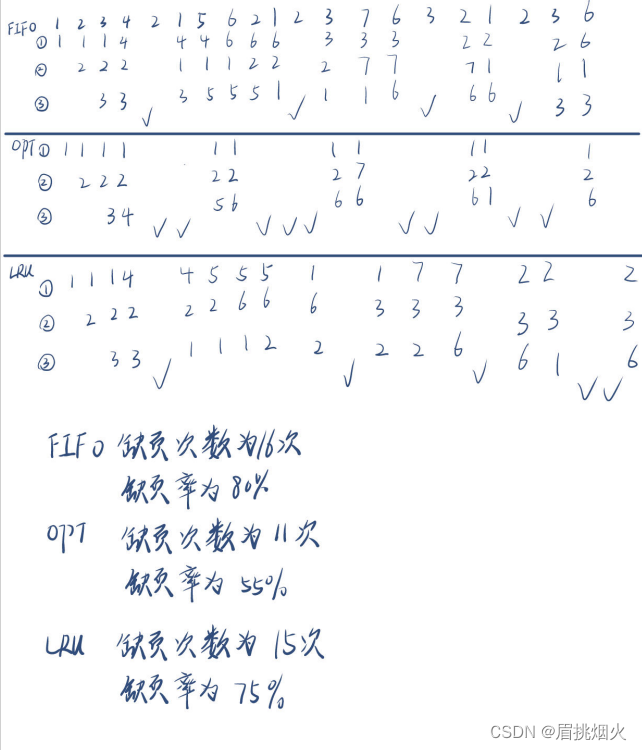

(8)在一个页式虛拟存储管理系统中,一个程序运行的页面走向是1-2-3-4-2-1-5-6-2-1-2-3-7-6-3-2-1-2-3-6。分别使用 FIFO、OPT 和 LRU 页面调度算法,对于分配给程序3个页框的情况,求出访向过程中所发生的缺页中断次数和缺页中断率。

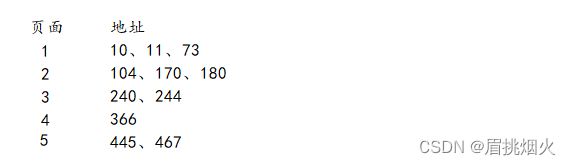

(9)在一个页式虛拟存储管理系统中,进程访问地址的序列为 10-11-104-170-73-305-180-240-244-445-467-366。请回答:① 如果页面大小为 100 B,给出页面访向序列;② 若进程分得3个页框,采用 FIFO 和 LRU 页面调度算法,计算缺页中断率。

① 1-1-2-2-1-4-2-3-3-5-5-4

(10) 假设一个进程分配到 4 个页框,每页的装入时间、最后访问时间、访向位 R、修改位 D 如下表所示(所有数字为十进制,且从0开始),当进程访向第4 页时,产生缺页中断。请分别使用 FIFO 和LRU 页面调度算法,写出缺页中断服务程序选择换出的页面。

| 页 | 页框 | 装入时间 | 最后访问时间 | R | D |

| 2 | 0 | 60 | 161 | 0 | 1 |

| 1 | 1 | 130 | 160 | 0 | 0 |

| 0 | 2 | 26 | 162 | 1 | 0 |

| 3 | 3 | 20 | 163 | 1 | 1 |

FIFO 页面调度算法:3

LRU 页面调度算法:1

(11)已知数组 int A[100][100];其元素按行存储。在虛拟存储管理系统中,采用 LRU 页面调度算法,一个进程有3 页内存空间,每页可以存放200 个整数。其中第1页存放程序,且假定程序已在内存中。

程序 A:

for (int i=0; i<100; i++)

for(int j=0; j<100; j++)

A[i,j] = 0;

程序 B:

for (int j=0; j<100; j++)

for(int i=0; i<100; i++)

A[i,j] = 0;

分别计算程序A和程序B在执行过程中的缺页中断次数。

一个进程在内存中有3个页,且其中的1页用于存 放程序,则用作存放数据的页面只有2个。 数组A中有10000个整数,每页 存放200个整数,故数组占用空间50页。

程序A: 程序A对数组A的访问是按行进行,即按照存储顺序进行。所以只有在访问每一页的第一个数据时会缺页,同一页的其他数据不会发生缺页,故程序A的缺页次数为50。

程序B: 程序B对数组A的访问是按列进行,而数组A每行有100个数据,每页可以存放200个数据,因此每页中有2个 数据属于同一列,每次缺页中断调进一页时,只有其中的 2个数据被赋予0值,即程序B对数组A每两次访问会遇到一次缺页。200/100=2,10000/2=5000,故缺页次数为5000.

(12)给定某段式存储器的段表如下:

| 段号 | 段首址 | 段长 |

| 0 | 219 | 600 |

| 1 | 2300 | 14 |

| 2 | 90 | 100 |

| 3 | 1327 | 580 |

| 4 | 1952 | 96 |

试计算以下二维逻辑地址<段号,段内位移>对应的物理地址(以十六进制表示):

①<0, 430>;②<3, 400>; ③ <1, 1>; ④ <2, 500>; ⑤ <4, 42>。

物理地址=段首地址+段内偏移

①649;②1727; ③ 2301; ④ 越界(500>100(该段段长)); ⑤ 1994。

假设一个任务被划分成4个大小相等的段,每段包含8个页表,页面大小为2 KB。请问在这一段页式存储管理系统中:

① 每段的最大尺寸是多少?

2*8=16KB

② 此任务的逻辑地址空间最大是多少?

4*16=64KB

③若此任务访同逻辑地址为5ABCH 的一个数据,请将该逻辑地址转化为“段号:页号|页内地址”的形式。

5ABCH 对应二进制 0101 1010 1011 1100

页面大小为2 KB,故低11位为页内偏移,高5位为页号 01011,即11。

第12到14位为页号,高两位为段号。

01:011 | 010 1011 1100