基于FPGA实现UDP通信,看完你就懂了!!!(附源码)

在前面几个文章我们介绍了UDP通信的物理接口,协议以及数据发送的实现,本次我们就来实现UDP数据接收部分,本次使用的开发板同样为锆石科技的FPGA A4_plus开发板,该开发板搭载的芯片为Altera(现已被intel收购)的一款EP4CE15F23C8芯片,而本次要实现的功能很简单,只实现了最基本的功能,接收一定的数据,当数据接收完之后,控制LED灯点亮。

有关UDP通信协议的相关内容,可以翻看我之前的几篇文章,有较为详细的介绍:

FPGA实现UDP通信(2)——通信接口简介_fpga网口通信-CSDN博客

FPGA实现UDP通信(3)——数据发送实现_fpga ps端实现udp通信-CSDN博客

最后我们需要在我们的板子上实现UDP通信协议,本次实现的为千兆以太网接口,接口类型为GMII接口,即在每次的时钟上升沿接收一个字节的数据,本次主要通过仿真观测波形来查看接收状态,并且为自动CRC校验,即仿真文件发送数据是通过CRC手动计算校验值来进行发送的,而在主程序即UDP接收端是通过自动CRC校验来接收数据的。

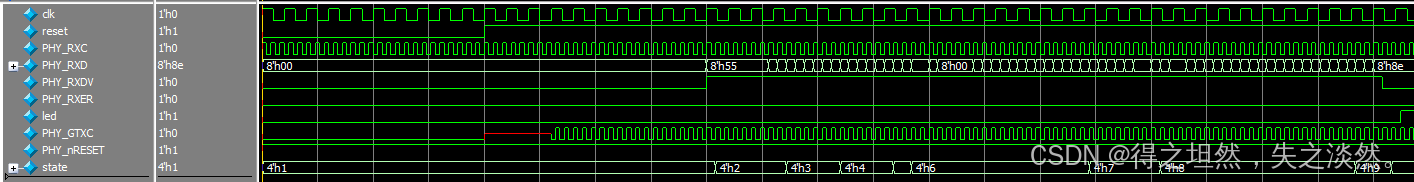

本次仿真的数据波形如下图所示。

由图中可以看到,数据接收是基于状态机来进行接收的,当接收数据完毕之后,led灯被拉高,说明数据接收正确并且CRC校验同样正确。

最后,贴上部分程序,需要完整工程代码的可以私信我。

/*

* 功能:实现UDP接收数据模块

* 作者:王志川

* 时间:2024.10.13

*/

module udp_rx(

input clk, //FPGA输入时钟信号,50M

input reset, //FPGA复位信号

input PHY_RXC, //数据接收时钟信号

input [7:0]PHY_RXD, //接收数据信号

input PHY_RXDV, //接收数据有效信号

input PHY_RXER, //接收错误标志信号

output reg led, //led指示灯

output PHY_GTXC, //发送时钟信号

output PHY_nRESET, //PHY芯片复位信号

output reg [3:0]state

);

//保持复位引脚为1,即不产生复位信号

assign PHY_nRESET = 1'b1;

//数据接收时钟分配

wire rx_125M;

assign rx_125M = PHY_RXC;

//pll IP核,输入50M时钟,产生125M时钟

wire locked;

wire clk_125M;

pll_125M pll_125M(

.areset(~reset),

.inclk0(clk),

.c0(clk_125M),

.locked(locked)

);

//数据发送时钟

assign PHY_GTXC = clk_125M;