拿到文档不知怎么去操作(以前没有看过手册也不知道流程是什么,只用过人家生成的代码,就知道地址和数据),以及寄存器的配置等等一顿蒙,接下来的时间对DAC3482进行学习。

1.DAC3482官网网址如下:

DAC3482 data sheet, product information and support | TI.com

2.文档解读学习以及基础知识恶补

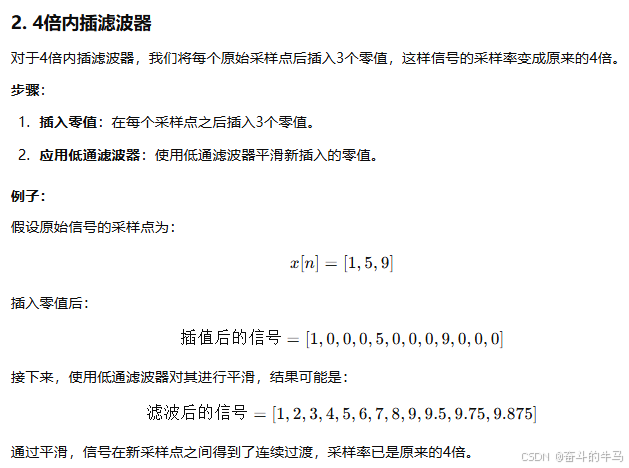

2.2.1 2、4、8、16 倍内插滤波器

通常与信号处理、尤其是数字信号处理中的 内插(Interpolation)技术有关。内插滤波器常用于数字信号中,将采样率增加到原来的若干倍。具体来说,倍数代表信号中插入的样本数,这样可以在不丢失重要信息的情况下提高采样率。

内插滤波器的基本工作原理:

内插滤波器的主要目的是在信号中插入更多的采样点,从而提高信号的采样率。其基本步骤如下:

- 插入零值:假设你从原始信号(采样率为Fs)生成一个更高采样率的信号。首先,通过插入零样本来增加信号的长度(假设插入2倍、4倍、8倍等),但这样会使信号变得“稀疏”。

- 滤波:通过低通滤波器滤除由于插入零值所产生的高频成分,确保信号平滑且连续。这就是内插滤波器的作用,它帮助恢复“平滑”的信号。

2倍、4倍、8倍、16倍内插滤波器:

这些不同倍数的内插滤波器意味着将采样率提高到原来的2倍、4倍、8倍或16倍。

2倍内插滤波器:

将每个原始采样点之后插入1个零值(使采样率翻倍),然后用低通滤波器平滑这些新插入的点。4倍内插滤波器:

将每个原始采样点后插入3个零值(使采样率翻4倍),然后进行滤波,恢复信号平滑度。8倍内插滤波器:

插入7个零值,确保信号转换后的平滑性。16倍内插滤波器:

插入15个零值,提升采样率到16倍。

.2.2.2 NCO是什么

NCO(Numerically Controlled Oscillator,数字控制振荡器)

NCO 是一种通过数字方法生成连续波形(如正弦波、方波等)的振荡器。与传统的模拟振荡器不同,NCO 使用数字信号处理技术来控制其输出信号的频率和相位,因此被广泛应用于数字通信、信号生成、频率合成等领域。

工作原理

NCO 的核心是一个数字信号生成器,它通过一个相位累加器和一个查找表(LUT)来生成连续的波形。其基本工作原理如下:

相位累加器(Phase Accumulator):

- NCO 的核心是一个相位累加器,它每个时钟周期增加一个常量的步进值。这个步进值决定了振荡器的频率。

- 相位累加器的输出是一个表示相位的数字值,通常是一个固定长度的二进制数(例如,32位)。随着时钟的进步,累加器的值不断增加,表示一个完整的周期。

查找表(LUT):

- 累加器的输出被用作查找表的地址,查找表内存储了周期性波形(如正弦波、方波等)的数值。

- 查找表通常存储在 ROM 或 RAM 中。每次读取时,根据相位值,从表中提取一个相应的波形值作为输出。

频率控制:

- 通过控制相位累加器的步进值,可以精确控制输出波形的频率。步进值越大,频率越高;步进值越小,频率越低。

输出波形:

- 查找表输出的数值可用于驱动 DAC(数模转换器),以产生模拟信号,或者直接作为数字信号使用。常见的波形有正弦波、余弦波、三角波、方波等。

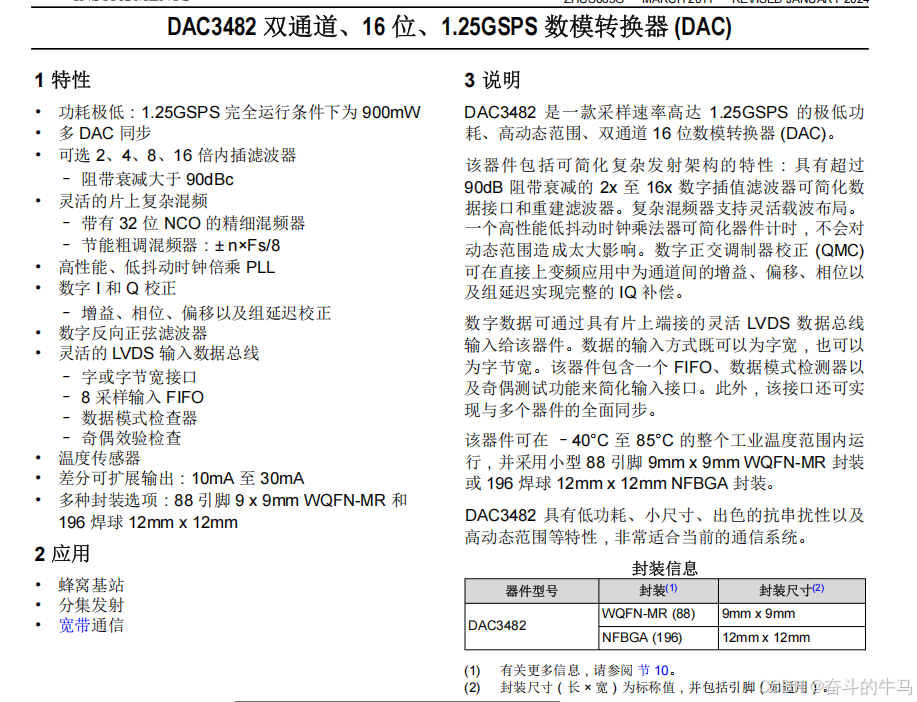

2.2.3 DAC3482

以上是DAC3482的简介 接下来只对6详细描述进行学习

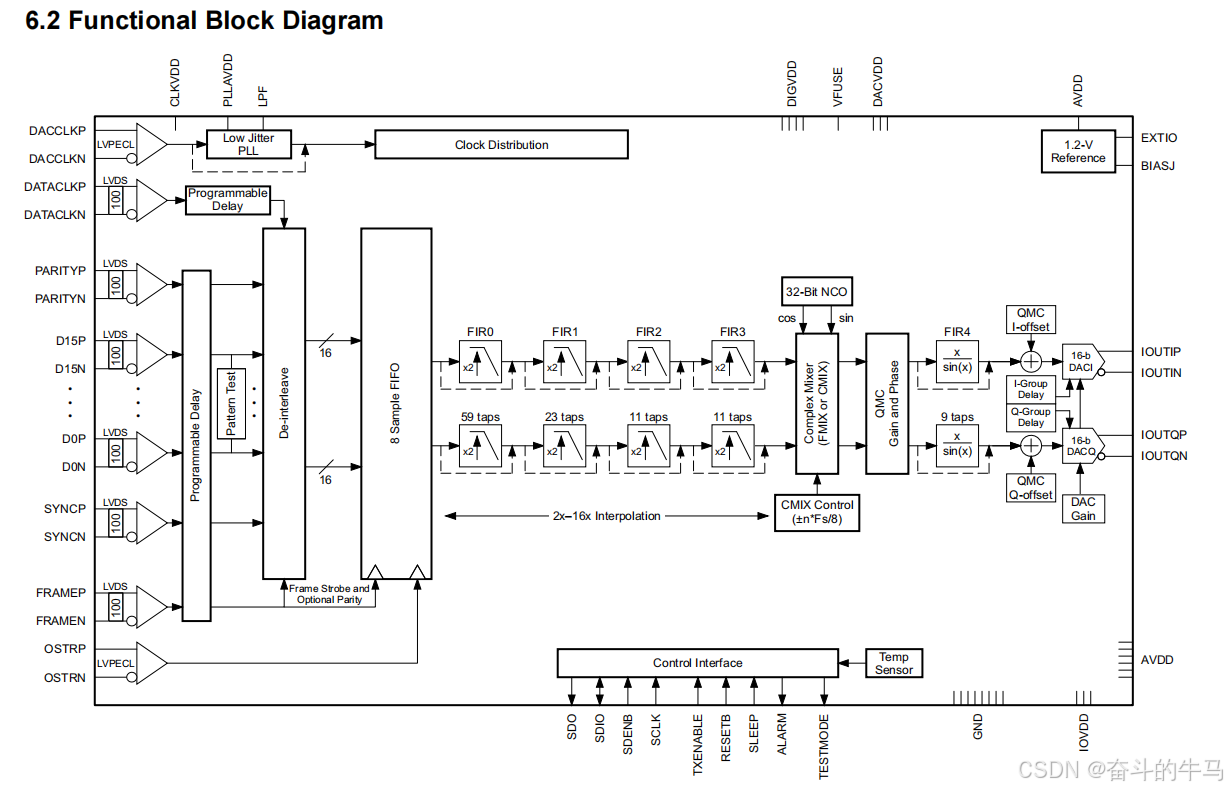

功能框图

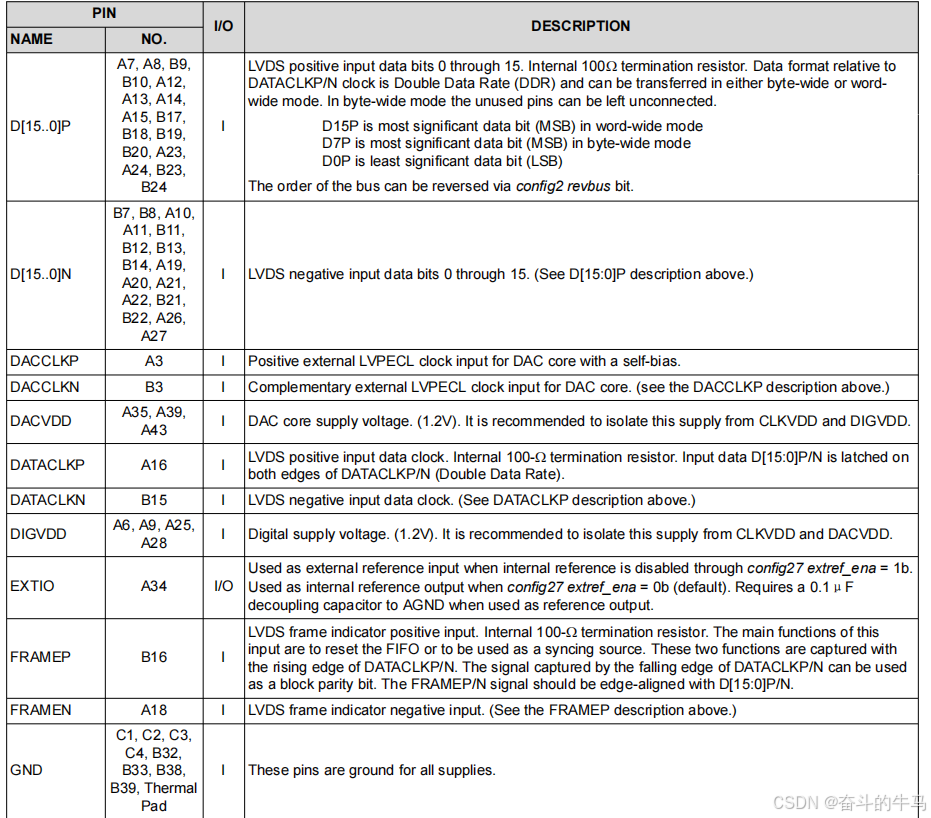

对于上述框架需要知道每个接口代表什么:根据文档内容做总结

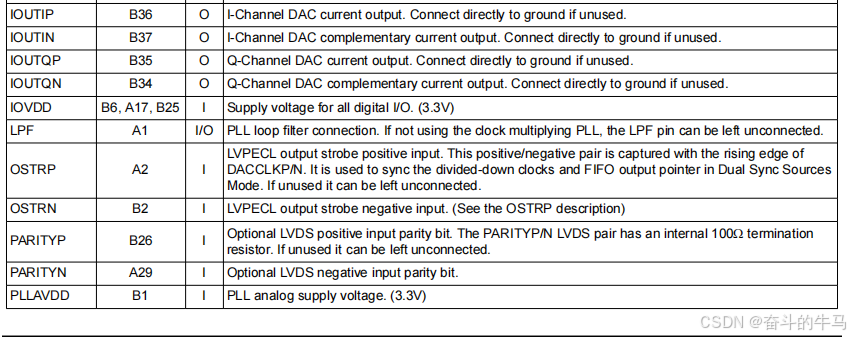

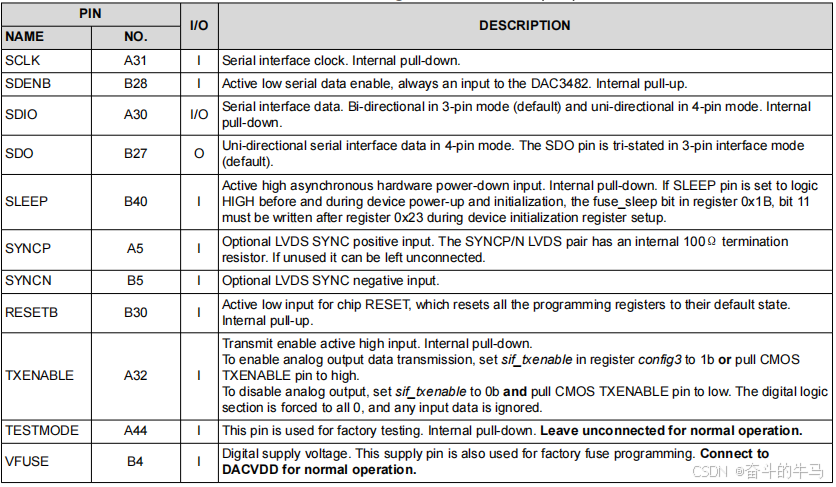

以上为各个管脚的功能图,现做总结:

AVDD:电压源3.3。CLKVDD:内部时钟缓冲器的电源电压。D[15..0]P:LVDS正输入数据位0到15 高位的第15bit 是字模式的重要位,第7bit位字节模式的重要位。D[15..0]N:LVDS为差分信号,这代表负输入数据位0到15。DATACLKP/N:数据的差分时钟。DACCLKP/N : LVPECL时钟输入的DAC核心与自偏置.FRAMEP/N:重置FIFO或用作同步源,在DATACLKP/N上升沿捕获。OSTRP/N:DACCLKP/N的上升边缘所捕获。它用于同步双同步源模式下的分割时钟和FIFO输出。PARITYP/N:奇偶校验位。SCLK:串行接口时钟。SDENB:串口数据的使能信号。SDIO:串口的数据,三个引脚为双向模式,能够输入也能够输出。四个引脚只能够单项输出。SDO:四个引脚只能够单项输出。SYNCP/N :可选的LVDS同步正负输入。RESETB :低电平复位。TXENABLE:传输高电平有效,模拟输出数据传输,寄存器配置3中的sif_txenable设置为1b或将CMOS的引脚拉到高,要禁用模拟输出,请将sif_txenable设置为0b,并将CMOS可启用针拉至低。数字逻辑部分被强制设置为所有0,并忽略任何输入数据。ALARM:报警,默认为高电平。

补充:LVPECL

LVPECL(Low Voltage Positive Emitter Coupled Logic,低电压正发射极耦合逻辑)是一种高速数字逻辑电路标准,通常用于高速信号传输中。它是PECL(Positive Emitter Coupled Logic)的一种低电压版本,相比传统的PECL,LVPECL在工作电压上较低,通常在3.3V或2.5V范围内,而PECL则通常工作在5V电源下。

6.3Feature Description

6.3.1Serial Interface

刚开始第一个字节为指令周期,后面为数据周期。最高位(7bit)为读或者写操作(高电平读,低电平写),剩下7位未地址。

(1)串行接口的写时序分析

在写数据的时候有使能信号SDENB,时钟SCLK,数据的输入SDIO。使能在低电平数据有效,同时在时钟的上升沿进行对数据的采集,在数据结束时是在时钟的下降沿SDIO拉低。下图为写时序图:

(2)串行接口的读时序分析

在读数据时有使能信号SDENB,时钟SCLK,数据的输入输出SDIO,以及SDO数据的输出。如上写数据一样,在数据输出时添加了 SDO,在三引脚配置时(暂时不知道3引脚是什么东东),数据输出实在SDIO中的数据周期输出,SDO高阻态。至于前面的指令周期,是写给DAC3482的控制读指令以及地址。在4引脚配置时,数据从SDO中输出。(后续知道了34引脚是什么东西再回来改) 下图为读时序

6.3.2Data Interface

是通过16位的LVDS总线可以接受16位I和Q数据,支持字宽模式和字节宽模式。在字宽模式下,数据通过16位总线传输;而在字节宽模式下,使用8位总线。模式选择通过config2寄存器中的16bit_in位进行。数据采样由LVDS双倍数据速率(DDR)时钟DATACLK完成,需满足建立和保持时间要求。

6.3.2.1 Word-Wide Format

设置config2寄存器中的16bit_in位为1b来选择字模式。在这种模式下,I和Q通道的16位数据以字宽交错的形式(I0, Q0, I1, Q1...)传输到D[15:0] 16位总线上。数据进入DAC3482的格式如下图所示,其中索引0是数据的最低有效位(LSB),索引15是数据的最高有效位(MSB)。

6.3.2.2Byte-Wide Format

通过在config2寄存器中将16bit_in设置为0b来选择字节范围的格式。在这种模式下,通道I和Q的16位数据以l0[15:8]、I0[7:0]、Q0[15:8]、Q0[7:0]、I-[15:8]的形式在字节范围内交错进入D[7:0] 8位总线。其中索引0是数据LSB,索引15是数据MSB。上述说了在字模式下为LVDS总线用了16位,字节模式下用了8位。

FRAME信号高电平表示将0通道的IQ数据传输,低电平1通道的IQ传输

6.3.3 Input FIFO

DAC3482包括一个2通道,16位宽和8样本深度输入FIFO。

FIFO 的输出时钟由DACCLK产生,当为字模式下时,速率为DACCLK/2*Interpolation。为字节模式下时,速率为DACCLK/Interpolation。

可以使用config9的 fifo_offset【2:0】对FIFO偏移量进行操作。我认为的此偏移量就是写和读指针的距离,写指针在0地址位,读指针在4地址位,在读和写的时钟是同一时钟情况下,他们之间的间隙不变,在不同时钟下间隙不同,可能发生写和读指针在同一个地址位。

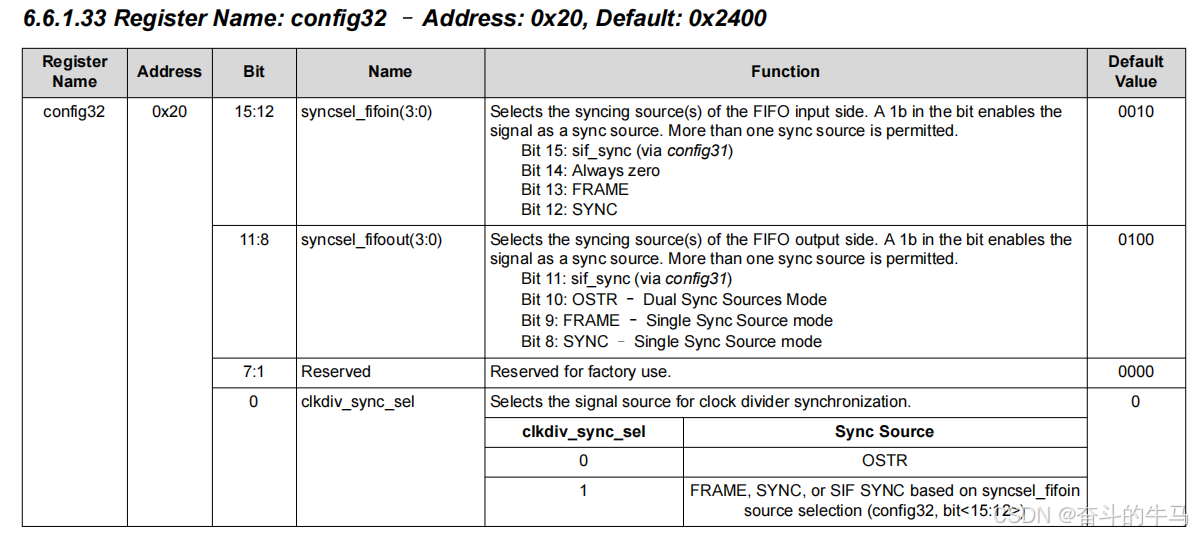

控制FIFO的寄存器